IBIS симулация

IBIS симулация

Jump to TINA Main Page & General Information

IBIS симулация

IBIS (Спецификация на буферната информация за входа / изхода) е метод за осигуряване на информация за моделиране на входно / изходните буфери на интегрални схеми. Хубавото на IBIS моделите е, че те често са достъпни дори за устройства, където пълните модели на устройства не са достъпни от производителите по каквато и да е причина (например, сложност, защита на информацията за собственост и др.).

Едно от най-популярните приложения на IBIS моделите е анализът на целостта на сигналите, включително съвпадение на импеданса и др.

В момента TINA поддържа най-широко използваната версия на IBIS 4.2.

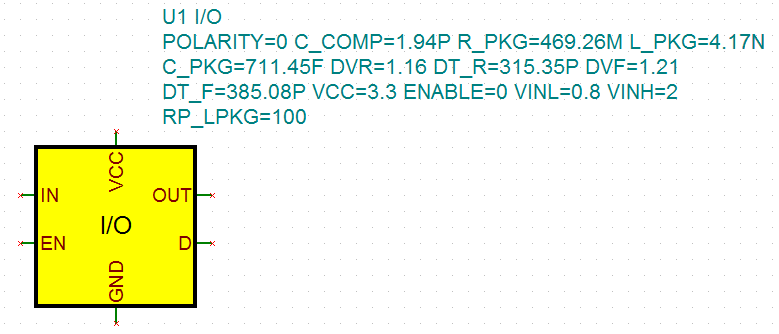

В TINA можете да конвертирате IBIS модели в TINA Spice макроси и след това да ги използват във всички схеми в TINA. Можете също така да попълните опростени модели на цифрови устройства, например MCU с модели IBIS, за да опишете по-добре аналоговото им поведение.

По-долу ще покажем използването на IBIS модели чрез пример за фиксиране на целостта на сигнала между Texas Instruments TMS320C6748 DSP и ADS1259 delta-sigma ADC.

Изберете Файл / Файл за импортиране / IBIS (* .ibs)изберете c6748zce.ibs от TINA справочник >\ Примери \ IBIS.

Ще се покаже следният диалог. В този диалогов прозорец можете да изберете модела за импортиране.

Сега изберете SPI1CLK_GP213 сигнал, модел PBFZP18LL_X50_PI_3P3 (клетката работи при 3.3V без изтегляне или падане) и Тип стойност.

Натиснете OK. Моделът IBIS се преобразува автоматично в a Spice макро.

SPI1CLK_GP213 е главният конфигурационен сериен часовник на TMS320C6748 чипа, за да задейства SPI тактов вход на AD конвертор, Texas Instruments ADS1259.

Изберете Файл / Файл за импортиране / IBIS (* .ibs)изберете ads1259.ibs от TINA справочник >\ Примери \ IBIS.

Ще се покаже следният диалог. В този диалогов прозорец можете да изберете модела за импортиране.

Сега изберете SCK входен сигнал, модел DIN_PD_3 и макс стойност (за диапазона на напрежението на 3.3V DVDD).

Натиснете OK. Моделът IBIS се преобразува автоматично в a Spice макро.

Свържете DSP I / O буфера към входа на ADC с предавателна линия без загуби.

Добавете източник на захранване и генератор на напрежение, за да създадете часовник сигнал от DSP страна. Поставете щифтове за симулация върху сигналните възли.

Ние коригираме параметрите на предавателната линия до няколко инча микроструйни следи, насочени по четирислойна платка. Това произвежда cc. 500ps закъснение и 90 ома характеристика импеданс.

Файл от \ Примери \ IBIS \ Съответствие на импеданса на TMS320C6748.TSC е готова за употреба.

Сега кликнете върху Анализ, Преходен.

DSP предава SPI тактовия сигнал, където несъответствието на импеданса създава отражения. Резултатът показва отраженията, създадени от несъответствията на импеданса в тази симулация на веригата.

На страната на ADC (pin EoTL), напрежението е извън земята и захранващото напрежение, което нарушава абсолютната максимална стойност на цифровия вход.

За да се избегне под и превишаване на края на линията, трябва да се съчетае изходното съпротивление на драйвера с импеданса на следата чрез вмъкване на резистор между изхода и следата.

Нека поставим 100 UM резистор в серия сега с изхода.

Стартирайте отново Transient Analysis и сравнете резултатите, като копирате важните криви една с друга.

Сега можем да видим, че използването на модела IBIS за разбиране и намиране на критичните проблеми със симулацията помогна за решаването на този проблем.