SystemC СИМУЛАЦИЯ

SystemC СИМУЛАЦИЯ

- Verilog-A & AMS симулация

- SystemVerilog симулация

- Симулация на Verilog

- VHDL симулация

- VHDL-AMS симулация

SystemC е друг чудесен инструмент за моделиране на хардуер. Тя включва всички функции на C ++, използвани по целия свят, и библиотека C ++ клас, специално проектирана за системно проектиране. SystemC разполага с безплатна реализация с отворен код и можете да го компилирате в един много ефективен изпълним двоичен код със също така свободен Visual Studio Community C ++ компилатор на Microsoft. В SystemC можете да модел хардуер на по-високо ниво абстракция, отколкото в други HDLs и така за моделиране на някои много сложни хардуер например микроконтролери е по-лесно и ефективно да се използва от други HDLs като VHDL или Verilog.

В v11 и по-късните версии на TINA можете да създавате и използвате компоненти, моделирани в SystemC както в TINA, така и в TINACloud. Следните са изискванията за използване на SystemC с TINA.

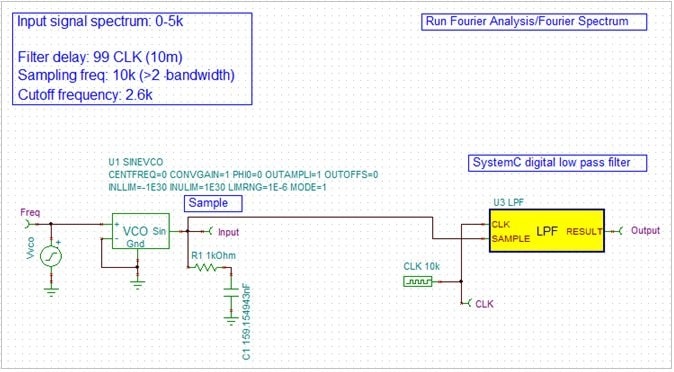

Low-pass filter example

Open the ExamplesSystemCsc lpf.TSC example.

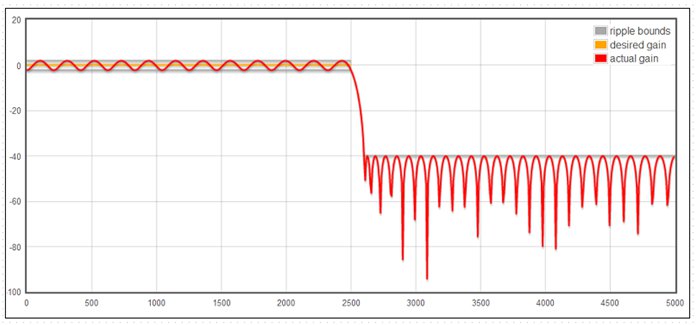

Характеристиките на филтъра и C-кодът са проектирани от безплатния инструмент

http://t-filter.engineerjs.com/

Генерираният C-код е поставен в файла fir.cpp.

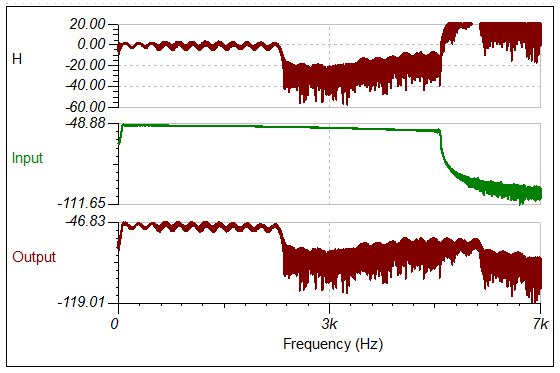

Анализ на изпълнение / анализ на Фурие / спектър на Фурие ...

Натиснете

Натиснете Повече бутон. Тип Изход (и) / вход (а) в реда реда. Напишете H в новото име на функция. Натиснете Създаване на, Натиснете OK. Изберете Преглед / Отделни криви.

Резултатът е следният

Най-важната част от макроса SystemC:

void fir::proc()

{

double u, y;

if (CLK.read() == SC_LOGIC_1) {

sc_logic sc_val;

// CALC

x[0] = SAMPLE; y = 0;

for (int k=0; k < M; k++){

y += b[k]*x[k];

}

// SHIFT

for (int k=M-1; k>=1; k—)

x[k] = x[k-1];

// SET VALUE

RESULT = y;

n++;

}

}

You can find this example in the Examples/Fir folder of the systemc_model.zip.