5. MOSFET integrisani krugovi

MOSFET integrisani krugovi

Kada su MOSFET tranzistori proizvedeni kao dio integriranog kruga, praktična razmatranja zahtijevaju dvije velike promjene u konfiguracijama kruga. Prvo, veliki spojni i premosni kondenzatori koji se koriste u diskretnim pojačalima ne mogu se praktično proizvesti u integriranim krugovima zbog male veličine. Ovu manu zaobilazimo tako što proizvodimo izravna pojačala.

Druga velika promjena je da ne možemo lako proizvesti otpornike koji se koriste kao dio prednaponskih krugova. Umesto toga, koristimo aktivna opterećenja i strujne izvore sastavljene od MOS tranzistora.

Integrisana kola koriste i NMOS i PMOS sklopove. CMOS je češći u digitalnim krugovima, dok se NMOS obično koristi za IC-ove veće gustoće (tj. Više funkcija po čipu).

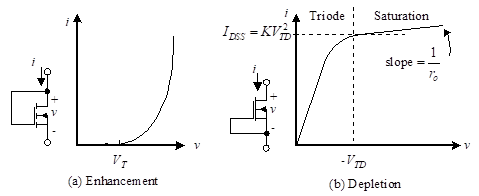

Simuliranje aktivnih opterećenja koristi prednost nagiba MOS karakterističnih krivulja. Na slici 23 prikazana su dva tipa aktivnih opterećenja. Na slici 23 (a) prikazujemo NMOS pojačalo, dok 23 (b) pokazuje opterećenje osiromašenog NMOS-a. Na slici su prikazane i relevantne karakteristične krivulje.

Slika 23 - Aktivna opterećenja

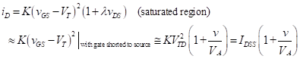

Za NMOS pojačanje opterećenje, odnos između napona i struje je dao

![]()

(29)

Ekvivalentna otpornost ove konfiguracije je 1 /gm, gde je vrednost provodljivosti ona koja se primenjuje na tački pristranosti.

Opterećenje osiromašenim NMOS-om ima ekvivalentni otpor koji se određuje nagibom karakteristike danom slijedećom jednadžbom

(30)

5.1 Biasing MOSFET integrisanih kola

Sada kada imamo dvije tehnike za simulaciju aktivnih opterećenja, možemo riješiti problem pristrasnosti. Mi koristimo aktivno opterećenje umesto otpora opterećenja u bilo kojoj konfiguraciji kola. Da bismo prikazali tehniku za analizu ovih, razmotrimo NMOS pojačalo koristeći opterećenje pojačanja, kao što je prikazano na slici 24.

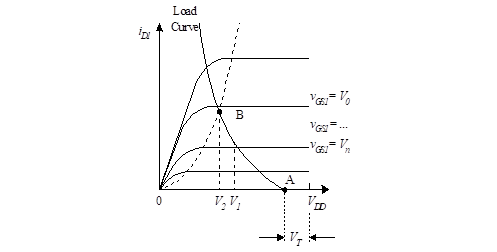

Tranzistor je označen Q2 zamenjuje RD naših ranijih sklopova. Da bismo odredili mirovanje radne točke, koristimo iste tehnike kao i u Odjeljku 4, „Konfiguracije FET pojačala i pristranost“, zamjenjujući samo grafičku karakteristiku pojačanja opterećenja za liniju opterećenja otpornika. Odnosno, moramo pronaći simultano rješenje karakteristika FET tranzistora s jednadžbom za teretni vod. To možemo učiniti grafički kao što je prikazano na slici 25.

Parametarske krivulje su karakteristične krivulje za pojačivački tranzistor, Q1. Karakteristika napona i struje aktivnog opterećenja, Q2 su one na slici 23. Izlazni napon, vnapolje, je razlika između VDD i napon na aktivnom opterećenju. Struja u aktivnom opterećenju je ista kao i struja odvoda u pojačavajućem tranzistoru. Stoga konstruiramo liniju opterećenja uzimajući pomaknutu zrcalnu sliku karakteristike slike 23. Radna tačka je presek ove krive sa odgovarajućom karakterističnom krivom tranzistora. Moramo pronaći napon od vrata do izvora da bismo znali koju krivu tranzistora treba izabrati. Kao što ćemo vidjeti, ulazni napon se često zamjenjuje aktivnim izvorom struje.

Slika 25 - Grafičko rješenje za Q-točku

Sada kada znamo kako da simuliramo aktivno opterećenje, skrećemo pažnju na generisanje referentne struje koja će se koristiti kao dio kola za ulazne pristranosti. Ovi strujni izvori se koriste na isti način na koji smo ih koristili za BJT pojačavanje pojačala.

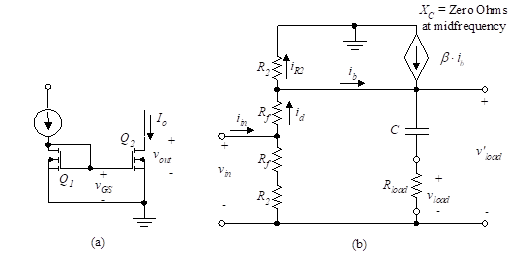

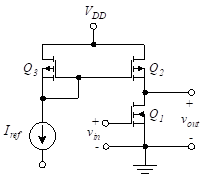

Slika 26 - Trenutno ogledalo

Mi analiziramo MOSFET current mirror. Aktuelno ogledalo je prikazano na slici 26. Pretpostavlja se da su dva tranzistora savršeno usklađena. Izlazna struja je odvodna struja Q2i referentni strujni pogoni Q1. Ako se tranzistori savršeno podudaraju, izlazna struja će biti potpuno jednaka referentnoj struji. To je istina jer su tranzistori povezani paralelno. Baš kao što je bio slučaj sa BJT trenutnim zrcalom, referentna struja se može generirati primjenom referentnog napona na referentnom otporu, kao što je prikazano na slici 26 (b).

Postavljanje različitih podkrugova zajedno (tj. Aktivno opterećenje i referentna struja) rezultira CMOS pojačalom na slici 27.

Dobitak ovog pojačala daje se pomoću

![]()

(31)

Slika 27 - CMOS pojačalo

5.2 Body Effect

Naša rasprava o odjeljku „2. Metal-oksidni poluprovodnik FET (MOSFET) ”odnosi se na podlogu (ili tijelo) MOSFET-a. Ovaj supstrat igra važnu ulogu u uspostavljanju kanala. U radu diskretnih MOSFET-ova, tijelo je često povezano s izvorom napajanja. U takvim slučajevima podloga nema izravan utjecaj na rad uređaja, a primjenjuju se krivulje razvijene ranije u ovom poglavlju.

Situacija se menja kada se MOSFET-i izrađuju kao deo integrisanih kola. U takvim slučajevima, podloga svakog pojedinačnog tranzistora nije izolirana od drugih podloga. Zaista, supstrat se često dijeli između svih MOSFET-ova na čipu. U PMOS IC-u, zajednički supstrat bi bio povezan sa najpozitivnijim terminalnim izvorom, dok je u NMOS-u povezan sa zemljom (ili sa negativnim napajanjem ako je prisutan). Time se uspostavlja obrnuta pristrasnost između izvora i tijela svakog tranzistora. Efekat ove obrnute pristrasnosti je promjena operativnih karakteristika. Na primjer, u n-kanalni uređaj, efektivno podiže prag (VT). Iznos kojim se prag mijenja ovisi o fizičkim parametrima i konstrukciji uređaja. Za NMOS, ova promjena se može aproksimirati sa

![]()

(32)

U jednačini (32), γ je parametar uređaja koji varira između 0.3 i 1 (V)-1 / 2). VSB je napon od izvora do tijela, a je Fermijev potencijal. Ovo je svojstvo materijala, a tipična vrijednost je 0.3 V za silicij.

STRUJA - 5. MOSFET integrirani krugovi

STRUJA - 5. MOSFET integrirani krugovi PREVIOUS- 4. Konfiguracije FET pojačala i pomicanje

PREVIOUS- 4. Konfiguracije FET pojačala i pomicanje