Simulació IBIS

Simulació IBIS

Jump to TINA Main Page & General Information

Simulació IBIS

IBIS (especificació d'informació del buffer d'entrada / sortida) és un mètode per proporcionar informació de modelització sobre els buffers d’entrada / sortida dels circuits integrats. El bo dels models IBIS és que sovint estan disponibles fins i tot per a dispositius on els fabricants no disposen de models complets de dispositius per qualsevol motiu (per exemple, complexitat, protecció d’informació propietària, etc.).

Un dels usos més populars dels models IBIS és l'anàlisi de la integritat de senyals, inclosa la correspondència d’impedàncies i molt més.

Actualment, TINA suporta la versió més àmpliament utilitzada d’IBIS 4.2.

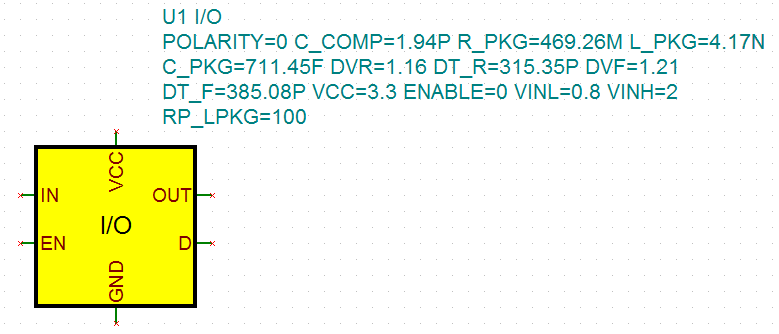

A TINA, podeu convertir els models IBIS a TINA Spice macros i després les utilitzeu en qualsevol circuit de TINA. També podeu completar models de dispositius digitals simplificats (per exemple, MCUs amb models IBIS) per descriure millor el seu comportament analògic.

A continuació, es mostrarà l’ús de models IBIS a través d’un exemple de fixació de la integritat del senyal entre un instrument Texas TMS320C6748 DSP i un ADC ADS1259 delta-sigma.

seleccionar Fitxer / Importació / Fitxer IBIS (* .ibs), Seleccioneu c6748zce.ibs des de Directori TINA >Exemples: IBIS.

Es mostrarà el següent diàleg. En aquest diàleg, podeu seleccionar el model que voleu importar.

ara seleccioneu SPI1CLK_GP213 senyal, model PBFZP18LL_X50_PI_3P3 (cel·la operada a 3.3V sense arrencada o desplaçament) i Typ valor establert.

Premeu OK. El model IBIS es converteix automàticament en un Spice macro.

SPI1CLK_GP213 és la configuració principal del senyal de rellotge de sèrie del xip TMS320C6748 per conduir l'entrada del rellotge SPI d'un convertidor AD, Texas Instruments ADS1259.

seleccionar Fitxer / Importació / Fitxer IBIS (* .ibs), Seleccioneu ads1259.ibs des de Directori TINA >Exemples: IBIS.

Es mostrarà el següent diàleg. En aquest diàleg, podeu seleccionar el model que voleu importar.

ara seleccioneu SCK senyal d’entrada, model DIN_PD_3 i Max valor (per al rang de voltatge de DVDN de 3.3V).

Premeu OK. El model IBIS es converteix automàticament en un Spice macro.

Connecteu el buffer d'E / S DSP a l'entrada de l’ADC amb una línia de transmissió sense pèrdues.

Afegiu la font d’alimentació i el generador de tensió per crear el senyal de rellotge del costat DSP. Col·loqueu les agulles de tensió per a la simulació sobre els nodes de senyal.

Ajustem els paràmetres de la línia de transmissió a uns pocs centímetres de traça de microstrip encaminats a una PCB de quatre capes. Això produeix cc. Retard 500ps i impedància característica 90 Ohms.

Fitxer des de \ Exemples \ IBIS \ Concordança d'impedància de TMS320C6748.TSC està a punt per ser utilitzat.

Ara, feu clic a Anàlisi, transitori.

El DSP transmet el senyal de rellotge SPI on la discrepància d'impedància crea reflexos. El resultat mostra les reflexions creades per la desajustament de la impedància en aquesta simulació de circuit.

Al costat ADC (pin EoTL), la tensió és més enllà del sòl i la tensió d'alimentació, que viola la qualificació màxima absoluta de l'entrada digital.

Per evitar baixades i excedències a l'extrem de la línia és que coincideixi amb la impedància de sortida del controlador a la impedància de traça inserint una resistència entre la sortida i la traça.

Posem una resistència 100 Ω en sèrie ara amb la sortida.

Executeu l'anàlisi de transitoris de nou i compareu els resultats copiant les corbes importants entre si.

Ara, podem veure que l'ús del model IBIS per entendre i trobar els problemes crítics amb la simulació va ajudar a resoldre aquest problema.