9. Analýza zesilovače FET

Analýza zesilovače FET

9.1 Zesilovač CS (a zdrojový rezistor)

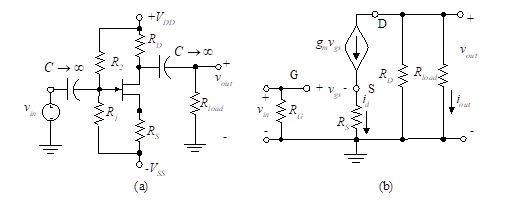

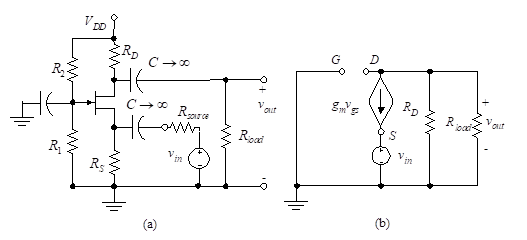

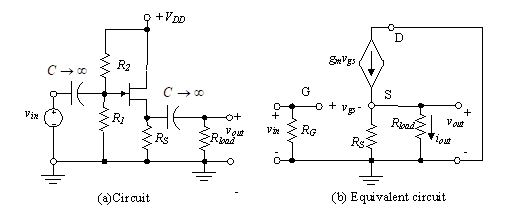

Obrázek 33 - Zesilovač CS se zdrojovým rezistorem

Obrázek 33 (a) ukazuje CS zesilovač se zdrojovým odporem. ac ekvivalentní obvod je na obr. 33 (b). Předpokládáme ro je velká ve srovnání s, takže ji lze zanedbávat. Pokud je mezi zdrojem a zemí (tj. Zesilovačem CS) přítomen kondenzátor, potřebujeme jednoduše nastavit RS rovna nule ac rovnice. Děláme to na konci tohoto odvození.

V části (b) na obrázku 33, RG je paralelní kombinace R1 a R2 a VGG je ekvivalentní napětí Theveninova obvodu předpětí:

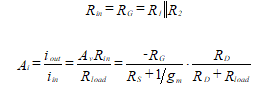

(41)

(41)

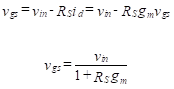

Analyzovat ac ekvivalentní obvod, napíšeme KVL rovnici kolem hradlového obvodu.

(42)

(42)

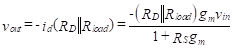

Výstupní napětí, vout, darováno

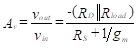

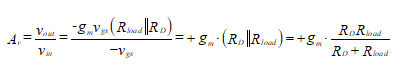

Zisk napětí, Av, je nyní nalezen.

(43)

(43)

Je-li odpor zdroje, RS, je přemostěn kondenzátorem RS = 0 a zesílení napětí se zvyšuje na

![]() (44)

(44)

To je obvykle velké záporné číslo.

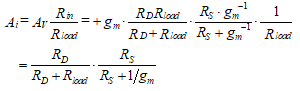

Vstupní odpor a proudový zisk jsou dány

(45)

(45)

9.2 Zesilovač CG

Obrázek 37 (a) ukazuje jednostupňový zesilovač společných hradel a obrázek 6.37 (b) ukazuje jeho ac ekvivalent. Opět jsme opomněli ro za předpokladu, že je velká ve srovnání s paralelní kombinací RD s Rzatížení.

Obrázek 37 - CG zesilovač

Z obr. 37 (b) smyčka vlevo je dáno napětím od zdroje ke zdroji

![]() (46)

(46)

Proud prochází RS is

(47)

(47)

tak je (vstupní) odpor viditelný zdrojem

![]() (48)

(48)

To by mělo být porovnáno s rovnicí (45) pro CS zesilovač. Vidíme, že pokud je odpor hradla vysoký, vstupní odpor zesilovače common-source může být mnohem větší než u zesilovače common-gate. Ve skutečnosti je počet aplikací zesilovače CG omezen v důsledku nízké vstupní impedance.

Zisk napětí je dán

(49)

(49)

Srovnáním s rovnicí (44) vidíme, že zesílení napětí pro CS zesilovač s unbypassed odporem ve zdrojovém obvodu je stejné jako zesilovač CG zesilovače s výjimkou CG zesilovače, který neposune fázi.

Výstupní odpor je jednoduše dán RD (vložte testovací proud a změřte napětí při nastavování vin na nulu).

Proudový zisk zesilovače CG je

(50)

(50)

9.3 Zesilovač CD (SF)

Obrázek 39 (a) ukazuje jednofázový zesilovač zdroje (SF) a obrázek 39 (b) ukazuje jeho ac ekvivalent. Jako u každé konfigurace, kterou jsme analyzovali, vynecháme velký odpor, ro za předpokladu, že je mnohem větší než paralelní kombinace RS s Rzatížení.

Obrázek 39 - CD zesilovač

Vstupní odpor je jednoduše Rin = RG. Zapisujeme rovnici KVL kolem smyčky typu gate-to-source

![]() (51)

(51)

z nichž získáme

![]() (52)

(52)

Výstupní napětí je

![]() (53)

(53)

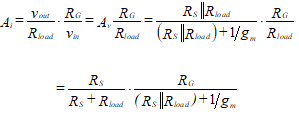

Zesílení napětí je poměr výstupu k vstupnímu napětí.

![]() (54)

(54)

Všimněte si, že toto zesílení napětí je menší než jednota a přibližuje se k jednomu jako paralelní kombinace RS s Rzatížení zvyšuje.

Nyní zjistíme aktuální zisk. Výstupní proud je poměr výstupního napětí k zátěžovému odporu. Vstupní proud je vstupní napětí děleno RG. Zisk je tedy dán

(55)

(55)

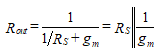

Výstupní odpor lze nalézt nahrazením zátěžového odporu zkušebním napětím, vtesta poté nalezení výsledného proudu, itest. Proud poháněný tímto testovacím zdrojem je nalezen z rovnice uzlu u zdroje.

![]() (56)

(56)

Napětí brány na zdroj je jednoduše -vtest protože předpokládáme, že vstupní napětí je nulové. Proto je výstupní odpor

(57)

(57)

AKTUÁLNÍ - 9. Analýza zesilovače FET

AKTUÁLNÍ - 9. Analýza zesilovače FET PŘEDCHOZÍ- 8. Zesilovače FET - kanonické konfigurace

PŘEDCHOZÍ- 8. Zesilovače FET - kanonické konfigurace