SystemC SIMULATSIOON

SystemC SIMULATSIOON

- Verilog-A ja AMS-i simulatsioon

- SystemVerilogi simulatsioon

- Verilog Simulation

- VHDL simulatsioon

- VHDL-AMS simulatsioon

SystemC on teine suurepärane vahend riistvara modelleerimiseks. See sisaldab kõiki C ++ funktsioone, mida kasutatakse kogu maailmas, ja C ++ klassi raamatukogu, mis on spetsiaalselt loodud süsteemi projekteerimiseks. SystemC-l on avatud lähtekoodiga vaba rakendus ja saate selle kompileerida väga tõhusaks käivitatavaks binaarseks koodiks, mis sisaldab ka tasuta Visual Studio ühenduse C ++ kompilaatorit. Süsteemis SystemC saate modelleerida riistvara suurema abstraktsioonitasemega kui teistes HDL-ides ja seega on väga keerulise riistvara, nt mikrokontrollerite modelleerimiseks lihtsam ja tõhusam kasutada kui teised HDL-id nagu VHDL või Verilog.

V11is ja TINA hilisemates versioonides saate luua ja kasutada ka süsteemis SystemC modelleeritud komponente nii TINA kui ka TINACloudis. Järgnevalt on esitatud nõuded, et kasutada Systemina TINAga.

Low-pass filter example

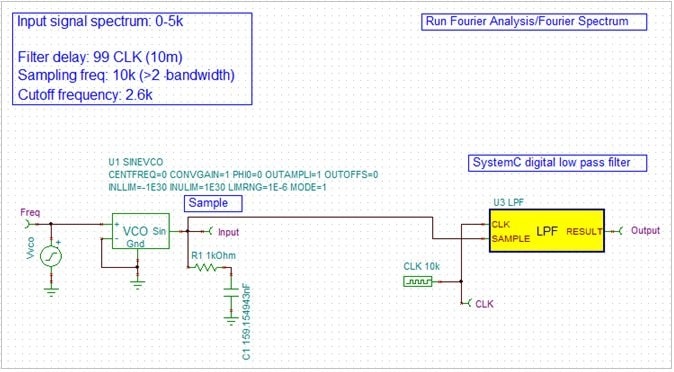

Open the ExamplesSystemCsc lpf.TSC example.

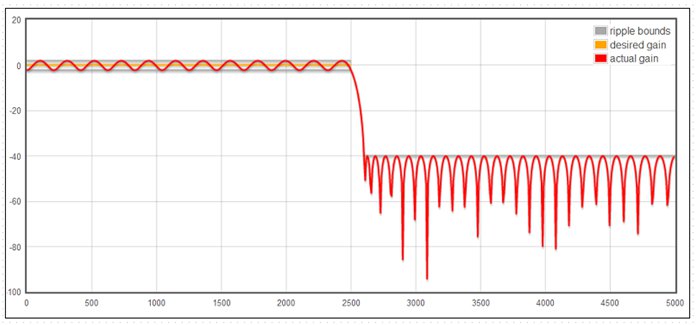

Filtri omadused ja C-kood on kujundatud tasuta tööriista juures

http://t-filter.engineerjs.com/

Genereeritud C-kood paigutati fir.cpp-faili.

Käivita analüüs / Fourieri analüüs / Fourier Spectrum…

Vajutage

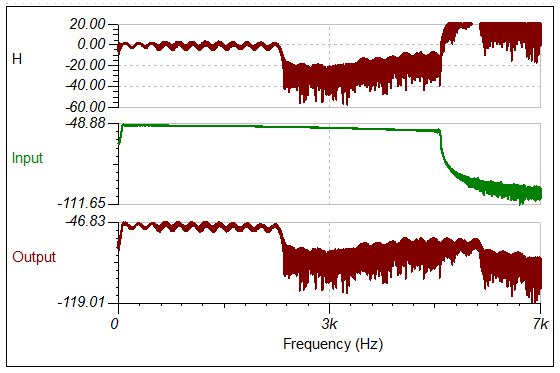

Vajutage rohkem nuppu. Tüüp Väljund (id) / sisend (id) liinirea redigeerimisel. Tippige uus funktsiooninimi H. Vajutage Looma. Vajuta OK. Valima Vaata / Eraldi kõverad.

Tulemuseks on järgmine

SystemC makro kõige olulisem osa:

void fir::proc()

{

double u, y;

if (CLK.read() == SC_LOGIC_1) {

sc_logic sc_val;

// CALC

x[0] = SAMPLE; y = 0;

for (int k=0; k < M; k++){

y += b[k]*x[k];

}

// SHIFT

for (int k=M-1; k>=1; k—)

x[k] = x[k-1];

// SET VALUE

RESULT = y;

n++;

}

}

You can find this example in the Examples/Fir folder of the systemc_model.zip.