SystemC SIMULATION

SystemC SIMULATION

- Verilog-A & AMS մոդելավորում

- SystemVerilog մոդելավորում

- Verilog մոդելավորում

- VHDL մոդելավորում

- VHDL-AMS մոդելավորում

SystemC- ն եւս մեկ հիանալի գործիք է սարքավորման մոդելավորման համար: Այն ներառում է C ++- ի բոլոր հատկանիշները, որոնք օգտագործվում են ամբողջ աշխարհում եւ C ++ դասի գրադարան, որը հատուկ նախագծված է համակարգի նախագծման համար: SystemC- ն ունի բաց կոդով անվճար իրականացումը, եւ այն կարող եք կազմել այն շատ արդյունավետ գործադիր երկքաղաքական կոդը, ինչպես նաեւ Microsoft- ի Visual Studio C ++ մշակողը: SystemC- ում դուք կարող եք մոդելավորել ապարատը ավելի բարձր մակարդակում, քան այլ HDL- ներում եւ այդպիսով որոշ չափով բարդ համակարգերի մոդելավորման համար, օրինակ, microcontrollers- ը ավելի հեշտ եւ արդյունավետ է, քան VHDL- ի կամ Verilog- ի նման այլ HDL- ները:

V11- ում եւ TINA- ի հետագա տարբերակներում դուք կարող եք նաեւ ստեղծել եւ օգտագործել SystemC- ում մոդելավորված բաղադրիչները `TINA- ում եւ TINACloud- ում: Հետեւյալները SystemCA- ի հետ TINA- ի օգտագործման պահանջներն են:

Low-pass filter example

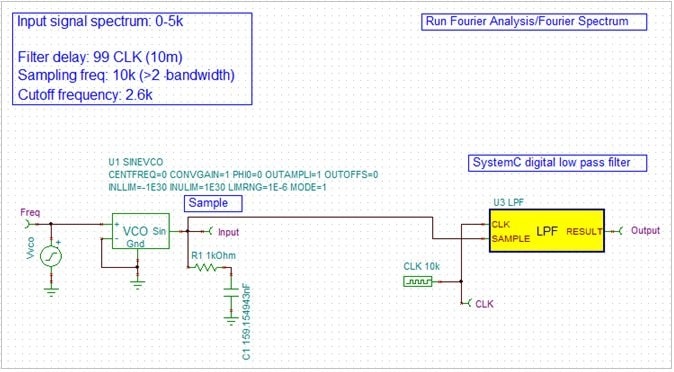

Open the ExamplesSystemCsc lpf.TSC example.

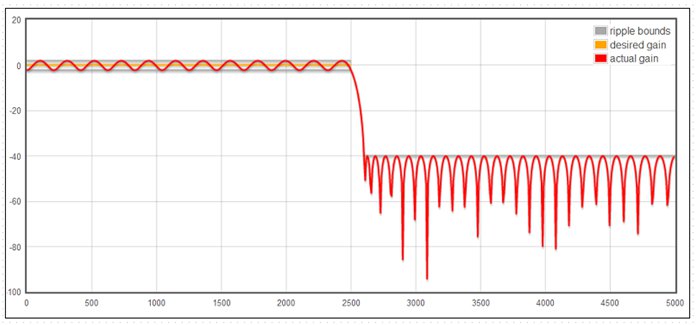

Ֆիլտրի բնութագրերը եւ C- կոդերը նախատեսված են անվճար գործիքի կողմից

http://t-filter.engineerjs.com/

Գեներացված C- կոդը տեղադրվել է fir.cpp ֆայլում:

Գործարկել վերլուծություն / Fourier վերլուծություն / Fourier Spectrum ...

Սեղմեք

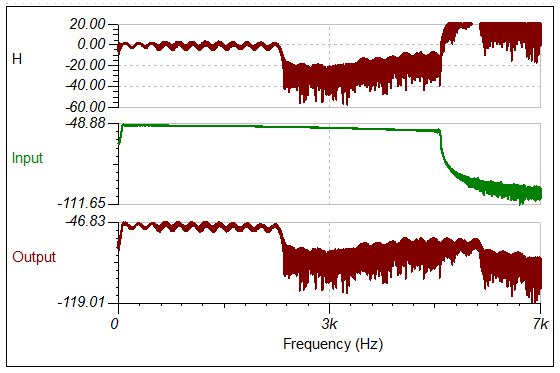

Սեղմեք Ավելին կոճակը: Տիպ Արդյունք (ներ) / մուտք (ներ) գծի խմբագրում: Նոր գործառույթի անվանման մեջ մուտքագրեք H: Մամուլ Ստեղծել. Մամուլ OK: Ընտրել Դիտել / առանձնացրեք կորերը.

Արդյունքը հետեւյալն է

SystemC մակրո ամենակարեւոր մասը `

void fir::proc()

{

double u, y;

if (CLK.read() == SC_LOGIC_1) {

sc_logic sc_val;

// CALC

x[0] = SAMPLE; y = 0;

for (int k=0; k < M; k++){

y += b[k]*x[k];

}

// SHIFT

for (int k=M-1; k>=1; k—)

x[k] = x[k-1];

// SET VALUE

RESULT = y;

n++;

}

}

You can find this example in the Examples/Fir folder of the systemc_model.zip.