9. Analisi dell'amplificatore FET

Analisi dell'amplificatore FET

9.1 L'amplificatore CS (e resistore sorgente)

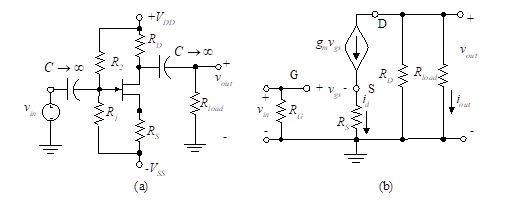

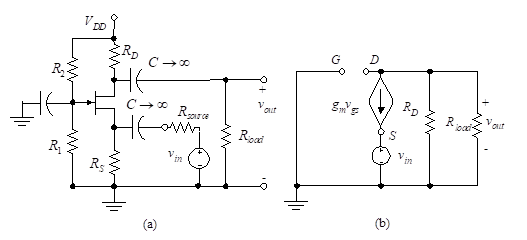

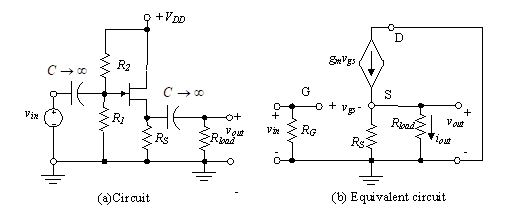

Figura 33 - L'amplificatore CS con resistenza sorgente

La figura 33 (a) mostra l'amplificatore CS con resistenza di origine. Il ac il circuito equivalente è in Figura 33 (b). Assumiamo ro è grande rispetto a, quindi può essere trascurato. Se è presente un condensatore tra la sorgente e la terra (cioè l'amplificatore CS), è sufficiente impostare RS uguale a zero nel seguito ac equazioni. Lo facciamo alla conclusione di questa derivazione.

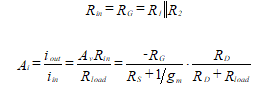

Nella parte (b) della figura 33, RG è la combinazione parallela di R1 ed R2 ed VGG è la tensione equivalente di Thevenin del circuito di polarizzazione:

(41)

(41)

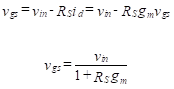

Per analizzare il ac circuito equivalente, scriviamo un'equazione KVL attorno al circuito di gate.

(42)

(42)

La tensione di uscita, vsu, è dato da

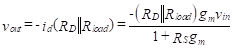

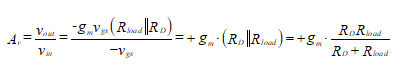

Il guadagno di tensione, Av, è ora trovato.

(43)

(43)

Se la resistenza fonte, RS, viene bypassato da un condensatore, lo lasciamo RS = 0 e il guadagno di tensione aumenta a

![]() (44)

(44)

Questo è in genere un numero negativo elevato.

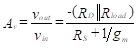

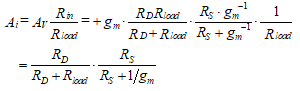

La resistenza di ingresso e il guadagno di corrente sono dati da

(45)

(45)

9.2 L'amplificatore CG

La figura 37 (a) mostra l'amplificatore a gate comune a stadio singolo e la Figura 6.37 (b) mostra il suo ac equivalente. Ancora una volta abbiamo trascurato ro partendo dal presupposto che è grande rispetto alla combinazione parallela di RD con Rcaricare.

Figura 37 - Amplificatore CG

Da Figura 37 (b) loop più a sinistra, la tensione gate-source è data da

![]() (46)

(46)

La corrente attraverso RS is

(47)

(47)

quindi la resistenza (di input) vista dalla sorgente è

![]() (48)

(48)

Questo dovrebbe essere confrontato con Equation (45) per l'amplificatore CS. Vediamo che se la resistenza del gate è elevata, la resistenza di ingresso dell'amplificatore common-source può essere molto più grande di quella dell'amplificatore common-gate. In effetti, il numero di applicazioni dell'amplificatore CG è limitato a causa della bassa impedenza di ingresso.

Il guadagno di tensione è dato da

(49)

(49)

Confrontandolo con Equation (44), vediamo che il guadagno di tensione per l'amplificatore CS con una resistenza unbypassed nel circuito sorgente è lo stesso di quello dell'amplificatore CG, tranne che l'amplificatore CG non sposta la fase.

La resistenza di uscita è semplicemente data da RD (inserire una corrente di prova e misurare la tensione durante l'impostazione vin a zero).

Il guadagno di corrente dell'amplificatore CG è

(50)

(50)

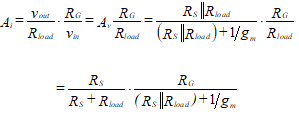

9.3 L'amplificatore CD (SF)

La figura 39 (a) mostra l'amplificatore follower source follower (SF) single-stage source e la figura 39 (b) mostra il suo ac equivalente. Come con ogni configurazione che abbiamo analizzato, omettiamo la grande resistenza, ro sotto l'ipotesi è molto più grande della combinazione parallela di RS con Rcaricare.

Figura 39 - L'amplificatore CD

La resistenza di ingresso è semplicemente Rin = RG. Scrivendo un'equazione KVL attorno al loop gate-to-source, abbiamo

![]() (51)

(51)

da cui otteniamo

![]() (52)

(52)

La tensione di uscita è

![]() (53)

(53)

Il guadagno di tensione è il rapporto tra l'uscita e la tensione di ingresso.

![]() (54)

(54)

Si noti che questo guadagno di tensione è inferiore all'unità e si avvicina a uno come la combinazione parallela di RS con Rcaricare aumenta.

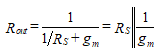

Ora troviamo il guadagno attuale. La corrente di uscita è il rapporto tra la tensione di uscita e la resistenza di carico. La corrente di ingresso è la tensione di ingresso divisa per RG. Il guadagno è quindi dato da

(55)

(55)

La resistenza di uscita può essere trovata sostituendo il resistore di carico con una tensione di prova, vteste quindi trovare la corrente risultante, itest. La corrente pilotata da questa sorgente di test si trova da un'equazione di nodo all'origine.

![]() (56)

(56)

La tensione da porta a fonte è semplicemente -vtest poiché supponiamo che la tensione di ingresso sia zero. Pertanto, la resistenza di uscita è

(57)

(57)

CORRENTE - 9. Analisi dell'amplificatore FET

CORRENTE - 9. Analisi dell'amplificatore FET PRECEDENTE- 8. Amplificatori FET - Configurazioni canoniche

PRECEDENTE- 8. Amplificatori FET - Configurazioni canoniche