5. MOSFET интегралдық схемалары

MOSFET интегралдық схемалары

MOSFET транзисторлары интегралды схеманың бөлігі ретінде дайындалған кезде, практикалық ойлар схема конфигурацияларында екі маңызды өзгерістерді талап етеді. Біріншіден, дискретті күшейткіштерде қолданылатын үлкен байланысы мен айнымалы конденсаторлар кішігірім мөлшерде интегралды схемаларда дайындала алмайды. Біз бұл кемшіліктерді тікелей біріктірілген күшейткіштер жасап шығарамыз.

Екінші маңызды өзгеріс - біз қиғаштық схеманың бөлігі ретінде қолданылатын резисторларды оңай шығара алмаймыз. Оның орнына біз белсенді жүктемелер мен MOS транзисторлардан тұратын ток көздерін пайдаланамыз.

Интегралды схемалар NMOS және PMOS схемаларын пайдаланады. CMOS цифрлық схемада кеңінен таралған, ал NMOS әдетте жоғары тығыздықты IC үшін қолданылады (яғни чипке көп функциялар).

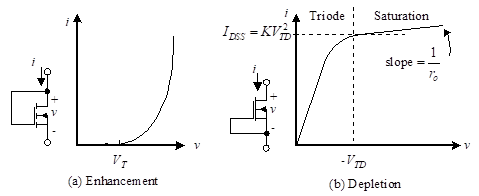

Белсенді жүктемелерді модельдеу MOS тән қисық сызықтарының көлбеуін пайдаланады. Сурет 23 белсенді жүктің екі түрін көрсетеді. 23 (a) суретте NMOS жақсарту жүктемесін көрсетеміз, ал 23 (b) NMOS жұмсарту жүктемесін көрсетеді. Сондай-ақ суретте көрсетілгендей, тиісті сипаттамалы қисықтар.

Сурет 23 - Белсенді жүктемелер

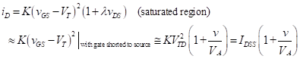

NMOS жақсарту жүктемесі үшін кернеу мен ток арасындағы байланыс беріледі

![]()

(29)

Бұл конфигурацияның баламалы кедергісі 1 /gm, онда трансферменттің мәні ол қиғаш нүктесінде қолданылады.

NMOS тозу жүктемесі төмендегі теңдеу арқылы берілген сипаттаманың беткі жағында анықталған балама қарсылыққа ие

(30)

5.1 MOSFET интегралды схемаларын сәйкестендіру

Енді бізде белсенді жүктемелерді модельдеуге арналған екі әдіс бар, біз бұл мәселені шешуге болады. Жүктеме қарсылық орнына белсенді жүктемені кез-келген схема конфигурациясында қолданамыз. Оларды талдауға арналған техниканы көрсету үшін NMOS күшейткішін 24 суретте көрсетілгендей жақсарту жүктемесі арқылы қарастырайық.

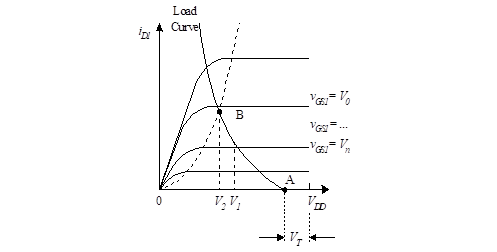

Транзистор таңбаланған Q2 ауыстырады RD біздің бұрынғы схемаларымыз. Тыныш жұмыс нүктесін анықтау үшін біз резистордың жүктеме сызығы үшін тек күшейту жүктемесінің графикалық сипаттамасын алмастыратын «FET күшейткіштің конфигурациясы және бейімделуі» 4-бөліміндегідей тәсілдерді қолданамыз. Яғни, біз FET транзисторлық сипаттамаларын жүктеме сызығының теңдеуімен бір уақытта шешуді табуымыз керек. Біз мұны 25-суретте көрсетілгендей графикалық түрде жасай аламыз.

Параметрлік қисықтар - күшейетін транзистордың қисық сызықтары, Q1. Белсенді жүктеме кернеуінің ток сипаттамасы, Q2 23 суретте көрсетілген. Шығу кернеуі, vсыртында, арасындағы айырмашылық VDD және белсенді жүктеме бойынша кернеу. Белсенді жүктемедегі ток күшейткіш транзистордағы ағынды ток сияқты. Сондықтан 23 фигурасының сипаттамасының жылжытылған айна бейнесін алып, жүктеу сызығын саламыз. Жұмыс нүктесі - бұл қисықтың тиісті транзисторлық қисық сызықпен қиылысы. Қандай транзисторлы қисықты таңдауға болатындығын білу үшін қақпаның кернеуін табу қажет. Келесі көретініміздей, кіріс кернеу жиі белсенді ток көзімен ауыстырылады.

Сурет 25 - Q-нүктесінің графикалық шешімі

Енді белсенді жүктемені қалай модельдеу керектігін білеміз, біз кіріспе схеманың бір бөлігі ретінде қолданылатын анықтамалық ток генерациясына назар аударамыз. Бұл ағымдық көздер BJT күшейткішіне бейімделу үшін пайдаланылғандай пайдаланылады.

Сурет 26 - Айна

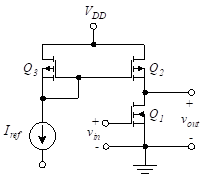

Біз MOSFET-ті талдаймыз ағымдағы айна. Ағымдағы айна 26 суретте көрсетілген. Екі транзистордың мінсіз сәйкес келуі деп есептеледі. Шығу тогы - ағызу ток Q2, және тірек ток дискілері Q1. Егер транзисторлар толық сәйкес келсе, шығыс тогы анықтамалық токқа толық тең болады. Бұл дұрыс, өйткені транзисторлар параллель қосылған. BJT ток айнасында болған сияқты, эталондық ток 26 (b) суретте көрсетілгендей эталондық кедергіге анықтамалық кернеу қолдану арқылы жасалуы мүмкін.

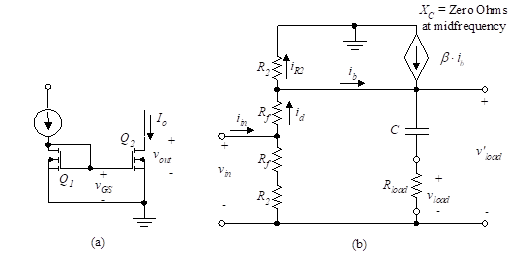

Әр түрлі ішкі бөліктерді (яғни, белсенді жүктеме мен анықтамалық ток) бірге орналастыру X X X X NUMX CMOS күшейткішіне әкеледі.

Бұл күшейткіштің пайдасы берілген

![]()

(31)

Сурет 27 - CMOS күшейткіші

5.2 дене әсері

Біздің бөлім «2. Металл-оксидті жартылай өткізгіш FET (MOSFET) »MOSFET субстратына (немесе корпусына) қатысты. Бұл субстрат арнаны құруда маңызды рөл атқарады. Дискретті MOSFET-тер жұмысында дене көбінесе қуат көзіне қосылады. Мұндай жағдайларда субстрат құрылғының жұмысына тікелей әсер етпейді және осы тарауда бұрын жасалған қисықтар қолданылады.

MOSFET интегралды схемалар бөлігі ретінде дайындалған кезде жағдай өзгереді. Мұндай жағдайларда әр транзистордың субстраты басқа субстраттардан оқшауланбайды. Шынында да, субстрат көбіне чиптегі барлық MOSFET-лар арасында бөлінеді. PMOS IC-де ортақ субстрат ең оң көздер терминалына қосылады, ал НМОС-да ол жермен байланысқан (немесе егер ол бар болса, теріс). Бұл әр транзистордың көзі мен денесі арасында кері бағытта орнатады. Бұл кері әсердің әсері жұмыс сипаттамаларын өзгерту болып табылады. Мысалы, nарналы құрылғы, ол шектіVT). Шекті мәні өзгеретін сома физикалық параметрлерге және құрылғы құрылысына байланысты. NMOS үшін бұл өзгерісті жақындатуға болады

![]()

(32)

Теңдеуде (32) γ - 0.3 және 1 (V-1 / 2). VSB денеден көзге дейінгі кернеу, және Ферманың потенциалы. Бұл материалдың сипаты және кремний үшін 0.3 V типтік мәні.

Ағымдағы - 5. MOSFET интегралды схемалары

Ағымдағы - 5. MOSFET интегралды схемалары PREVIOUS- 4. ФИТ күшейткіштің конфигурациясы және схемасы

PREVIOUS- 4. ФИТ күшейткіштің конфигурациясы және схемасы