11. 다른 장치들

다른 장치들

일반적인 2 단자 및 3 단자 장치의 파생물 인 다른 장치가이 절에 나와 있습니다.

11.1 메탈 반도체 배리어 접합 트랜지스터

금속 반도체 장벽 접합 트랜지스터 (MESFET)는 쇼트 키 다이오드와 마찬가지로 접합이 금속 반도체 장벽이라는 점을 제외하면 FET와 유사하다. 실리콘 (Si) 또는 갈륨 비소 (GaAs)로 만들어진 FET는 확산 또는 이온 주입 게이트로 구성됩니다. 그러나, 쇼트 키 배리어 금속 게이트를 사용하는 것이 채널이 n-유형 및 짧은 채널 너비가 필요합니다. 갈륨 비소 (GaAs)는 작업하기 어렵지만 전자가 Si보다 GaAs에서 더 빠르게 이동하기 때문에 고주파 응용 분야에서 유용한 우수한 쇼트 키 장벽을 만듭니다. MESFET에서 GaA를 사용하면 마이크로파 응용 분야에서 우수한 성능을 나타내는 트랜지스터가 생성됩니다. 실리콘 바이폴라 트랜지스터와 비교하여 GaAs MESFET는 4GHz 이상의 입력 주파수에서 더 나은 성능을 제공합니다. 이러한 MESFET는 높은 이득, 낮은 잡음, 고효율, 높은 입력 임피던스 및 열 폭주를 방지하는 특성을 나타냅니다. 이들은 마이크로파 발진기, 증폭기, 믹서 및 고속 스위칭에도 사용됩니다. GaAs MESFET는 고주파 애플리케이션에 사용됩니다.

11.2 VMOSFET (VMOS)

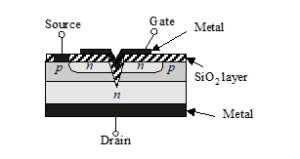

솔리드 스테이트 장치의 전력 성능을 높이기 위해 상당한 연구 노력이 적용되었습니다. 많은 가능성을 보여준 영역은 전도 채널이 기존의 소스-드레인 직선이 아닌 "V"를 형성하도록 수정되는 MOSFET입니다. 추가 반도체 층이 추가됩니다. 용어 VMOS 는 소스와 드레인 사이의 전류가 구성으로 인해 수직 경로를 따른다는 사실로부터 유도된다. 드레인은 이제 그림 47에 표시된 것처럼 추가 된 반도체 재료 조각에 위치합니다. 이는 트랜지스터 드레인 영역이 히트 싱크와 접촉하여 장치에서 발생 된 열을 분산시키는 것을 돕는다. V 형 게이트는 노치의 각 측면에 하나씩 두 개의 수직 MOSFET을 제어합니다. 2 개의 S 단자를 병렬로 연결하면 전류 용량을 두 배로 늘릴 수 있습니다. VMOS는 비대칭이므로 S 및 D 터미널은 저전력 MOS FET의 경우처럼 상호 교환 될 수 없습니다. 기존의 FET는 수 밀리 암페어의 전류로 제한되지만, VMOS FET는 100A 전류 범위에서 동작 할 수있다. 이는 종래의 FET에 비해 전력을 크게 향상시킨다.

VMOS 장치는 고주파수, 고전력 응용 프로그램에 대한 솔루션을 제공 할 수 있습니다. UWF (Ultra-High Frequency) 대역의 주파수에서 10 와트 장치가 개발되었습니다. VMOS FET의 다른 중요한 이점이 있습니다. 열 폭주를 방지하기 위해 온도 계수가 음수입니다. 또한 누설 전류가 낮습니다. 그들은 높은 스위칭 속도를 달성 할 수 있습니다. VMOS 트랜지스터는 게이트 전압의 균등 한 증가에 대한 특성 곡선의 간격을 동일하게 만들 수 있으므로 고전력 선형 증폭기 용 바이폴라 접합 트랜지스터와 같이 사용할 수 있습니다.

그림 47 - VMOS 구성

11.3 기타 MOS 장치

MOS 장치의 또 다른 유형은 이중 확산 공정 FET 제작 때로는 DMOS. 이 소자는 채널의 길이를 줄이는 장점이있어 우수한 저전력 소비와 고속 성능을 제공합니다.

사파이어의 기판 상에 작은 실리콘 아일랜드 상에 FET를 제조하는 것은 때때로 조난 신호. 실리콘 섬은 사파이어 기판 상에 성장 된 실리콘의 얇은 층을 에칭함으로써 형성된다. 이러한 유형의 제조는 실리콘 섬 사이의 절연을 제공하여 소자 들간의 기생 용량을 크게 감소시킨다.

MOS 기술은 큰 값의 커패시터가 가능하지 않더라도 FET와 동시에 커패시터와 레지스터 (MOSFET 사용)가 만들어지는 장점이있다. 인핸스먼트 MOSFET을 사용하면 2 단자 저항이 만들어지고 MOSFET 게이트는 드레인에 연결되어 FET가 핀치 오프 (pinch-off)시 작동하게한다. MOSFET 게이트는 전원을 통해 드레인에 연결되어 FET가 특성의 전압 제어 저항 영역에서 작동 할 때 바이어 싱된다. 이러한 방식으로, 드레인 -로드 저항기는 증착 된 레지스터보다는 MOSFET으로 대체되어 칩 면적을 절약한다.

개요

이 장의 목적은 전계 효과 트랜지스터를 사용하는 증폭기 회로의 분석 및 설계를 소개하는 것입니다. FET는 BJT와 아주 다르다. 그 동작은 전류 제어 장치 인 BJT와 대비되는 전압에 의해 제어된다.

우리의 접근 방식은 BJT 챕터의 방식과 유사합니다. 우리는 FET 동작을 제어하는 물리적 현상을 조사하기 시작했습니다. 이 과정에서 우리는 FET와 BJT의 대비를 강조했다. 우리는 MOSFET으로 연구를 시작한 후 JFET에 관심을 돌 렸습니다. 또한 우리는 이러한 중요한 장치를위한 소 신호 모델을 개발했습니다. 우리는 이러한 모델을 사용하여 FET 증폭기의 다양한 구성을 분석했습니다. FET 회로를 분석하는 방법을 알았 더라면 사양을 충족시키기 위해 설계에주의를 돌 렸습니다. 우리는 또한 컴퓨터 시뮬레이션 프로그램에서 사용 된 모델을 검사했다.

우리는 FET가 집적 회로의 일부로 제조되는 방식을 간단히 살펴 보았습니다. 이 장은 MESFET 및 VMOS를 포함한 다른 유형의 FET 디바이스에 대한 소개로 결론을 맺었습니다.

CURRENT – 11. 기타 장치

CURRENT – 11. 기타 장치 이전 - 10. FET 앰프 설계

이전 - 10. FET 앰프 설계