5. MOSFET 집적 회로

MOSFET 집적 회로

MOSFET 트랜지스터가 집적 회로의 일부로 제조 될 때 실제 고려 사항은 회로 구성의 두 가지 주요 변경을 필요로합니다. 첫째, 개별 증폭기에 사용되는 대형 커플 링 및 바이 패스 커패시터는 크기가 작기 때문에 집적 회로에서 실제로 제조 할 수 없다. 직결 형 증폭기를 제작하여 이러한 단점을 극복합니다.

두 번째 주요 변경 사항은 바이어스 회로의 일부로 사용되는 저항을 쉽게 제작할 수 없다는 점입니다. 대신, MOS 트랜지스터로 구성된 능동 부하 및 전류 소스를 사용합니다.

집적 회로는 NMOS 및 PMOS 회로를 사용합니다. CMOS는 디지털 회로에서보다 일반적으로 사용되는 반면, NMOS는 일반적으로 고밀도 IC (즉, 칩 당 더 많은 기능)에 사용됩니다.

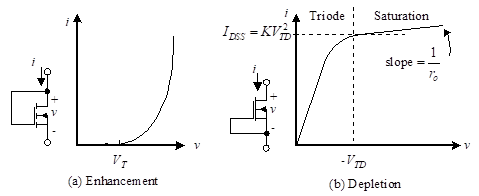

능동 부하 시뮬레이션은 MOS 특성 곡선의 기울기를 이용합니다. 그림 23는 두 가지 유형의 능동 부하를 보여줍니다. 그림 23 (a)에서 NMOS 향상로드를 보여주고 23 (b)는 NMOS 고갈로드를 보여줍니다. 또한 그림에는 관련 특성 곡선이 나와 있습니다.

그림 23 - 활성로드

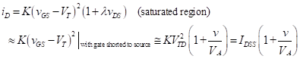

NMOS 향상 부하의 경우 전압과 전류의 관계는

![]()

(29)

이 구성의 등가 저항은 1 /gm여기서 트랜스 컨덕턴스의 값은 바이어스 포인트에 적용되는 값이다.

NMOS 공핍 부하는 다음 식에 의해 주어진 특성의 기울기에 의해 결정되는 등가 저항을 갖는다.

(30)

MOSFET 집적 회로의 5.1 바이어 싱

능동 부하를 시뮬레이트하는 두 가지 기술이 있으므로 이제 편향 문제를 해결할 수 있습니다. 어떤 회로 구성에서도 부하 저항 대신 활성 부하를 사용합니다. 이를 분석하기위한 기술을 보여주기 위해 그림 24와 같이 향상 부하를 사용하는 NMOS 증폭기를 고려해 보자.

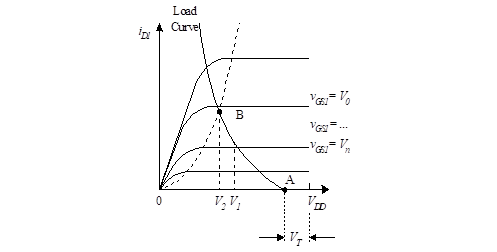

트랜지스터 라벨 Q2 대체 RD 우리의 이전 회로의. 정지 동작 지점을 결정하기 위해 섹션 4, "FET 증폭기 구성 및 바이어스"에서 수행 한 것과 동일한 기술을 사용하여 저항 부하 라인에 대한 향상된 부하 그래픽 특성 만 대체합니다. 즉, 부하 라인에 대한 방정식을 사용하여 FET 트랜지스터 특성의 동시 솔루션을 찾아야합니다. 그림 25와 같이 그래픽으로이를 수행 할 수 있습니다.

파라 메트릭 곡선은 증폭 트랜지스터의 특성 곡선이며, Q1. 능동 부하의 전압 대 전류 특성, Q2 그림 23의 것들입니다. 출력 전압, v아웃, 차이점은 무엇입니까? VDD 및 능동 부하 양단의 전압. 능동 부하의 전류는 증폭 트랜지스터의 드레인 전류와 같습니다. 그러므로 우리는 그림 23의 특성을 시프트 한 미러 이미지를 취하여 부하 선을 구성합니다. 작동 점은이 곡선과 적절한 트랜지스터 특성 곡선의 교차점입니다. 선택할 트랜지스터 커브를 파악하려면 게이트 - 소스 간 전압을 찾아야합니다. 우리가 다음에 보게 될 것처럼, 입력 바이어스 전압은 종종 활성 전류 소스로 대체된다.

그림 25 - Q- 포인트를위한 그래픽 솔루션

이제 능동 부하를 시뮬레이트하는 방법을 알았으므로 입력 바이어스 회로의 일부로 사용될 기준 전류 생성에주의를 돌린다. 이 전류 소스는 BJT 앰프 바이어 싱에 사용 된 것과 거의 같은 방식으로 사용됩니다.

그림 26 - 전류 미러

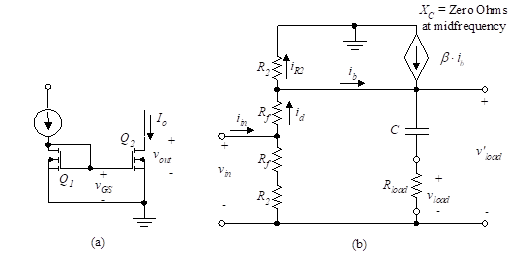

우리는 MOSFET을 분석한다. 현재의 거울. 전류 미러가 그림 26에 나와 있습니다. 2 개의 트랜지스터는 완벽하게 매칭되는 것으로 가정한다. 출력 전류는 Q2, 기준 전류 드라이브 Q1. 트랜지스터가 완벽하게 일치하면 출력 전류는 기준 전류와 정확히 동일합니다. 이것은 트랜지스터가 병렬로 연결되어 있기 때문에 사실입니다. BJT 전류 미러의 경우와 마찬가지로 그림 26 (b)에 표시된 것처럼 기준 저항에 기준 전압을 적용하여 기준 전류를 생성 할 수 있습니다.

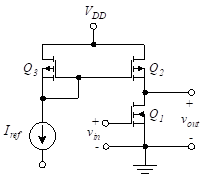

다양한 서브 서킷 (즉, 능동 부하 및 기준 전류)을 결합하면 그림 27의 CMOS 앰프가된다.

이 증폭기의 이득은 다음과 같습니다.

![]()

(31)

그림 27 - CMOS 증폭기

5.2 바디 이펙트

섹션“2. 금속 산화물 반도체 FET (MOSFET)”는 MOSFET의 기판 (또는 본체)을 나타냅니다. 이 기질은 채널 구축에 중요한 역할을합니다. 개별 MOSFET의 작동에서 본체는 종종 전원에 연결됩니다. 이러한 경우 기판은 장치의 작동에 직접적인 영향을 미치지 않으며이 장의 앞부분에서 개발 한 곡선이 적용됩니다.

MOSFET이 집적 회로의 일부로 제조되면 상황이 바뀝니다. 이러한 경우에, 각각의 개별 트랜지스터의 기판은 다른 기판으로부터 절연되지 않는다. 실제로 기판은 칩상의 모든 MOSFET에서 공유되는 경우가 많습니다. PMOS IC에서 공유 기판은 가장 포지티브 소스 단자에 연결되며, NMOS에서는 접지에 연결됩니다 (존재하는 경우 음극 전원에 연결). 이것은 각 트랜지스터의 소스와 바디 사이에 역 바이어스를 설정합니다. 이 역 바이어스의 효과는 작동 특성을 변경하는 것입니다. 예를 들어, n채널 디바이스는 임계 값을 효과적으로 올립니다 (VT). 임계 값이 변경되는 양은 물리적 매개 변수 및 장치 구성에 따라 다릅니다. NMOS의 경우,이 변화는 다음과 같이 근사화 될 수있다.

![]()

(32)

식 (32)에서, γ는 약 0.3와 1 사이에서 변화하는 장치 파라미터이다 (V-1/2). VSB 소스-바디 전압이고 페르미 전위. 이것은 재질의 특성이며 일반적인 값은 실리콘의 경우 0.3 V입니다.

CURRENT – 5. MOSFET 집적 회로

CURRENT – 5. MOSFET 집적 회로 이전 - 4. FET 앰프 구성 및 바이어스

이전 - 4. FET 앰프 구성 및 바이어스