8. FET 증폭기 - 표준 구성

FET 증폭기 - 표준 구성

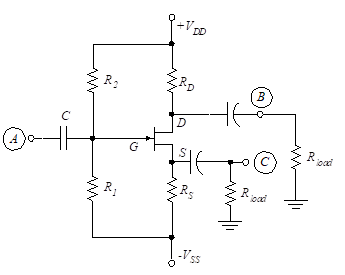

그림 31 - FET 증폭기 - 일반 구성

그림 31은 FET 증폭기의 일반적인 구성을 보여준다.

이 그림에서 우리는 n채널 JFET이지만 소스의 부호에 따라 다른 FET 디바이스에도 적용된다. 출력 (부하)은 B 또는 C 지점에 연결되고 입력은 A 또는 C에 연결됩니다.

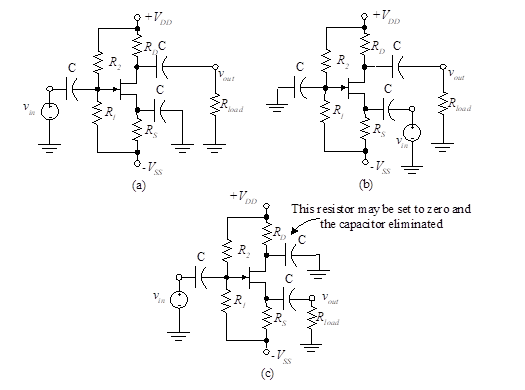

단일 스테이지 BJT 증폭기의 기본 구성이 4 가지였던 것처럼 단일 스테이지 FET 증폭기에는 4 가지 구성이있다. 이러한 구성은 그림 32에 나와 있습니다.

그림 32 (a)에서 우리는 ac JFET 소스 단자에서 접지까지의 경로. 출력은 드레인과 접지 사이에 있으며 입력은 게이트와 접지 사이에 있습니다. JFET 소스 단자는 입력과 출력 모두에 공통이기 때문에이를 공통 - 소스 (CS) 증폭기. 우리는 섹션 9.1에서이 구성이 높은 입력 저항과 높은 전압 이득을 산출하지만 높은 출력 저항을 희생한다는 것을 알 수 있습니다.

그림 32 (a)에서 JFET 소스 단자와 접지 사이의 커패시턴스가 제거되면, 소스 저항이있는 공통 소스 앰프 (또는 소스 저항 증폭기). 이것은 이미 터 저항이있는 CE 앰프와 유사합니다 ( 이미 터 - 저항 증폭기).

그림 32 (b)에서 우리는 (ac)는 게이트 터미널을 접지하고, 출력을 드레인에서 접지로 가져 와서 JFET 소스 터미널과 접지 사이에 입력 신호를인가했다.

게이트가 (ac)을 입력 및 출력에 공통으로 사용하는 공통 게이트 (CG) 증폭기. 우리는 섹션 9.2에서이 구성이 높은 전압 이득과 낮은 출력 저항을 제공하지만 낮은 입력 저항을 희생한다는 것을 알 수 있습니다. 입력 저항이 낮기 때문에이 구성은 전류 이득이 1에 가까운 전류 증폭기 (예 : 신호 분리)로 사용되는 경우가 많습니다.

그림 32 - FET 단일 스테이지 증폭기 구성

마지막으로 그림 32 (c)는 드레인이 접지 된 구성을 보여줍니다 (ac), 게이트에서 접지로 신호 입력, JFET 소스 단자에서 접지로 출력. 드레인은 공통이기 때문에 (ac)를 입력 및 출력 모두에 적용하는 경우이를 a 공통 드레인 (CD) 구성. 또는, 소스 팔로어 (SF) 작동 방식 때문입니다. 섹션“9.3 CD (SF) 증폭기”에서 전압 이득이 낮은 출력 저항과 높은 입력 저항으로 거의 일치하는 것을 볼 수 있습니다. 따라서 출력 (JFET 소스 터미널)은 입력을 "따르고"이 구성은 종종 버퍼로 사용됩니다.

CURRENT – 8. FET 증폭기 – 표준 구성

CURRENT – 8. FET 증폭기 – 표준 구성 이전 - 7. 컴퓨터 시뮬레이션을위한 FET 모델

이전 - 7. 컴퓨터 시뮬레이션을위한 FET 모델