2. 반전 증폭기

반전 증폭기

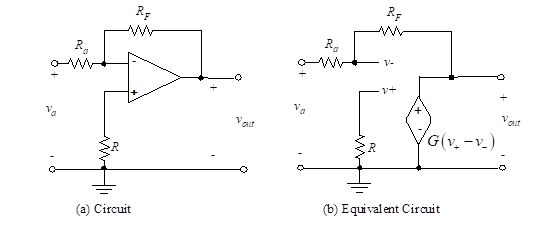

그림 3 - 반전 연산 증폭기

그림 3 (a)는 피드백이있는 반전 증폭기를 보여주고, 그림 3 (b)는 이상적인 반전 연산 증폭기 회로에 대한 등가 회로를 보여줍니다. 우리는 이상적인 연산 증폭기의 속성을 사용하여 연산 증폭기 입력을 개방 회로로 모델링했습니다. 제어 된 소스는 Gvd, 주어진 가정하에이 정보를 명시 적으로 사용할 필요는 없습니다. 우리는 출력 전압을 풀고 싶습니다. v아웃, 입력 전압의 관점에서, va. 우리는 v+ 과 v- 이 표현식을 서로 동일하게 설정하십시오. 현재부터 R 0 인 경우,

(12)

또한 Kirchhoff의 노드 방정식은 v- 수율,

(13)

이후 v+ = v- 과 v+ = 그 다음 0 v- 또한 0입니다. 그러므로 우리는 두 개의 미지수에 하나의 방정식을 가지고 있습니다. va 과 v아웃그래서 우리는 폐 루프 게인을 풀 수 있습니다.

(14)

폐 루프 게인, v아웃 /va는 음 (반전)이며 2 개의 저항의 비율에만 의존하며, RF /Ra. 이것은 매우 높은 개 루프 이득과 독립적이며, G. 이 바람직한 결과는 입력 전압에서 빼기 위해 출력 전압의 일부에 대한 피드백의 사용에 기인한다. 출력에서 입력을 통한 피드백 RF 차동 전압을 구동하는 역할을하며, vd = v+ - V-0에 가깝습니다. 비 반전 입력 전압, v+, 0 일 때 피드백은 주행의 효과가 있습니다. v- 0으로. 따라서, 연산 증폭기의 입력에서,

(15)

이상적인 연산 증폭기 회로가 아무리 복잡해도이 간단한 절차를 따르면 엔지니어는 연산 증폭기 시스템을 신속하게 분석 (그리고 곧 설계) 할 수 있습니다.

이제이 결과를 다중 입력의 경우까지 확장 할 수 있습니다.

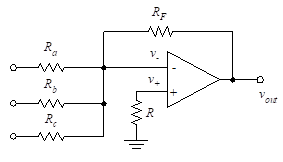

그림 4- 연산 증폭기 회로

그림 (4)에 표시된 증폭기는 여러 입력 전압의 음의 가중치 합계 출력을 생성합니다.

현재부터 R 0 인 경우, v+ = 0. 반전 입력단에서의 노드 방정식은 다음과 같습니다. (16) :

(16)

이후 v+ = v-다음, v+ = 0 = v- 우리가 찾는다. v아웃 다음과 같이 입력 관점에서 :

(17)

확장 기능 n 입력은 간단합니다.

어플리케이션

TINACloud 회로 시뮬레이터를 사용하여 다음 회로를 분석하여 V를 결정하십시오.아웃 아래의 링크를 클릭하면 입력 전압의 관점에서 볼 수 있습니다.

CURRENT – 2. 반전 증폭기

CURRENT – 2. 반전 증폭기 이전 - 1. 이상적인 연산 증폭기

이전 - 1. 이상적인 연산 증폭기