2. 레벨 쉬프터

레벨 쉬프터

증폭기에 대한 입력의 평균값이 0V 인 경우에도 출력에는 종종 바이어스 효과로 인해 0이 아닌 평균 전압이 있습니다. 이들 dc 전압은 시스템의 동작에 악영향을 미치는 바람직하지 않은 오프셋을 야기 할 수있다.

연산 증폭기가 다단계이기 때문에 dc 고 이득의 원치 않는 증폭기 dc 전압이 문제의 원인이 될 수 있습니다. 초기 단계의 작은 오프셋은 이후 단계를 포화시킬 수 있습니다.

레벨 쉬프터 은 보상을 위해 입력에서 알려진 전압을 더하거나 빼는 증폭기입니다 dc 오프셋 전압. 연산 증폭기에는 레벨 시프터가 포함되어 있습니다.

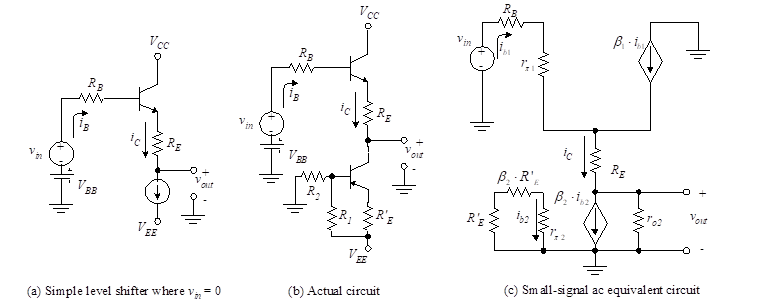

그림 7는 간단한 레벨 쉬프터를 보여줍니다. 이 시프터는 다음과 같은 경우에 단위 이득 증폭기로 작동합니다. ac 조정 가능한 dc 출력.

그림 7 (a)의 입력 루프에서 KVL을 사용하여 분석을 시작하고 vin = 0을 구하십시오.

(34)

지금부터

(35)

우리는 dc 출력 전압 값, V아웃.

(36)

방정식 (36)은 RE, V아웃 원하는대로 설정할 수 있습니다. dc 레벨 (최대 VBB-VBE). 이후 VBB 이다 dc 레벨을 얻으려면이 앰프를 사용하여 레벨을 이동하십시오 아래로 (낮은 값으로). 만약 상승 변속이 필요하며 유사한 회로가 사용되지만 PNP 트랜지스터는 npn 트랜지스터. 활성 전류 소스가있는 완전한 회로가 그림 7 (b)에 나와 있습니다.

그림 7- 레벨 쉬프터

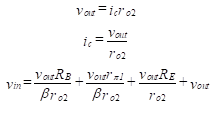

이제 우리는 회로를 ac 적용된 신호. 그림 7 (c)는 ac 등가 회로. 유의 사항 β2ib2 는 활성 전류 소스의 컬렉터 전류이며이를 상수라고 가정합니다. 왜냐하면 ac 전류 값이 0이면,이 전류 소스는 개방 회로로 대체됩니다. 우리는 ac 방정식은 KVL을 사용합니다.

(37)

과

(38)

비율 ac ~에 출력 ac 입력은이다

(39)

방정식 (39)은 다음과 같이 나타냅니다. ro2 입력에 대한 출력의 비율은 1에 가까워지고 레벨 쉬프터는 에미 터 팔로워처럼 작용합니다 ac. 이것이 바람직한 결과입니다.

예

두 개의 직접 결합 CE 증폭기가 원하는 전압 이득을 얻기 위해 직렬로 배치됩니다. 2 개의 CE 증폭기 사이에 배치 된 레벨 시프터를 설계하여 dc 제 2 CE 증폭기가 포화되는 것을 방지하기에 충분히 낮은 전압이다. 두 번째 단계에 1 V 바이어스를 제공하면됩니다. 콜렉터 전압, VC, 첫 번째 앰프의 4 V, RC 그 앰프의 1 kΩ입니다. 레벨 시프터를 설계하여 IC 의 1 mA 사용 ![]() 전원 공급 장치. 그림 3에 표시된 유형의 전류 소스를 사용하십시오 (장 : 차동 증폭기 1.3 참조). β (s) = 100, VBE(들) = 0.7 V 및 VON = 0.7 V.

전원 공급 장치. 그림 3에 표시된 유형의 전류 소스를 사용하십시오 (장 : 차동 증폭기 1.3 참조). β (s) = 100, VBE(들) = 0.7 V 및 VON = 0.7 V.

해결 방법 : 레벨 시프터는 그림 7 (b)에 나와 있습니다. 우리는 RE, R1, R2및 아르 자형'E. 첫 번째 앰프는 VC 4 V의 값 VBB 방정식 (36)은 4 V이고, RB 그 공식의 1 kΩ입니다. 이전 앰프의 Thevenin 등가 회로를 사용하고 있습니다. 방정식 (36)

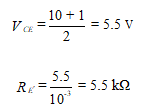

전류 - 소스 트랜지스터 동작 점을 dc 로드 라인, 우리는

과

가로 지르는 전압 아르 자형'E 5.5 V입니다. 그렇다면

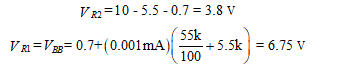

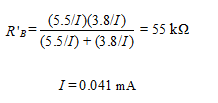

우리는 이제 전압을 알고 있습니다. R1 과 R2 및 병렬 저항. 그림 9.7 (b)의 하부 트랜지스터에서베이스 전류가 무시할 수 있다고 가정하는 두 개의 방정식이 나온다.

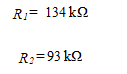

과

따라서 설계가 완료되었습니다.

신청

또한 아래의 링크를 클릭하여 인터프리터 도구를 사용하여 TINA 또는 TINACloud 회로 시뮬레이터로 이러한 계산을 수행 할 수 있습니다.

CURRENT – 2. 레벨 시프터

CURRENT – 2. 레벨 시프터 이전 - 1. 차동 증폭기

이전 - 1. 차동 증폭기