8. 반전 증폭기

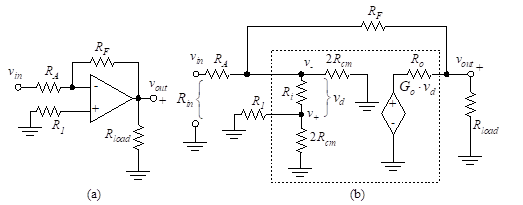

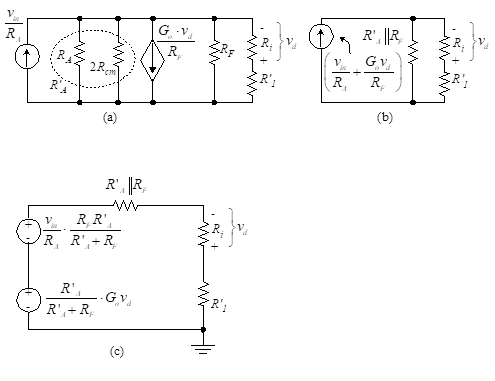

그림 36 (a)는 반전 증폭기를 보여준다. 그림 36 (b)는이 장의 앞부분에서 개발 된 연산 증폭기 모델을 사용한 등가 회로를 보여준다.

8.1 입력 및 출력 저항

그림 36 (b)는 Figure 37 (a)로 축소됩니다. ![]()

그림 37 - 단순화 된 반전 증폭기 모델

이러한 부등식이 적용되지 않는다고 가정하는 것이 타당합니다. 출력이 입력을로드하고 이득이 감소하기 때문입니다.

전압 분배기 관계를 사용하여

(71)

루프 방정식은

(72)

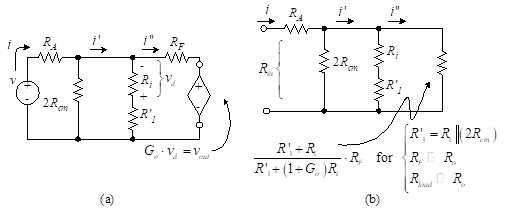

입력 저항, Rin은 그림 37 (b)에서 구한 것입니다. 여기서 우리는 종속 소스를 등가 저항으로 대체했습니다. 이 저항의 값은 다음과 같습니다. v-/나는" (72)로부터 구해진다. 큰 경우 G (즉, ![]() ), 그림 37 (b)의 가장 오른쪽 저항은 대략 0이고,

), 그림 37 (b)의 가장 오른쪽 저항은 대략 0이고, ![]() .

.

반전 증폭기의 출력 저항은 비 반전 증폭기의 출력 저항과 동일합니다. 그러므로,

(73)

8.2 전압 이득

그림 36 (b) 및 그림 37 (a)의 등가 회로를 사용하여 전압 이득을 결정합니다. 반전 입력 게인, A- = v아웃/vin는 그림 37 (a)의 회로에서 출력 저항을 찾는 것과 동일한 가정을 다시함으로써 얻어진다.

이러한 가정은 그림 38 (a)에 표시된 회로로 회로를 축소합니다. 여기서 저항과 병렬로 전류 소스에 대한 저항과 직렬로 전압 소스를 변경했습니다. 그런 다음 저항을 결합하여 그림 38 (b)의 회로를 생성 할 수 있습니다. 마지막으로 전류원을 다시 전압원으로 변환하여 그림 38 (c)의 회로를 단순화한다.

이 회로의 루프 방정식은

(74)

이후 v아웃 = Govd, 반전 전압 이득은

(75)

그림 38 (파트 a, b, c) - 입력 게인 반전

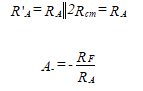

근사치를 만들어 이상적인 연산 증폭기의 이득과 관련하여이 결과를 검증 할 수 있습니다. RA << 2Rcm 과 G >> 1. 그런 다음

(76)

이는 단순화 된 모델에서 이전에 발견 된 결과와 동일합니다.

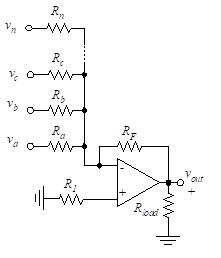

8.3 다중 입력 증폭기

(39)

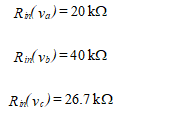

전압 va, vb,…, vm 저항을 통해 합산 접합 (op-amp의 반전 입력)에인가된다 Ra, Rb,…, Rm, 그림 39와 같이 출력 전압은

(77)

바이어스 균형을 달성하기 위해

(78)

정의하자.

![]()

(79)

출력 저항은

(80)

이제는 두 개의 입력 만 사용되었다고 가정합니다. 출력 전압은

(81)

입력 저항 va 대략 같음 Ra, 및에서의 입력 저항 vb 약 Rb. 우리는이 회로를 출력 전압이 1 인 단일 입력 2 입력 하도로 만들 수 있습니다.

(82)

설정하여 RF = Ra = Rb. 비 반전 입력 단자에서 접지까지의 저항은 바이어스 밸런스를 달성하도록 선택됩니다. 그러므로, R1 = RF/ 3, 우리는

(83)

등 이득 (즉, 단일이 아닌) 2 입력 여름은 다음과 같이 설정합니다. ![]() 과

과 ![]() . 이 경우, 출력 전압은

. 이 경우, 출력 전압은

(84)

입력 저항은 대략 R. 이후 RA = R/ 2,

(85)

If m 입력은 동일한 저항을 통해 합산됩니다 ( R), 출력 전압은

(86)

이 등가 이득 다중 입력 반전 합산 기의 경우, 각 입력에 대한 입력 저항은 대략 R. 이후 RA = R/m,

(87)

과

(88)

출력 저항은

(89)

예

741 op-amp를 사용하여 3 입력 반전 증폭기를 설계 및 분석합니다.

입력 저항은이다. R분 = 8 kΩ.

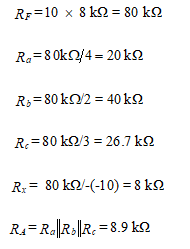

해결 방법 : "이상적인 연산 증폭기"장의 설계 방법을 사용하여 X = 0, Y = 9, Z = -10.

그때

증폭기의 이득 승수는 1 +RF/RA = 10. 입력 저항은 다음과 같이 나타납니다.

출력 저항은 대략 75 (10) / 105 = 7.5 mΩ. 바이어스 균형을 달성하기 위해

CURRENT – 8. 반전 증폭기

CURRENT – 8. 반전 증폭기 이전 - 7. 비 반전 증폭기

이전 - 7. 비 반전 증폭기