9. 차동 합산

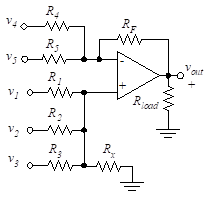

그림 40 - 차동 합산

Op 앰프는 여러 입력의 가중치 합계 출력을 생성하도록 구성 할 수 있습니다. 합계에 양수 및 음수 부호가 모두 포함되면 DIfferential Summing 결과.

그림 40의 연산 증폭기 구성은 출력 전압을 생성하며, v아웃, 주어진

(90)

어디에

(91)

바이어스 밸런스를 달성하기 위해 다음과 같이 저항을 선택합니다.

(92)

각각의 반전 입력에 대한 입력 저항, vj이다 Rj.

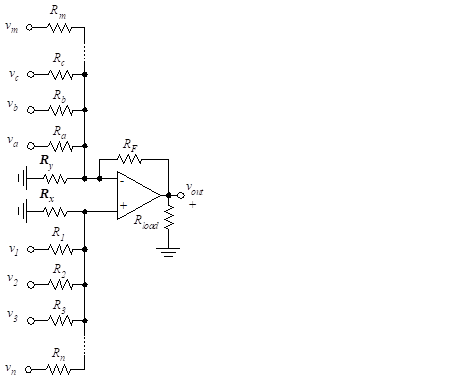

반전 단자와 비 반전 단자에 각각 하나의 입력 만 있으면 결과는 a입니다. 차동 증폭기. 이것은 그림 41에 나와 있습니다.

그림 41 - 차동 증폭기

이 구성의 출력 전압은 다음과 같습니다.

(93)

RA = Ra [수식 91] 참조. 바이어스 균형을 달성하기 위해

(94)

입력 저항 va 터미널은 RA. 입력 저항 v1 터미널은 ![]() 어디로 Rin 식 (56)로부터

어디로 Rin 식 (56)로부터

(95)

그때 Rin(에서 V1)는 약 R1+R2. R아웃 수식 (52)에서 발견되며

(96)

단위 이득 차이를 얻으려면, 출력은 다음과 같이 주어진다. v아웃 = v1 - va 우리는 설정 RA = RF = R1 = Rx. 741 연산 증폭기가 사용되는 경우이 4 개의 저항에 대한 일반적인 값은 10 kΩ입니다.

입력 저항이 v아웃 그러면 10 kΩ이고 v1 단자의 저항은 20 kΩ입니다.

등 이득 차이를 원하지만 이득이 단일 일 필요는 없다고 가정 해보십시오. 우리는 R1 = RA 과 Rx = RF. 출력 전압은

(97)

입력 저항 va 터미널은 ![]() , 비 반전 단자에는 대략입니다. RA + RF 이후 Rin >> RF. 입력 저항 값 및 R아웃 방정식 (95)과 방정식 (96)을 사용하여 쉽게 결정됩니다.

, 비 반전 단자에는 대략입니다. RA + RF 이후 Rin >> RF. 입력 저항 값 및 R아웃 방정식 (95)과 방정식 (96)을 사용하여 쉽게 결정됩니다.

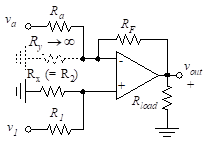

그림 41의 Differencing 앰프 구성의 유용한 수정은 부호 전환기 그림 42에 표시된대로.

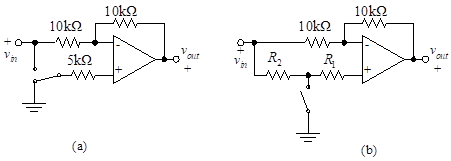

그림 42 – 사인 스위처

그림 42 (a)에 표시된 위치에 스위치를 놓으면 v아웃 =-vin, 반대의 스위치 위치에 대해서는, v아웃 = 2vin - vin = vin. 입력 저항은 각 위치에 대해 10 kΩ이며 바이어스는 각 위치에서 균형을 이룹니다. 그림 42 (a)는 단극 쌍투 스위치를 보여줍니다. 부호 전환은 그림 42 (b)에서와 같이 단발 스위치로도 수행 할 수 있습니다. 그러나이 구현을 위해 바이어스 및 입력 저항은 두 스위치 위치에서 동일하지 않습니다.

예

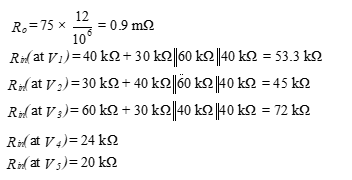

출력이있는 다중 입력 741 앰프의 각 입력에서 출력 저항과 입력 저항을 결정합니다.

+ 및 – 단자의 저항 값이 10kΩ이라고 가정합니다.

해결 방법 : 더 큰의 사용 X 및 (Y+ 1)는 다음을 결정하기위한 배율 인수를 산출합니다. RF.

회로는 그림 43에 나와 있습니다.

CURRENT – 9. 미분 합산

CURRENT – 9. 미분 합산 이전 - 8. 반전 증폭기

이전 - 8. 반전 증폭기