IBIS modeliavimas

IBIS modeliavimas

Jump to TINA Main Page & General Information

IBIS modeliavimas

IBIS (įvesties / išvesties buferio informacijos specifikacija) yra būdas pateikti modeliavimo informaciją apie integrinių grandynų įvesties / išvesties buferius. IBIS modelių geras dalykas yra tai, kad jie dažnai yra prieinami net ir tiems prietaisams, kuriuose gamintojai negali gauti pilnų prietaisų modelių dėl kokių nors priežasčių (pvz., Sudėtingumo, nuosavybės teisių apsaugos ir pan.).

Vienas iš populiariausių IBIS modelių naudojimo yra signalo vientisumo analizė, įskaitant impedanso atitikimą ir dar daugiau.

Šiuo metu TINA palaiko plačiausiai naudojamą IBIS 4.2 versiją.

TINA galite konvertuoti IBIS modelius į TINA Spice makrokomandas ir tada jas naudoti bet kuriuose TINA grandiniuose. Taip pat galite atlikti supaprastintus skaitmeninių įrenginių modelius, pvz., MCU su IBIS modeliais, kad geriau apibūdintumėte jų analoginį elgesį.

Toliau mes parodysime IBIS modelių naudojimą, pavyzdžiu nustatant signalo vientisumą tarp „Texas Instrument TMS320C6748 DSP“ ir ADS1259 delta-sigma ADC.

pasirinkti Failas / Importas / IBIS failas (* .ibs), Pasirinkite c6748zce.ibs nuo TINA katalogas >Pavyzdžiai IBIS.

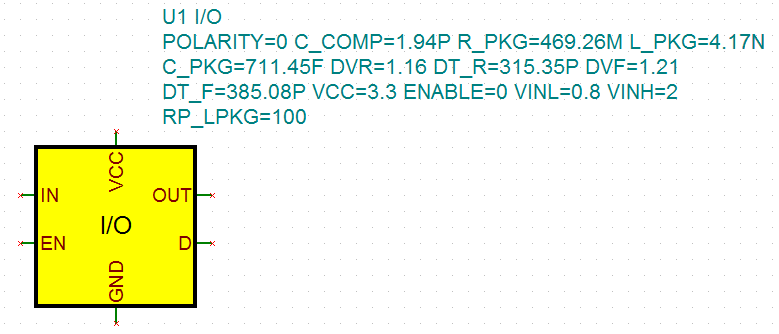

Bus rodomas toks dialogo langas. Šiame dialogo lange galite pasirinkti importuojamą modelį.

Dabar pasirinkite SPI1CLK_GP213 signalas, PBFZP18LL_X50_PI_3P3 modelis (ląstelė veikiama 3.3V be ištraukimo arba nuleidimo), ir Tipas nustatyta vertė.

Paspauskite OK. IBIS modelis automatiškai konvertuojamas į a Spice makro.

SPI1CLK_GP213 yra TMS320C6748 lusto pagrindinio konfigūravimo serijos laikrodžio signalas, skirtas AD konverterio „Texas Instruments ADS1259“ SPI laikrodžio įvedimui.

pasirinkti Failas / Importas / IBIS failas (* .ibs), Pasirinkite ads1259.ibs nuo TINA katalogas >Pavyzdžiai IBIS.

Bus rodomas toks dialogo langas. Šiame dialogo lange galite pasirinkti importuojamą modelį.

Dabar pasirinkite SCK įvesties signalas, DIN_PD_3 modelis ir daugiausia vertė (3.3V DVDD įtampos diapazonui).

Paspauskite OK. IBIS modelis automatiškai konvertuojamas į a Spice makro.

Prijunkite DSP I / O buferį prie ADC įvesties be nuostolių perdavimo linijos.

Pridėkite maitinimo šaltinio ir įtampos generatorių, kad sukurtumėte DSP pusės laikrodžio signalą. Į signalo mazgus įdėkite modeliavimo įtampos kaiščius.

Pritaikome perdavimo linijos parametrus iki kelių colių mikroschemos pėdsakų, nukreiptų ant keturių sluoksnių PCB. Tai sukuria cc. 500ps uždelsimas ir 90 Ohms charakteristika.

Failas iš \ Pavyzdžiai \ IBIS \ TMS320C6748.TSC impedanso atitikimas yra paruoštas naudoti.

Dabar spustelėkite Analizė, Transient.

DSP perduoda SPI laikrodžio signalą, kai impedanso neatitikimas sukuria atspindžius. Rezultatas rodo atspindžius, kuriuos sukelia impedanso neatitikimai šiame grandinės modeliavime.

ADC pusėje (kaištis EoTL) įtampa yra virš žemės ir maitinimo įtampa, kuri pažeidžia absoliučią maksimalią skaitmeninio įėjimo vertę.

Kad būtų išvengta ir viršijama linijos gale, reikia suderinti vairuotojo išėjimo impedanciją su pėdsako varža, įterpiant rezistorių tarp išėjimo ir pėdsako.

Įdėkite 100 Ω rezistorių serijoje dabar su išėjimu.

Dar kartą atlikite pereinamąją analizę ir palyginkite rezultatus, kopijuodami svarbias kreives.

Dabar matome, kad naudojant IBIS modelį, norint suprasti ir rasti svarbiausius su modeliavimu susijusius klausimus, padėjo išspręsti šią problemą.