2. Metalo oksido puslaidininkinis FET (MOSFET)

Metalo oksido puslaidininkinis FET (MOSFET)

Metalo oksido puslaidininkinis FET (MOSFET) yra keturių galų įrenginys. Terminalai yra šaltinis (S), vartai (G) ir nutekėjimas (D), substratas or kūnas sudaro ketvirtąjį terminalą. MOSFET yra sukonstruotas taip, kad vartų gnybtas izoliuotas nuo kanalo silicio dioksido dielektriku. MOSFET gali būti bet kuris išeikvojimas or patobulinimo režimas. Trumpai apibrėžiame šias dvi sąvokas.

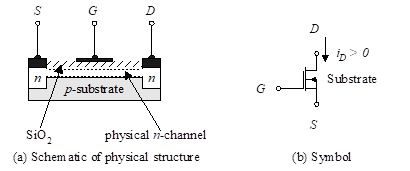

1 pav. – n kanalų išeikvojimo MOSFET

Dėl SiO MOSFET kartais vadinami IGFET (izoliuotų vartų lauko efekto tranzistoriai).2 sluoksnis, naudojamas kaip izoliatorius tarp vartų ir pagrindo. Analizę pradedame nuo išeikvojimo režimo MOSFET. Kaip gali būti ir BJT npn or PNP, MOSFET gali būti bet kuris n-kanalas (NMOS) arba p-kanalas (PMOS). 1 paveiksle pavaizduota an fizinė struktūra ir simbolis n-kanalo išeikvojimas MOSFET. Atkreipkite dėmesį, kad substratas yra prijungtas prie šaltinio terminalo. Taip bus beveik visada.

Išeikvojimo MOSFET yra sukonstruotas su a fizinis kanalas įdėtas tarp kanalizacijos ir šaltinio. Dėl to, kai įtampa, vDS, yra taikoma tarp kanalizacijos ir šaltinio, srovė, iD, yra tarp kanalizacijos ir šaltinio, nors vartų gnybtas G lieka neprijungtas (vGS = 0 V).

Statyba n-kanalo išeikvojimas MOSFET prasideda p- legiruotas silicis. The n- legiruoti šaltinio ir drenažo šuliniai sudaro mažo atsparumo jungtis tarp galų n- kanalas, kaip parodyta 1 paveiksle. Plonas silicio dioksido sluoksnis nusėda, dengiantis plotą tarp šaltinio ir kanalizacijos. SiO2 yra izoliatorius. Aliuminio sluoksnis yra nusodinamas ant silicio dioksido izoliatoriaus, kad sudarytų vartų gnybtą. Veikiant, neigiamas vGS išstumia elektronus iš kanalo srities ir taip išeikvoja kanalą. Kada vGS pasiekia tam tikrą įtampą, VT, kanalas yra nuspaustas. Teigiamos vertės vGS padidinti kanalo dydį, todėl padidės nutekėjimo srovė. Išeikvotas MOSFET gali veikti su teigiamomis arba neigiamomis reikšmėmis vGS. Kadangi vartai yra izoliuoti nuo kanalo, vartų srovė yra nežymiai maža (maždaug 10-12 A).

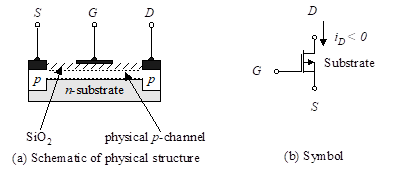

2 pav. p-kanalo išeikvojimas MOSFET

2 paveikslas yra panašus į 1 paveikslą, išskyrus tai, kad mes pakeitėme n-kanalo išeikvojimas MOSFET iki a p-kanalo išeikvojimas MOSFET.

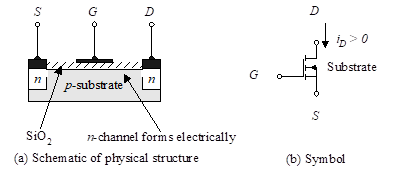

Šios n-kanalo patobulinimo MOSFET pavaizduotas 3 paveiksle kartu su grandinės simboliu. Tai dažniausiai naudojama lauko tranzistoriaus forma.

3 pav. – n kanalų patobulinimo MOSFET

Šios n-kanalo patobulinimo MOSFET skiriasi nuo išeikvoto MOSFET tuo, kad neturi plono n- sluoksnis. Norint sukurti kanalą, reikia teigiamos įtampos tarp vartų ir šaltinio. Šis kanalas susidaro veikiant teigiamai įtampai nuo vartų iki šaltinio, vGS, kuris pritraukia elektronus iš substrato srities tarp n- legiruotas kanalizacija ir šaltinis. Teigiamas vGS dėl to elektronai kaupiasi paviršiuje po oksido sluoksniu. Kai įtampa pasiekia slenkstį, VT, į šią sritį pritraukiamas pakankamas elektronų skaičius, kad jis veiktų kaip laidus n- kanalas. Nėra pastebimos išleidimo srovės, iD egzistuoja iki vGS viršija VT.

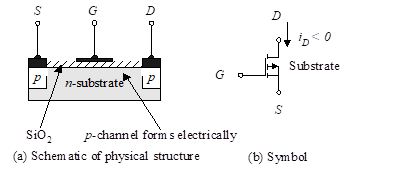

4 paveikslas yra panašus į 3 paveikslą, išskyrus tai, kad mes pakeitėme n-kanalo patobulinimas MOSFET į a p-kanalo tobulinimo MOSFET.

4 pav. p-kanalo patobulinimo MOSFET

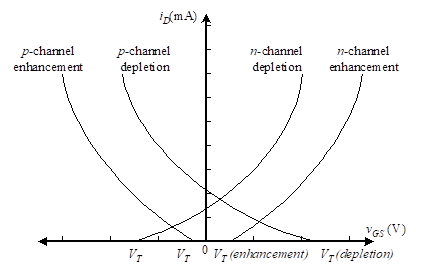

Apibendrinant galima pasakyti, kad MOSFET šeima identifikuoja iD palyginti su vGS kreivės, parodytos 5 paveiksle. Kiekviena charakteristikos kreivė sukuriama esant pakankamai nutekėjimo šaltinio įtampai vDS kad prietaisas veiktų normaliai iD palyginti su vDS kreivės. Tolesniuose skyriuose aptariama slenkstinė įtampa bus apibrėžta VT tiek tobulinimo MOSFET, tiek išeikvojimo MOSFET.

5 pav. iD palyginti su vGS MOSFET šeimos charakteristikos, užtikrinančios pakankamą nutekėjimo šaltinio įtampą VDS

2.1 Patobulinimo režimo MOSFET terminalo charakteristikos

Dabar, kai pristatėme pagrindinę MOSFET struktūrą ir veikimo pagrindą, naudojame metodą, norėdami ištirti patobulinimo režimo įrenginio terminalo elgseną. Pirmiausia atlikime keletą bendrų pastabų iš 1 paveikslo. Pagalvokite apie normalų srovės srautą MOSFET kaip iš kanalizacijos į šaltinį (kaip ir BJT, ji yra tarp kolektoriaus ir emiterio). Kaip ir su npn BJT, tarp nutekėjimo ir šaltinio yra du vienas kitą papildantys diodai. Todėl mes turime pritaikyti išorinę įtampą vartams, kad srovė tekėtų tarp kanalizacijos ir šaltinio.

Jei įžeminame šaltinį ir įtampai suteikiame teigiamą įtampą, ta įtampa iš tikrųjų yra vartų įtampa. Teigiama vartų įtampa pritraukia elektronus ir atstumia skyles. Kai įtampa viršija slenkstį (VT), pritraukiama pakankamai elektronų, kad susidarytų laidus kanalas tarp nutekėjimo ir šaltinio. Šiuo metu tranzistorius įsijungia, o srovė priklauso nuo abiejų vGS ir vDS. Turėtų būti aišku, kad VT yra teigiamas skaičius an n-kanalo įrenginys ir neigiamas skaičius a p- kanalo įrenginys.

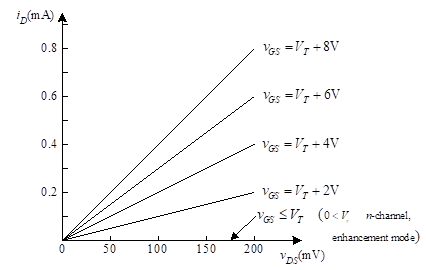

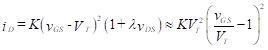

Sukūrus kanalą (ty vGS >VT), srovė gali tekėti tame kanale tarp nutekėjimo ir šaltinio. Šis srovės srautas priklauso nuo vDS, bet tai taip pat priklauso nuo vGS. Kai vGS vos vos viršija slenkstinę įtampą, gali tekėti labai mažai srovės. Kaip vGS padidėja už slenksčio, kanale yra daugiau nešėjų ir galimos didesnės srovės. 6 paveiksle parodytas ryšys tarp iD ir vDS kur vGS yra parametras. Atkreipkite dėmesį, kad už vGS mažesnė už slenkstį, srovė neteka. Dėl aukštesnių vGS, ryšys tarp iD ir vDS yra maždaug tiesinis, rodantis, kad MOSFET elgiasi kaip rezistorius, nuo kurio varža priklauso vGS.

6 pav.iD palyginti su vDS patobulinimo režimui n-kanalo MOSFET kai vDS yra mažas

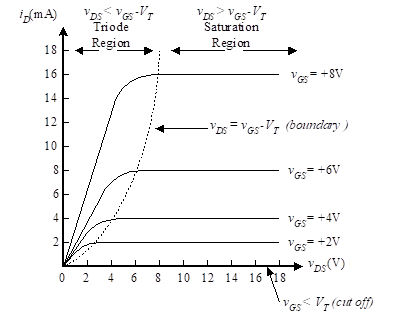

6 paveikslo kreivės atrodo kaip tiesios linijos. Tačiau jie nebus tęsiami kaip tiesios linijos vDS tampa didesnis. Prisiminkite, kad laidumo kanalui sukurti naudojama teigiama vartų įtampa. Tai daro pritraukdama elektronus. Teigiama nutekėjimo įtampa daro tą patį. Kai artėjame prie kanalo nutekėjimo galo, kanalą sukurianti įtampa artėja vGS-vDS kadangi du šaltiniai priešinasi vienas kitam. Kai šis skirtumas yra mažesnis nei VT, kanalas nebeegzistuoja visoje erdvėje tarp šaltinio ir nutekėjimo. Kanalas yra apribota nutekėjimo gale ir toliau didėja vDS nesukelia jokio padidėjimo iD. Tai žinoma kaip įprastas veikimo regionas arba sotis 7 paveiksle parodyta charakteristikų kreivių horizontalioji dalis. Kai skirtumas didesnis nei VT, mes tai vadiname triodai režimu, nes potencialai visuose trijuose gnybtuose stipriai veikia srovę.

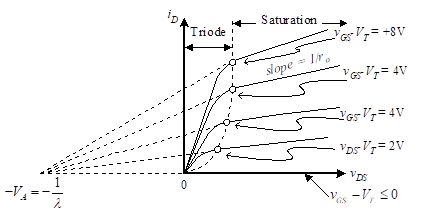

Ankstesnė diskusija veda prie 7 paveikslo veikimo kreivių.

7 pav.iD palyginti su vGS patobulinimo režimo MOSFET

Perėjimas tarp triodo ir įprastos veikimo srities (vadinamos prisotinimo sritimi ir dažnai nurodomas kaip veikimas suspaudimo režimu) 7 paveiksle parodytas kaip punktyrinė linija, kur

![]()

(1)

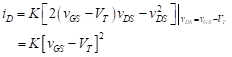

Prie triodo srities ribos kreivių keliai maždaug atitinka santykį,

![]()

(2)

(2) lygtyje K yra konstanta tam tikram įrenginiui. Jo vertė priklauso nuo įrenginio matmenų ir jo gamyboje naudojamų medžiagų. Konstantą suteikia

![]()

(3)

Šioje lygtyje μn yra elektronų judrumas; Coksidas, oksido talpa, yra talpa, tenkanti vartų ploto vienetui; W yra vartų plotis; L yra vartų ilgis. Lygtis rodo sudėtingą ir netiesinį ryšį tarp iD ir dvi įtampos, vDS ir vGS. Kadangi norėtume, kad nutekėjimo srovė svyruotų maždaug tiesiškai vGS (nepriklauso nuo vDS), FET paprastai nenaudojamas triodo srityje.

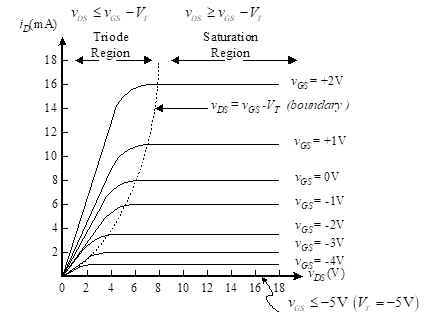

Dabar norime rasti veikimo kreivių lygtį prisotinimo srityje. Mes galime nustatyti reikšmes perėjimo tarp triodo ir soties srities, įvertindami (2) lygtį perėjime (kelyje). Tai yra,

(4)

Ši lygtis nustato nutekėjimo srovės dydį ties riba (punktyrinė linija 8 paveiksle) kaip vartų ir šaltinio įtampos funkciją. vGS. Jei reikia, mes galime atsižvelgti į nedidelį charakteristikų kreivių nuolydį soties srityje, pridėdami tiesinį koeficientą.

![]()

(5)

Lygtyje (5) λ yra maža konstanta (8 pav. pavaizduotų charakteristikų kreivių beveik horizontalios atkarpos nuolydis). Paprastai jis yra mažesnis nei 0.001 (V-1). Tada

![]()

(6)

Visos mūsų ankstesnės diskusijos buvo susijusios su NMOS tranzistorius. Dabar trumpai aptariame būtinus PMOS pakeitimus. PMOS vertės vDS bus neigiamas. Be to, norėdami sukurti kanalą PMOS, ![]() .

.

8 pav. MOSFET tranzistoriaus gnybtų charakteristikos

Vieninteliai pokyčiai, palyginti su NMOS tranzistorių charakteristikomis (7 pav.), yra tai, kad horizontalioji ašis dabar yra -vDS vietoj +vDS o parametrinės kreivės rodo didesnę nutekėjimo srovę, kai vartų įtampa mažėja (užuot didėja NMOS tranzistorius). Didėjančių srovės verčių kreivės atitinka neigiamą vartų įtampą. Kada vGS > VT, tranzistorius yra išjungtas. Norėdami pagerinti PMOS, VT yra neigiamas, o PMOS išeikvojimas, VT yra teigiamas.

PMOS tranzistoriaus triodo srities perėjimo srovės lygtis yra identiška NMOS. Tai yra,

![]()

(7)

Atkreipkite dėmesį, kad vGS ir vDS abu yra neigiami dydžiai. PMOS tranzistoriaus prisotinimo srities lygtis taip pat yra identiška NMOS lygtis. Tai yra,

(8)

Atkreipkite dėmesį, kad λ yra neigiamas PMOS tranzistoriams, nes kreivės kitimo greitis (![]() ) yra neigiamas.

) yra neigiamas.

Paimant abiejų (6) lygties pusių dalinę išvestinę vGS, ![]() , mes gauname

, mes gauname

![]()

(9)

Mes teikiame pirmenybę vertei gm būti pastovus, ypač esant dideliems signalo svyravimams. Tačiau mes galime tik apytiksliai įvertinti šią sąlygą, jei naudosime FET mažoms signalų programoms. Esant dideliam signalui, kai kuriose programose bangos formos iškraipymas gali būti nepriimtinas.

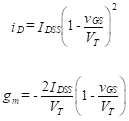

2.2 Išeikvojimo režimo MOSFET

Ankstesnė dalis buvo susijusi su patobulinimo režimu MOSFET. Dabar tai palyginame su išeikvojimo režimu MOSFET. Už n-kanalo patobulinimo režimas, norėdami gauti kanalą, turėjome ant vartų pritaikyti teigiamą įtampą. Ši įtampa turėjo būti pakankamai didelė, kad priverstų pakankamai judriųjų elektronų generuoti srovę indukuotame kanale.

9 pav. Išeikvojimo režimas n-channel MOSFET

Lauke n-kanalo išeikvojimo režimo MOSFET, mums nereikia šios teigiamos įtampos, nes turime fiziškai implantuotą kanalą. Tai leidžia mums turėti srovę tarp nutekėjimo ir šaltinio gnybtų, net jei vartams yra neigiama įtampa. Žinoma, yra ribota neigiamos įtampos, kuri gali būti taikoma vartams, kiekis, o srovė teka tarp kanalizacijos ir šaltinio. Ši riba vėl identifikuojama kaip slenkstinė įtampa, VT. Patobulinimo režimo pasikeitimas yra tas, kad vartų ir šaltinio įtampa dabar gali būti neigiama arba teigiama, kaip parodyta 9 paveiksle.

Lygtys, apibrėžiančios išeikvojimo režimo MOSFET veikimą, yra labai panašios į patobulinimo režimo lygtis. Nutekėjimo srovės vertė kai vGS yra nulis identifikuojamas kaip IDSS. Tai dažnai vadinama nutekėjimo šaltinio prisotinimo srovėArba nulis – vartų nutekėjimo srovė. Palyginus patobulinimo režimo MOSFET lygtis su išeikvojimo režimo lygtimis, randame

![]()

(10)

Tada randame,

(11)

Išeikvojimo režimo MOSFET yra atskira forma arba jie gali būti pagaminti integrinių grandynų lustuose kartu su patobulinimo režimo tipais. Tai apima abu p-tipo ir n-tipas. Tai suteikia daugiau lankstumo grandinės projektavimo metodams.

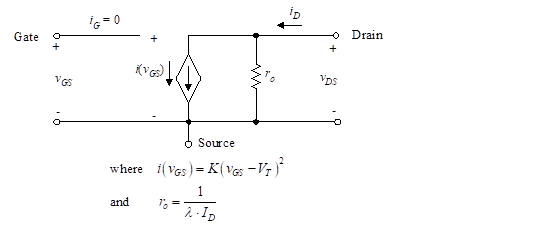

2.3 Didelio signalo ekvivalentinė grandinė

Dabar norime sukurti lygiavertę grandinę, kuri atspindėtų 8 paveiksle [(5) arba (8) lygtis] parodytas didelio signalo charakteristikas soties srityje. Atkreipkite dėmesį, kad išleidimo srovė, iD, priklauso nuo vGS ir vDS. Esant pastoviai vartų ir šaltinio įtampai, mes veikiame pagal vieną iš parametrinių figūros kreivių, o ryšys yra maždaug tiesi. Tiesus ryšys tarp srovės ir įtampos modeliuojamas rezistoriumi. Todėl lygiavertę grandinę sudaro lygiagrečiai su srovės šaltiniu esantis rezistorius, kur srovės šaltinio vertė nustato nutekėjimo srovės dalį dėl vGS. Kreivės nuolydis priklauso nuo vGS. Nuolydis yra dalinė išvestinė,

![]()

(12)

kur r0 yra prieauginė išėjimo varža. Iš [ (5) arba (8)] lygties matome, kad šis pasipriešinimas yra pateiktas pagal

![]()

(13)

kur vartojame didžiąsias raides VGS parodyti, kad varža yra apibrėžta tam tikrai pastoviai vartų ir šaltinio įtampos vertei. Galutinis (13) lygties aproksimavimas gaunamas iš (5) lygties, darant prielaidą, kad λ yra mažas. Todėl varža yra atvirkščiai proporcinga poslinkio srovei, ID. Tada didelio signalo ekvivalento modelis pateikiamas 11 paveiksle, kur r0 yra kaip išplėtota (13) lygtyje.

11 pav. Didelio signalo ekvivalento grandinė

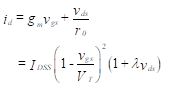

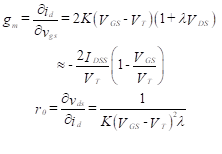

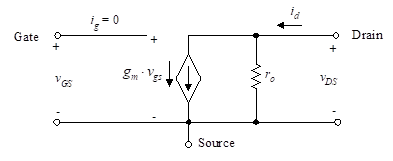

2.4 MOSFET mažo signalo modelis

Dabar norime pažvelgti į didėjančius efektus, susijusius su lygtimi. Trys grandinės parametrai toje lygtyje, iD, vGS ir vDS susideda iš abiejų dc (šališkumas) ir ac komponentai (todėl išraiškose naudojome didžiąsias raides). Mus domina ac mažo signalo modelio komponentai. Matome, kad nutekėjimo srovė priklauso nuo dviejų įtampų – nuo vartų iki šaltinio ir nuo nutekėjimo į šaltinį. Prieauginėms reikšmėms šį ryšį galime parašyti kaip

(14)

Lygtyje (14) gm is priekinis translaidumas ir r0 yra išėjimo varža. Jų reikšmės randamos imant dalines išvestines (5) lygtyje. Taigi,

(15)

Aproksimacija (15) lygtyje atsiranda dėl stebėjimo, kad λ jei mažas. (14) lygtis veda į 12 paveikslo mažų signalų modelį.

12 pav. Mažo signalo MOSFET modelis

SROVĖ – 2. Metalo oksido puslaidininkinis FET (MOSFET)

SROVĖ – 2. Metalo oksido puslaidininkinis FET (MOSFET) ANKSTESNĖ- 1. AKT privalumai ir trūkumai

ANKSTESNĖ- 1. AKT privalumai ir trūkumai