7. Model FET untuk Simulasi Komputer

Model FET untuk Simulasi Komputer

SPICE dan MICRO-CAP mengandungi model canggih untuk JFET dan MOSFET. Model JFET (yang SPICE Model 2G.6) mengandungi parameter 12. MOSFET SPICE Model mengandungi parameter 42 dalam tiga tahap. Model tahap terendah mengandungi parameter 25, manakala model pesanan lebih tinggi menambah ke senarai ini. MICRO-CAP parameter 10 tambahan kepada model MOSFET untuk membawa jumlahnya kepada 52. Lebih banyak parameter yang digunakan model, lebih dekat hasil simulasi adalah untuk operasi peranti sebenar. Walau bagaimanapun, lebih banyak parameter dalam model, semakin perlahan simulasi.

Sebab terdapat begitu banyak parameter adalah bahawa model ini cuba meniru lengkung operasi tidak linier peranti ini. Komputer mampu mengesan lebih banyak detail daripada yang kita dapat dengan tangan, jadi modelnya dapat lebih canggih daripada yang kita gunakan untuk penyelesaian "kertas". Dalam banyak situasi analisis, anda akan menetapkan sebahagian besar parameter model ke nilai lalai mereka dan model kompleks ini berkelakuan hampir sama dengan model ringkas yang telah kita bincangkan. Semasa kita berbincang SPICE dalam Lampiran teks ini, kami akan mengkaji semula sintaks dengan cepat untuk memasukkan JFET atau MOSFET dalam litar. The SPICE pernyataan untuk JFET adalah bentuk,

Jname nd ng model ns [kawasan] [OFF] [IC = vds [, vgs]]

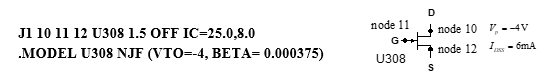

Kurungan persegi menunjukkan bahawa kuantiti adalah pilihan. Sebagai contoh, anda mungkin termasuk pernyataan,

10, 11 dan 12 dalam pernyataan pertama adalah nombor node untuk longkang, pintu, dan sumber. U308 adalah nama model. Kawasan, yang secara lalai menjadi perpaduan, mengalikan atau membahagi parameter untuk model. Arahan “OFF” mematikan JFET untuk titik operasi pertama. “IC” menetapkan syarat awal untuk tegangan drain-to-source dan gate-to-source. Keadaan awal hanya digunakan untuk analisis sementara. Pernyataan kedua digunakan untuk menentukan peranti yang mempunyai nama U308 sebagai n- JFET saluran dengan Vp (VTO) ditetapkan kepada -4V dan K(BETA) bersamaan dengan K = IDSS/VP2. Untuk p-channel JFET menggunakan penunjuk PJF bukan NJF dan tetapkan parameter VTO dan BETA untuk memadankan p-lain saluran.

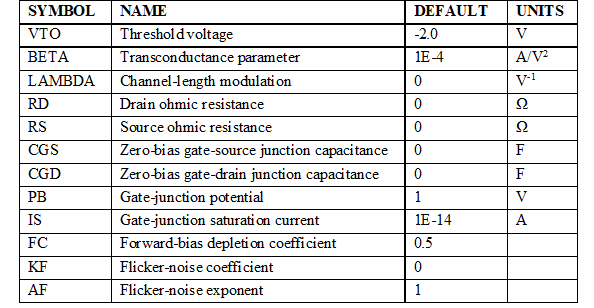

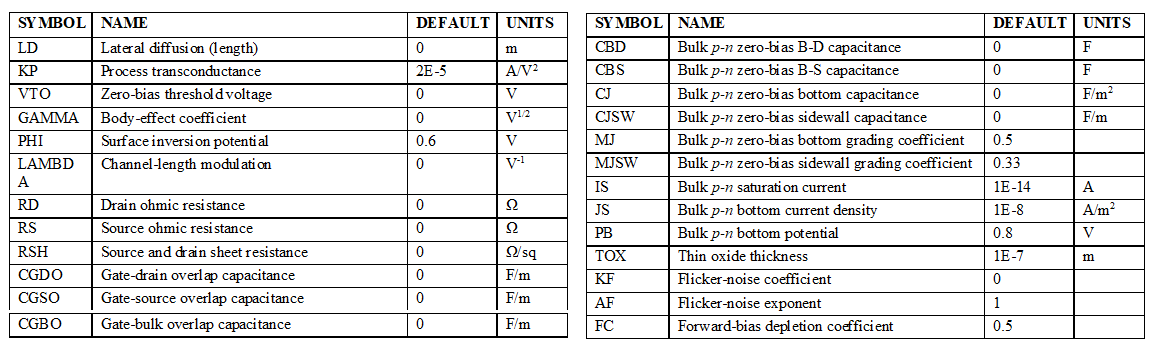

Jadual berikut menyenaraikan parameter 12 dalam model simulasi komputer. Ia juga menunjukkan nilai dan unit lalai bagi setiap parameter.

Jadual 2 - SPICE Parameter JFET

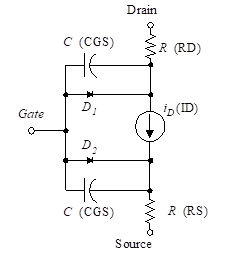

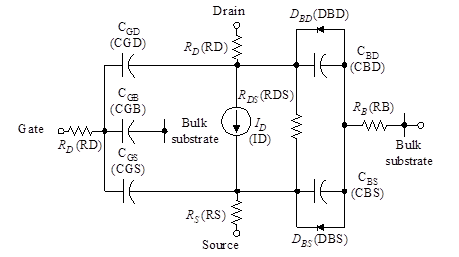

Model yang dikaitkan dengan parameter ini ditunjukkan dalam Rajah 29.

. SPICE Model MOSFET adalah lebih kompleks daripada JFET. Tahap terendah (tahap 1) mengandungi parameter 25 yang terperinci dalam Jadual 3. The SPICE pernyataan adalah dalam bentuk:

Mname nd ng ns nbnamename

+ [L = panjang] [W = lebar] [AD = drainarea] [AS = sourcearea]

+ [PD = drainperiphery] [PD = sourceperiphery] [NRD = drainsquares]

+ [NRS = sourcesquares] [NRG = gatesquares] [NRB = bulksquares]

+ [OFF] [IC = vds] [, vgs [, vbs]]]

(29)

(29)

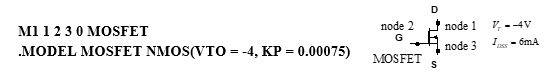

Kurungan persegi menunjukkan bahawa kuantiti adalah pilihan. Sebagai contoh, anda mungkin termasuk pernyataan,

Contoh ini menentukan nombor nod 1,2,3 dan 0 untuk longkang, pintu, sumber, dan badan peranti. Perhatikan bahawa KP = 2K (= 2IDSS/VP2). Gunakan PMOS untuk p-galan bukan NMOS dalam kenyataan kedua.

Parameter, nilai dan unit lalai mereka diberikan dalam Jadual 3. Model yang dikaitkan dengan parameter ini ditunjukkan dalam Rajah 30.

Rajah 30 - Model transistor MOSFET

SEMASA - 7. Model FET untuk Simulasi Komputer

SEMASA - 7. Model FET untuk Simulasi Komputer PREVIOUS- 6. Perbandingan MOSFET kepada JFET

PREVIOUS- 6. Perbandingan MOSFET kepada JFET