2. Penguat Pembalik

Penguat Penyerapan

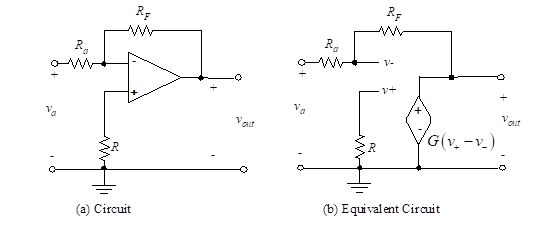

Rajah 3- Op-amp terbalik

Rajah 3 (a) menggambarkan penguat terbalik dengan maklum balas, dan Rajah 3 (b) menunjukkan litar setara untuk litar op-amp pembalik ideal ini. Kami telah menggunakan sifat op-amp yang ideal untuk memodelkan input op-amp sebagai litar terbuka. Sumber terkawal adalah Gvd, tetapi di bawah andaian yang diberikan, kami tidak perlu menggunakan maklumat ini dengan jelas. Kami ingin menyelesaikan untuk voltan output, vkeluar, dari segi voltan input, va. Kami menulis persamaan untuk v+ and v- dan kemudian tetapkan ungkapan-ungkapan ini sama dengan satu sama lain. Sejak semasa melalui R adalah sifar,

(12)

Juga persamaan nod Kirchhoff di v- hasil,

(13)

Sejak v+ = v- and v+ = 0, kemudian v- juga sifar. Oleh itu, kita mempunyai satu persamaan dalam dua tidak diketahui, va and vkeluar, jadi kita boleh selesaikan untuk keuntungan gelung tertutup seperti,

(14)

Perhatikan bahawa keuntungan gelung tertutup, vkeluar /va, adalah negatif (terbalik) dan hanya bergantung pada nisbah dua perintang, RF /Ra. Ia adalah bebas daripada keuntungan gelung terbuka yang sangat tinggi, G. Hasil yang diingini ini disebabkan oleh penggunaan maklum balas sebahagian daripada voltan output untuk menolak dari voltan masukan. Maklum balas daripada output ke input melalui RF berfungsi untuk menggerakkan voltan pembezaan, vd = v+ - v-, dekat dengan sifar. Oleh kerana voltan input tidak terbalik, v+, sifar, maklum balas mempunyai kesan memandu v- kepada sifar. Oleh itu, pada input op-amp,

(15)

Tidak kira betapa rumit litar op-amp yang ideal, dengan mengikuti prosedur mudah ini jurutera dapat menganalisis dengan cepat (dan tidak lama lagi mereka bentuk) sistem op-amp.

Sekarang kita boleh memperluaskan hasil ini kepada kes multiple input.

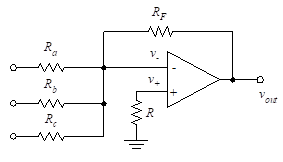

Rajah litar 4- Op-amp

Penguat yang ditunjukkan dalam Rajah (4) menghasilkan output yang merupakan penjumlahan negatif bagi beberapa voltan masukan.

Sejak semasa melalui R adalah sifar, v+ = 0. Persamaan nod pada terminal input terbalik diberikan oleh Persamaan (16):

(16)

Sejak v+ = v-, Maka v+ = 0 = v- dan kita dapati vkeluar dari segi input seperti berikut:

(17)

Pelanjutan untuk n input adalah mudah.

APLIKASI

Analisis litar berikut menggunakan dengan simulator litar TINACloud untuk menentukan Vkeluar dari segi tegangan input dengan mengklik pautan di bawah.

SEMASA - 2. Penguat terbalik

SEMASA - 2. Penguat terbalik PREVIOUS- 1. Op-amp ideal

PREVIOUS- 1. Op-amp ideal