7. Aplikasi Op-amp lain

Aplikasi op-amp lain

Kami telah melihat bahawa op-amp boleh digunakan sebagai penguat, atau sebagai cara menggabungkan beberapa input dalam cara linear. Kami kini menyiasat beberapa aplikasi penting tambahan IC linier serba boleh ini.

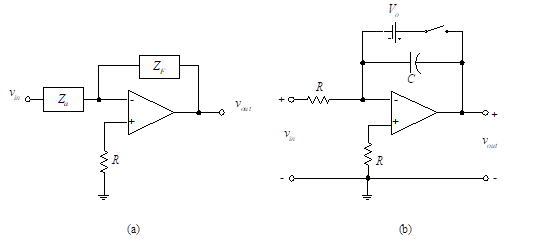

Litar Impedansi Negatif 7.1

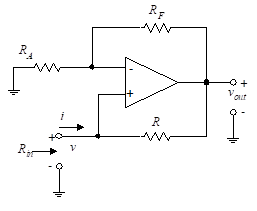

Litar yang ditunjukkan dalam Rajah (17) menghasilkan rintangan input negatif (impedans dalam kes umum).

Litar ini boleh digunakan untuk membatalkan rintangan positif yang tidak diingini. Banyak aplikasi pengayun bergantung kepada litar op-amp rintangan negatif. Rintangan masukan, Rin, ialah nisbah voltan input kepada arus.

![]()

(43)

Hubungan pembahagi voltan digunakan untuk memperoleh ungkapan untuk v- kerana semasa ke dalam op-amp adalah sifar.

![]()

(44)

Kita sekarang biarkan v+ = v- dan selesaikan vkeluar dari segi vin, yang menghasilkan,

![]()

(45)

Sejak input impedans ke v+ terminal adalah tak terhingga, semasa dalam R adalah sama dengan iin dan boleh didapati seperti berikut:

![]()

(46)

Rintangan masukan, Rin, kemudian diberikan oleh

![]()

(47)

Persamaan (47) menunjukkan bahawa litar Rajah (17) menghasilkan rintangan negatif. Jika R digantikan dengan suatu impedans, Z, litar ini menghasilkan impedans negatif.

PERMOHONAN

Menganalisis litar berikut secara online dengan simulator litar TINACloud dengan mengklik pautan di bawah.

Simulasi Litar Impedansi Negatif 1

7.2 Dependent-Current Generator

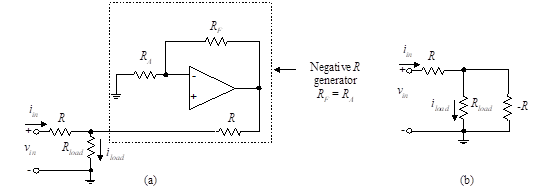

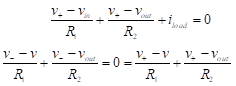

Rajah 18 - Penjana semasa bergantung

Katakan kita biarkan RF = RA. Persamaan (47) kemudian menunjukkan bahawa rintangan masukan ke litar op-amp (tertutup dalam kotak putus-putus) adalah -R. Litar input kemudiannya boleh dipermudahkan seperti ditunjukkan dalam Rajah 18 (b). Kami ingin mengira imemuatkan, semasa dalam Rmemuatkan. Walaupun rintangannya negatif, undang-undang Kirchhoff yang normal masih berlaku kerana tiada apa pun dalam turunannya yang menganggap perintang positif. Arus input, iin, kemudiannya didapati dengan menggabungkan rintangan ke dalam perintang tunggal, Rin.

![]()

(48)

Kami kemudian memohon nisbah pembahagi semasa kepada perpecahan semasa antara Rmemuatkan dan -R kepada mendapatkan

![]()

(49)

Oleh itu, kesan penambahan litar op-amp adalah untuk membuat arus dalam beban yang berkadar dengan voltan masukan. Ia tidak bergantung kepada nilai rintangan beban, Rmemuatkan. Oleh itu, semasa ini adalah bebas daripada perubahan rintangan beban. Litar op-amp secara berkesan membatalkan rintangan beban. Oleh kerana semasa adalah bebas daripada beban tetapi hanya bergantung kepada voltan masukan, kita memanggil ini a penjana semasa (atau penukar voltan ke semasa).

Antara banyak aplikasi litar ini ialah dc sumber voltan terkawal. Jika kita membiarkannya vin = E (pemalar), semasa melalui Rmemuatkan adalah tetap bebas daripada variasi Rmemuatkan.

PERMOHONAN

Menganalisis litar berikut secara online dengan simulator litar TINACloud dengan mengklik pautan di bawah.

Simulasi Circuit Penjana semasa 2-

7.3 Pengubah Semasa-ke-Voltan

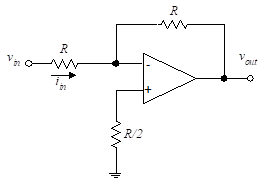

Rajah 19 - Penukar arus-ke-Voltan

Litar Rajah (19) menghasilkan voltan keluaran yang sebanding dengan arus input (ini juga dapat dilihat sebagai a penguat penyambung perpaduan). Kami menganalisis litar ini dengan menggunakan sifat op-amp yang ideal. Kami menyelesaikan voltan di terminal input untuk dicari

![]()

(50)

Oleh itu, voltan keluaran, vkeluar = -iinR, adalah berkadar dengan arus input, iin.

PERMOHONAN

Menganalisis litar berikut secara online dengan simulator litar TINACloud dengan mengklik pautan di bawah.

3- Semasa ke Voltage Converter Circuit Simulation

Penukar Voltage-to-Current 7.4

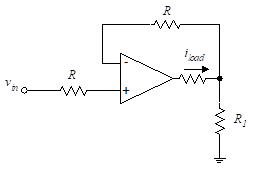

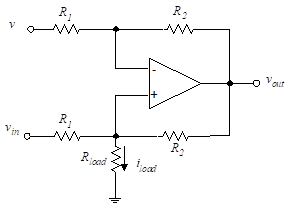

Rajah 20 - Voltan kepada penukar semasa

Litar Rajah (20), adalah penukar voltan ke semasa. Kami menganalisis litar ini seperti berikut:

![]()

(51)

Dari Persamaan (51) kita dapati,

![]()

(52)

Oleh itu, arus beban bebas daripada perintang beban, Rmemuatkan, dan berkadaran dengan voltan yang digunakan, vin. Litar ini menghasilkan sumber arus terkawal voltan. Walau bagaimanapun, kelemahan praktikal litar ini adalah bahawa kedua-dua penghantar beban tidak dapat dibubarkan.

Rajah 21 - Penukar voltan ke semasa

Kami menganalisis litar ini dengan menulis persamaan nod seperti berikut:

(53)

Kesamaan terakhir menggunakan hakikat bahawa v+ = v-. Terdapat lima tidak diketahui dalam persamaan ini (v+, vin, vkeluar, v, dan imemuatkan). Kami menghapuskan v+ and vkeluar untuk mendapatkan,

![]()

(54)

Arus beban, imemuatkan, bebas daripada beban, Rmemuatkan, dan hanya fungsi perbezaan voltan, (vin - v).

PERMOHONAN

Menganalisis litar berikut secara online dengan simulator litar TINACloud dengan mengklik pautan di bawah.

4-Voltage to Current Circuit Simulation

7.5 Inverting Amplifier dengan Impeden Umum

Rajah 22 - Penggunaan galangan umum sebagai ganti rintangan

Hubungan Persamaan (17) mudah diperluas termasuk komponen non-resistif jika Rj digantikan dengan suatu impedans, Zj, dan RF digantikan oleh ZF. Untuk input tunggal, seperti yang ditunjukkan dalam Rajah 22 (a), output akan berkurangan kepada

![]()

(55)

Oleh kerana kita berurusan dengan domain kekerapan, kita menggunakan huruf besar untuk voltan dan arus, dengan itu mewakili amplitud kompleks.

Satu litar berguna berdasarkan Persamaan (55) ialah Penyepadu Miller, seperti yang ditunjukkan dalam Rajah 22 (b). Dalam aplikasi ini, komponen maklum balas adalah kapasitor, C, dan komponen input adalah perintang, R, Jadi

![]()

(56)

Dalam Persamaan (56), s adalah pengendali transform Laplace. Untuk isyarat sinusoidal, ![]() . Apabila kita menggantikan impedans ke Persamaan (55), kita dapati

. Apabila kita menggantikan impedans ke Persamaan (55), kita dapati

![]()

(57)

Dalam domain frekuensi kompleks, 1 / s sesuai dengan integrasi dalam domain masa. Ini adalah penyongsang integrator kerana ungkapan mengandungi tanda negatif. Oleh itu voltan keluaran adalah

![]()

(58)

di mana vkeluar(0) adalah keadaan awal. Nilai vkeluar dibangunkan sebagai voltan merentasi kapasitor, C, pada masa t = 0. Suis ditutup untuk mengecas kapasitor ke voltan vkeluar(0) dan kemudian di t = 0 suis terbuka. Kami menggunakan suis elektronik, yang dibincangkan dengan lebih lengkap dalam Bab 16. Sekiranya keadaan awal sifar, suis masih digunakan untuk menetapkan semula integrator kepada sifar voltan keluaran pada masa t = 0.

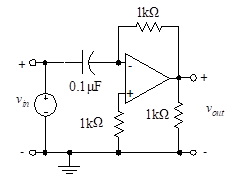

Gambar 23 - Contoh pembeza terbalik

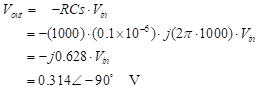

Jika elemen umpan balik adalah perintang, dan elemen masukan adalah kapasitor, seperti ditunjukkan dalam Rajah (23), hubungan input-output menjadi

![]()

(59)

Dalam domain waktu, ini menjadi

![]()

(60)

PERMOHONAN

Menganalisis litar berikut secara online dengan simulator litar TINACloud dengan mengklik pautan di bawah.

5 - Contoh satu simulasi Circuit Simulator yang terbalik

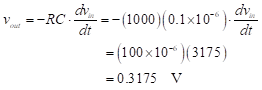

Litar ini beroperasi sebagai pembalik pembezaan. Perhatikan bahawa kapasitor input, Za = 1 / sC, tidak menyediakan jalan untuk dc. Ini tidak menjejaskan hasilnya kerana terbitan konstan adalah sifar. Untuk kesederhanaan, mari kita gunakan isyarat input sinusoidal. Persamaan Pengaturan semula (59) dan penggantian nilai numerik untuk litar ini, kita dapati

(61)

Voltan input terbalik (peralihan 180) oleh litar ini dan kemudian dipertingkatkan dan dialihkan lagi (90 ° oleh j-operator) dengan nilai RC di mana ![]() .

.

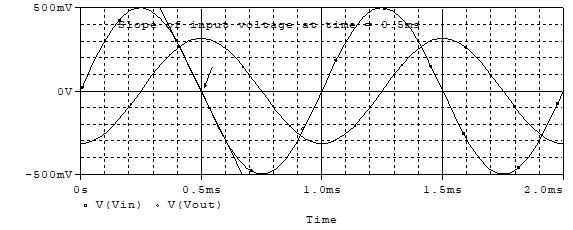

Keputusan simulasi ditunjukkan dalam Rajah (24).

Rajah 24 - Hasil simulasi untuk pembalik pembezaan

Puncak gelombang input pada voltan 0.5. Voltan keluaran mempunyai peralihan bersih (kelewatan) darjah 90 dan puncak voltan keluaran pada kira-kira voltan 0.314. Ini adalah persetujuan yang baik dengan hasil Persamaan (61).

Kita juga boleh menggunakan bentuk gelombang untuk menunjukkan bahawa litar ini melakukan tugas pembeza pembalikkan. Kami akan mengesahkan bahawa bentuk gelombang output mewakili cerun masa isyarat input yang berterusan. Pemalar adalah keuntungan voltan litar. Kadar perubahan voltan input terbesar terjadi pada persimpangan sifar. Ini sepadan dengan masa bahawa bentuk gelombang output mencapai maksimum (atau minimum). Memilih titik perwakilan, katakan pada masa0.5 ms, dan menggunakan teknik grafik, kita mengira cerun gelombang voltan input sebagai

![]()

(62)

Meningkatkan kadar perubahan ini (iaitu,![]() ) dengan keuntungan voltan litar mengikut Persamaan (60) kita menjangkakan voltan keluaran puncak

) dengan keuntungan voltan litar mengikut Persamaan (60) kita menjangkakan voltan keluaran puncak

(63)

Aplikasi Computer Analog 7.6

Dalam bahagian ini kita membentangkan penggunaan litar op-amp yang saling berkaitan, seperti musim panas dan integrator, untuk membentuk komputer analog yang digunakan untuk menyelesaikan persamaan pembezaan. Banyak sistem fizikal digambarkan oleh persamaan kebezaan linier, dan oleh itu sistem boleh dianalisis dengan bantuan komputer analog.

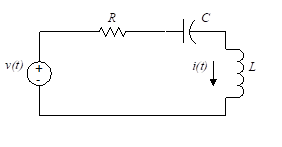

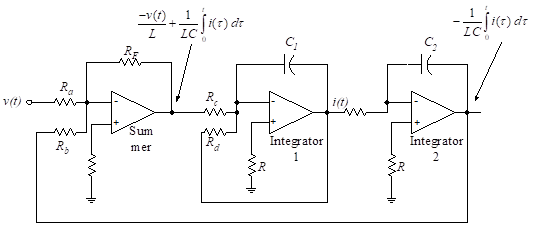

Gambar 25 - Aplikasi komputer analog

Marilah kita selesaikan semasa, i (t), dalam litar Rajah 25. Voltan input adalah fungsi memandu dan keadaan awal adalah sifar. Kami menulis persamaan kebezaan untuk litar seperti berikut:

![]()

(64)

Sekarang menyelesaikan untuk di / dt, kita dapati

![]()

(65)

Kami tahu bahawa untuk t> 0,

![]()

(66)

Dari Persamaan (65) kita melihat bahawa -di / dt dibentuk dengan menjumlahkan tiga syarat, yang terdapat pada Rajah 26 pada input ke penguat yang mengintegrasikan pertama.

Gambar 26 - Penyelesaian komputer analog untuk Rajah 25

Ketiga terma dijumpai seperti berikut:

1. Fungsi pemanduan, -v (t) / L, dibentuk dengan lulus v (t) melalui musim panas (Summer) dengan keuntungan, 1 / L.

2. Ri / L dibentuk dengan mengambil output penguat terintegrasi pertama (Integrator 1) dan menambahkannya pada input penguat kepada output penguat penjumlahan (Summer).

3. Istilah ini

![]()

(67)

adalah output integrator kedua (Integrator 2). Oleh kerana tanda mesti diubah, kita saksikan dengan keuntungan perpaduan yang membalikkan musim panas (Musim Panas).

Keluaran integrator pertama ialah + i, seperti yang dilihat dari Persamaan (66). Pemalar dalam persamaan kebezaan ditubuhkan oleh pemilihan yang tepat bagi perintang dan kapasitor komputer analog. Keadaan awal sifar dicapai oleh suis merentasi kapasitor, seperti ditunjukkan dalam Rajah 22 (b).

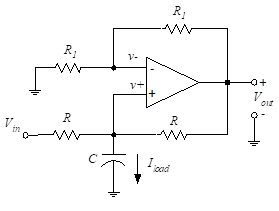

7.7 Non-Inverting Miller Integrator

Gambarajah 27 - Penyepadu bukan penyongsangan

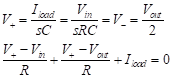

Kami menggunakan pengubahsuaian penjana semasa yang bergantung pada bahagian sebelumnya untuk membangunkan penyepadu bukan penyongsangan. Litar dikonfigurasikan seperti ditunjukkan dalam Rajah 27.

Ini sama dengan litar Rajah 21, tetapi rintangan beban telah digantikan dengan kapasitans. Kami kini mendapati semasa, Iload. Voltan terbalik, V, didapati dari pembahagian voltan antara Vo dan V seperti berikut:

(68)

Oleh kerana V + = V-, kami menyelesaikan dan mencari

IL = Vin / R. Perhatikan bahawa

![]()

(69)

di mana s ialah operator transformasi Laplace. Pada masa itu, fungsi Vout / Vin

![]()

(70)

Oleh itu, dalam domain masa yang kita ada

![]()

(71)

Oleh itu litar adalah penyepadu bukan penyongsangan.

PERMOHONAN

Menganalisis litar berikut secara online dengan simulator litar TINACloud dengan mengklik pautan di bawah.

Simulasi Circuit penyepadu 6-Non-inverting

RINGKASAN

Penguat operasi adalah blok bangunan yang sangat berguna untuk sistem elektronik. Penguat sebenar beroperasi hampir sebagai penguat yang ideal dengan keuntungan yang sangat tinggi dan impedans input hampir tidak terhingga. Atas sebab ini, kita boleh memperlakukannya dengan cara yang sama kita merawat komponen litar. Iaitu, kita dapat memasukkan penguat kepada konfigurasi yang berguna sebelum mengkaji operasi dalaman dan ciri-ciri elektronik. Dengan mengenali ciri terminal, kita dapat mengkonfigurasi penguat dan litar berguna yang lain.

Bab ini bermula dengan analisis penguat operasi yang ideal, dan dengan pembangunan model litar bersamaan menggunakan sumber bergantung. Sumber-sumber bergantung yang kita pelajari awal dalam bab ini membentuk blok bangunan litar setara untuk banyak alat elektronik yang kita pelajari dalam teks ini.

Kami kemudian meneroka sambungan luaran yang diperlukan untuk menjadikan op-amp menjadi penguat terbalik, penguat yang tidak terbalik, dan penguat masukan berganda. Kami membangunkan teknik reka bentuk yang selesa yang menghapuskan keperluan untuk menyelesaikan sistem persamaan serentak yang besar.

Akhir sekali, kita melihat bagaimana op-amp boleh digunakan untuk membina pelbagai litar yang lebih kompleks, termasuk litar yang bersamaan dengan impedans negatif (yang boleh digunakan untuk membatalkan kesan impedans positif), integrator dan pembezaan.

SEMASA - 7. Aplikasi op-amp lain

SEMASA - 7. Aplikasi op-amp lain PREVIOUS- 6. Reka bentuk litar op-amp

PREVIOUS- 6. Reka bentuk litar op-amp