5. Praktikal Op-amp

Praktikal Op-amp

Praktikal Op-amp kira-kira mereka ideal rakan sekerja tetapi berbeza dalam beberapa perkara penting. Adalah penting bagi pereka litar untuk memahami perbezaan antara op-amp sebenar dan op-amp yang ideal, kerana perbezaan ini boleh menjejaskan prestasi litar.

Matlamat kami adalah untuk mengembangkan model terperinci op-amp praktikal - model yang mengambil kira ciri-ciri yang paling ketara dari peranti tidak ideal. Kita mulakan dengan menentukan parameter yang digunakan untuk menggambarkan op-amp praktikal. Parameter ini ditentukan dalam senarai pada lembaran data yang dibekalkan oleh pengeluar op-amp.

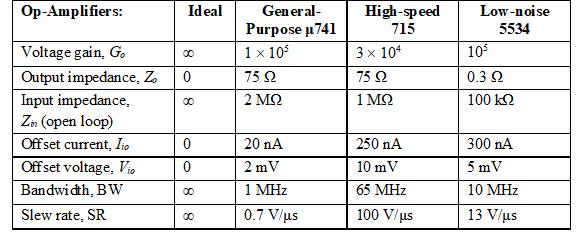

Jadual 1 menyenaraikan nilai parameter untuk tiga op-amp tertentu, salah satu daripada tiga ialah μA741. Kami menggunakan penguat operasi ľA741 dalam banyak contoh dan masalah akhir bab untuk sebab-sebab berikut: (1) mereka telah direka oleh banyak pengeluar IC, (2) mereka didapati dalam kuantiti yang besar di seluruh industri elektronik, dan ( 3) mereka adalah op-amp pampasan dalaman, dan sifat mereka boleh digunakan sebagai rujukan untuk tujuan perbandingan apabila berurusan dengan jenis op-am yang lain. Oleh kerana pelbagai parameter ditakrifkan dalam bahagian berikut, rujukan hendaklah dibuat kepada Jadual 9.1 untuk mencari nilai-nilai tipikal.

Jadual 1 - Nilai parameter untuk op-amp

Perbezaan yang paling ketara antara op-amps yang ideal dan sebenar adalah dalam peningkatan voltan. Op-amp yang ideal mempunyai keuntungan voltan yang mendekati infiniti. Op-amp sebenar mempunyai keuntungan voltan terhingga yang berkurangan apabila kekerapan meningkat (kami meneroka ini secara terperinci dalam bab seterusnya).

5.1 Open-Loop Voltage Gain (G)

Keuntungan voltan gelung terbuka op-amp adalah nisbah perubahan dalam voltan output kepada perubahan dalam voltan input tanpa maklum balas. Keuntungan voltan adalah kuantiti tak berdimensi. Simbol G digunakan untuk menunjukkan keuntungan voltan gelung terbuka. Op-amp mempunyai keuntungan voltan tinggi untuk input frekuensi rendah. Spesifikasi op-amp menyenaraikan peningkatan voltan dalam volt per millivolt atau dalam desibel (dB) [ditentukan sebagai 20log10(vkeluar/vin)].

Model 5.2 Modified Op-amp

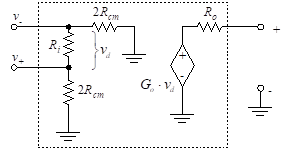

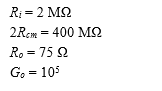

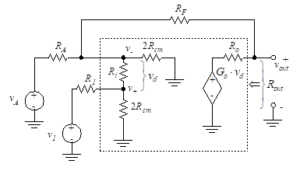

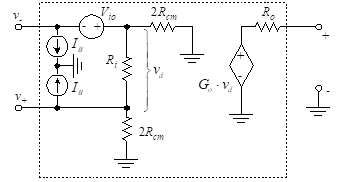

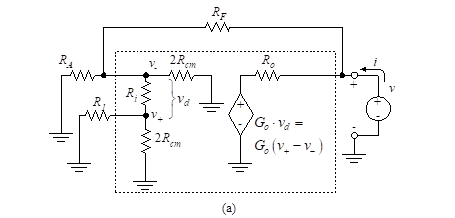

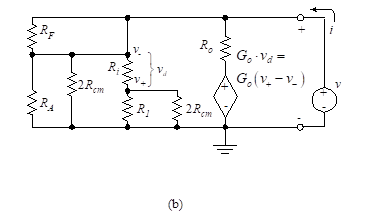

Rajah 14 menunjukkan versi diubahsuai model op-amp yang ideal. Kami telah mengubah model ideal dengan menambah rintangan input (Ri), rintangan output (Ro), dan rintangan mod biasa (Rcm).

Rajah 14 - Model op-amp yang diubahsuai

Nilai biasa parameter ini (untuk op-amp 741) adalah

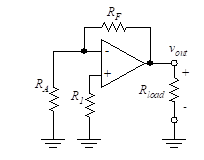

Kami kini mempertimbangkan litar Rajah 15 untuk menilai prestasi op-amp. Input terbalik dan bukan pembalik op-amp didorong oleh sumber-sumber yang mempunyai rintangan siri. Output op-amp disalurkan kembali ke input melalui perintang, RF.

Sumber yang memacu kedua-dua input dinyatakan vA and v1, dan rintangan siri yang berkaitan adalah RA and R1. Jika litar input lebih rumit, rintangan ini boleh dianggap sebagai persamaan Thevenin litar itu.

Rajah 15 - Litar Op-amp

5.3 Input Voltan Offset (Vio)

Apabila voltan input ke op-amp yang ideal adalah sifar, voltan output juga sifar. Ini tidak benar untuk op-amp sebenar. The voltan input input, Vio, ditakrifkan sebagai voltan input pembezaan yang diperlukan untuk membuat voltan output sama dengan sifar. Vio adalah sifar untuk op-amp yang ideal. Nilai tipikal Vio untuk op-amp 741 adalah 2 mV. Nilai bukan sifar Vio adalah tidak diingini kerana op-amp menguatkan sebarang input yang mengimbangi, dengan itu menyebabkan keluaran yang lebih besar dc kesilapan.

Teknik berikut boleh digunakan untuk mengukur voltan mengimbangi input. Daripada mengubah voltan input untuk memaksa output menjadi sifar, input ditetapkan sama dengan sifar, seperti yang ditunjukkan dalam Rajah 16, dan voltan keluaran diukur.

Rajah 16 - Teknik untuk mengukur Vio

Voltan keluaran yang dihasilkan daripada voltan input sifar dikenali sebagai output voltan mengimbangi dc. Voltan mengimbangi input diperoleh dengan membahagikan kuantiti ini dengan keuntungan gelung terbuka op-amp.

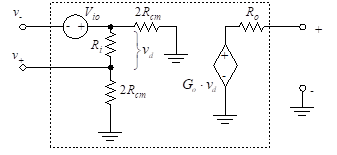

Kesan voltan mengimbangi input boleh dimasukkan ke dalam model op-amp seperti ditunjukkan dalam Rajah 17.

Sebagai tambahan untuk memasukkan voltan mengimbangi input, model op-amp yang ideal telah diubah lagi dengan penambahan sebanyak empat perlawanan. Ro adalah rintangan keluaran. Yang rintangan input daripada op-amp, Ri, diukur antara terminal terbalik dan tidak terbalik. Model ini juga mengandungi perintang yang menghubungkan setiap dua input ke tanah.

Ini adalah rintangan mod biasa, dan masing-masing adalah sama dengan 2Rcm. Jika input disambung bersama seperti dalam Rajah 16, kedua-dua perintang ini selari, dan rintangan Thevenin gabungan ke tanah adalah Rcm. Jika op-amp sesuai, Ri and Rcm pendekatan infiniti (iaitu, litar terbuka) dan Ro adalah sifar (iaitu, litar pintas).

Rajah 17 - Input voltan mengimbangi

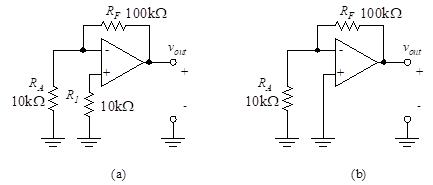

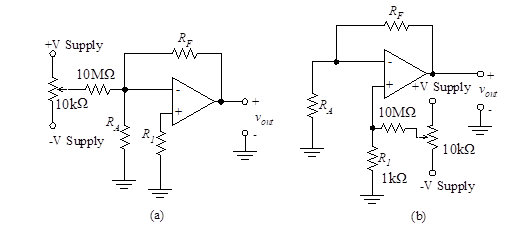

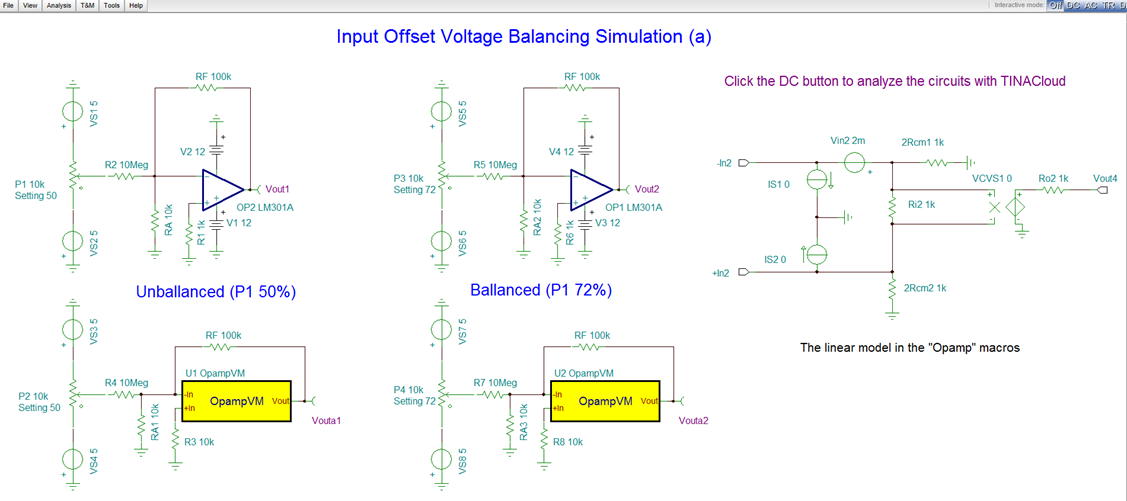

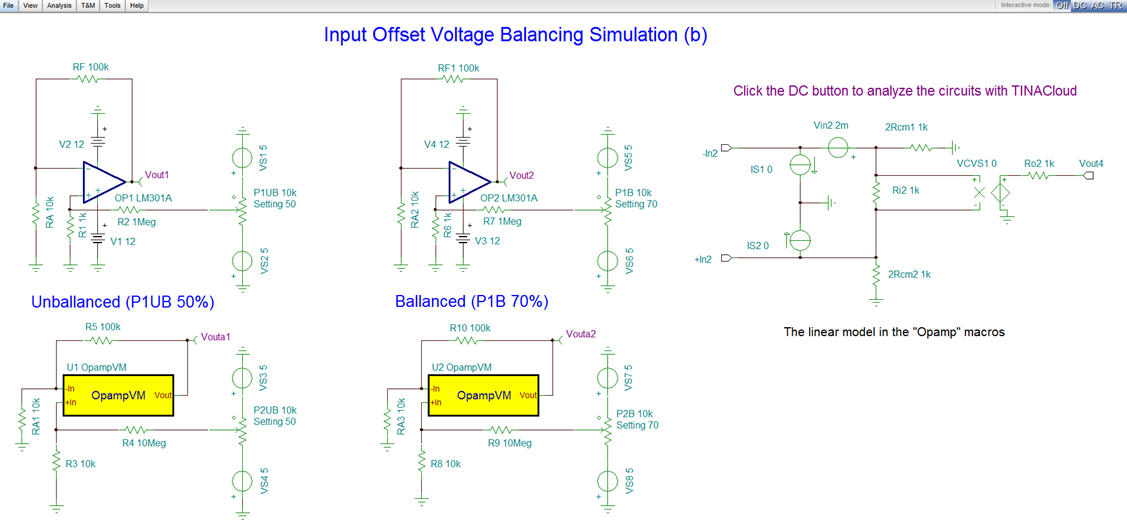

Konfigurasi luaran yang ditunjukkan dalam Rajah 18 (a) boleh digunakan untuk menafikan kesan voltan offset. Voltan berubah-ubah digunakan pada terminal input terbalik. Pemilihan voltan yang betul ini membatalkan input yang diimbangi. Begitu juga, Rajah 18 (b) menggambarkan litar mengimbangi ini yang digunakan untuk input bukan penyongsangan.

Rajah 18 - Pengimbang voltan mengimbangi

PERMOHONAN

Anda boleh menguji Imbangan Voltan Mengimbangi Input dari litar 18 (a) dengan simulasi dalam talian dengan Simulator Litar TINACloud dengan mengklik pautan di bawah.

Input Offset Voltage Balancing Simulation Circuit (a) dengan TINACloud

Input Offset Voltage Balancing Simulation Circuit (a) dengan TINACloud

PERMOHONAN

Anda boleh menguji Imbangan Offset Input litar 18 (b) dengan simulasi dalam talian dengan Simulator Litar TINACloud dengan mengklik pautan di bawah:

Input Offset Voltage Balancing Simulation Circuit (b) dengan TINACloud

Simulasi Circuit Balanced Offset input (b) dengan TINACloud

5.4 Input Bias Semasa (IBias)

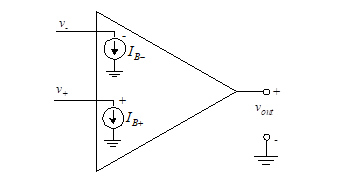

Walaupun input op-amp yang ideal tidak mencatatkan, op-amp sebenar membenarkan beberapa arus bias memasuki setiap terminal input. IBias adalah dc semasa ke dalam transistor masukan, dan nilai tipikal ialah 2 μA. Apabila impedans sumbernya rendah, IBias mempunyai sedikit kesan, kerana ia menyebabkan perubahan yang relatif kecil dalam voltan input. Bagaimanapun, dengan litar memandu tinggi impedans, arus kecil boleh menyebabkan voltan yang besar.

Arus bias boleh dimodelkan sebagai dua tenggelam semasa, seperti ditunjukkan dalam Rajah 19.

Rajah 19 - Pengimbang voltan mengimbangi

Nilai tenggelam ini adalah bebas daripada impedans sumber. The bias semasa didefinisikan sebagai nilai purata dua sinki semasa. Oleh itu

(40)

Perbezaan di antara dua nilai tenggelam dikenali sebagai input mengimbangi semasa, Iio, dan diberikan oleh

(41)

Kedua-dua arus input-bias dan arus mengimbangi input adalah bergantung suhu. The pekali suhu bias input didefinisikan sebagai nisbah perubahan dalam arus bias untuk berubah suhu. Nilai tipikal ialah 10 nA /oC. The input koefisien suhu semasa mengimbangi ditakrifkan sebagai nisbah perubahan magnitud semasa mengimbangi kepada perubahan suhu. Nilai tipikal ialah -2nA /oC.

Rajah 20 - Model semasa bias input

Arus bias input dimasukkan ke dalam model op-amp Rajah 20, di mana kita mengandaikan bahawa arus mengimbangi input diabaikan.

Itu dia,![]()

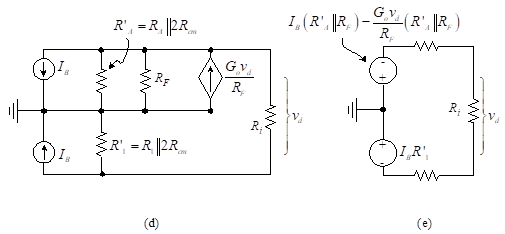

Rajah 21 (a) - Litar

Kami menganalisis model ini untuk mencari voltan keluaran yang disebabkan oleh arus bias input.

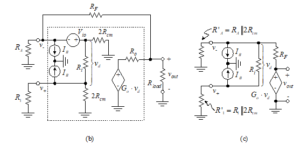

Rajah 21 (a) menunjukkan litar op-amp di mana input pembalikan dan bukan pembalik disambungkan ke tanah melalui rintangan.

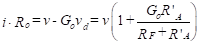

Litar ini digantikan dengan kesamaannya dalam Rajah 21 (b), di mana kita telah diabaikan Vio. Kami selanjutnya memudahkan litar dalam Rajah 21 (c) dengan mengabaikan Ro and Rmemuatkan. Iaitu, kita mengandaikan RF >> Ro and Rmemuatkan >> Ro. Keperluan pemuatan output biasanya memastikan ketidaksamaan ini dipenuhi.

Litar ini selanjutnya dipermudahkan dalam Rajah 21 (d) di mana kombinasi siri sumber voltan dan perintang yang bergantung kepada pengganti digantikan dengan kombinasi selari sumber arus dan perintang yang bergantung.

Akhirnya, kita menggabungkan rintangan dan menukar kedua-dua sumber semasa kembali kepada sumber voltan untuk mendapatkan bersamaan dengan mudah dari Rajah 21 (e).

Rajah 21 (b) dan (c) - Kesan bias input

Kami menggunakan persamaan gelung untuk mencari voltan keluaran.

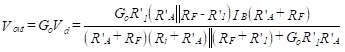

(43)

di mana

(44)

Rintangan mod biasa, Rcm, berada dalam pelbagai ratus megohms untuk kebanyakan op-amp. Oleh itu

(45)

Sekiranya kita menganggapnya lebih lanjut Go adalah besar, Persamaan (43) menjadi Persamaan.

(46)

Rajah 21 (d) dan (e) - Kesan bias input

Ambil perhatian bahawa jika nilai R1 dipilih untuk sama dengan, maka voltan keluaran adalah sifar. Kami menyimpulkan dari analisis ini bahawa dc rintangan dari V+ ke tanah harus sama dengan dc rintangan dari V- ke tanah. Kami menggunakannya keseimbangan bias kekangan banyak kali dalam reka bentuk kami. Adalah penting bahawa kedua-dua terminal terbalik dan tidak berpencar mempunyai a dc jalan ke tanah untuk mengurangkan kesan bias input semasa.

1 Contoh

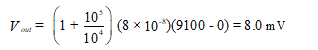

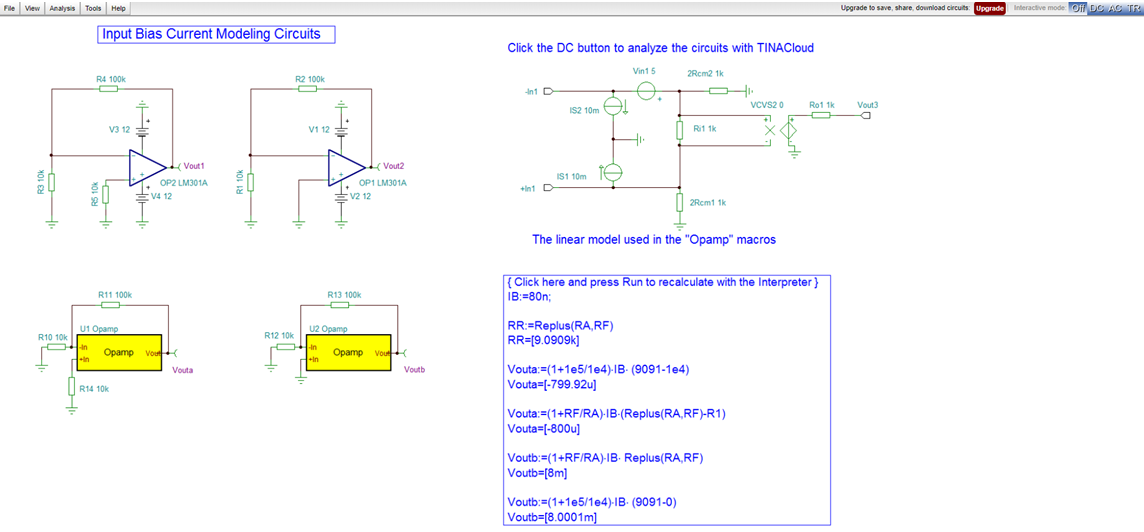

Cari voltan keluaran untuk konfigurasi Rajah 22 di mana IB = 80 nA = 8 10-8 A.

penyelesaian: Kami menggunakan bentuk Persamaan ringkas (46) untuk mencari voltan keluaran untuk litar Rajah 22 (a).

Untuk litar Rajah 22 (b), kita dapati

PERMOHONAN

Juga, anda boleh menjalankan pengiraan ini dengan simulator litar TINACloud, menggunakan alat Interpreternya dengan mengklik pautan di bawah.

Input Bias Simulasi Litar Pemodelan Semasa dengan TINACloud

Input Bias Simulasi Litar Pemodelan Semasa dengan TINACloud

5.5 Penolakan Mod Biasa

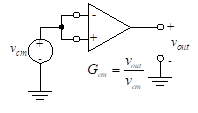

Op-amp biasanya digunakan untuk menguatkan perbezaan antara dua tegangan input. Oleh itu, ia beroperasi di mod pembezaan. Voltan tetap yang ditambahkan pada kedua-dua input ini tidak boleh mempengaruhi perbezaan dan oleh itu tidak boleh dipindahkan ke output. Dalam kes praktikal, nilai input yang tetap atau purata ini tidak menjejaskan voltan keluaran. Jika kita menganggap hanya bahagian yang sama dari dua input, kita sedang mempertimbangkan apa yang dikenali sebagai mod biasa.

Rajah 23 - Mod umum

Marilah kita mengandaikan bahawa terminal input dua op-amp sebenar disambung bersama dan kemudian kepada voltan sumber biasa. Ini digambarkan dalam Rajah 23. Voltan keluaran akan menjadi sifar dalam kes yang ideal. Dalam kes praktikal, output ini tidak sifar. Nisbah voltan output bukan sifar ke voltan masukan yang digunakan ialah keuntungan voltan biasa mod, Gcm. Yang nisbah penolakan mod biasa (CMRR) ditakrifkan sebagai nisbah dc keuntungan gelung terbuka, Go, kepada keuntungan biasa mod. Oleh itu,

(47)

Nilai tipikal CMRR dari 80 ke 100 dB. Adalah wajar untuk mempunyai CMRR setinggi mungkin.

5.6 Nisbah Penolakan Bekalan Kuasa

Nisbah penolakan bekalan kuasa adalah ukuran keupayaan op-amp untuk mengabaikan perubahan dalam voltan bekalan kuasa. Sekiranya peringkat keluaran sistem menarik jumlah arus berubah-ubah, voltan bekalan boleh berubah-ubah. Perubahan beban yang disebabkan oleh voltan bekalan ini kemudiannya boleh menyebabkan perubahan dalam operasi penguat lain yang berkongsi bekalan yang sama. Ini dikenali sebagai bercakap silang, dan ia boleh menyebabkan ketidakstabilan.

. nisbah penolakan bekalan kuasa (PSRR) ialah nisbah perubahan dalam vkeluar kepada jumlah perubahan voltan bekalan kuasa. Sebagai contoh, jika bekalan positif dan negatif berbeza dari ± 5 V hingga ± 5.5 V, jumlah perubahannya adalah 11 - 10 = 1 V. PSRR biasanya ditentukan dalam voltan mikro per volt atau kadang-kadang dalam desibel. Op-amp khas mempunyai PSRR sekitar 30 μV / V.

Untuk mengurangkan perubahan voltan bekalan, bekalan kuasa untuk setiap kumpulan op-amp mestilah dibongkar (iaitu, terpencil) dari kumpulan lain. Ini mengurungkan interaksi kepada satu kumpulan op-amp. Dalam praktiknya, setiap kad litar bercetak harus mempunyai garis bekalan dilangkau ke tanah melalui kapasitor tantalum seramik 0.1-μF atau 1-μF. Ini memastikan bahawa variasi beban tidak akan memberi makan dengan ketara melalui bekalan ke kad lain.

5.7 Rintangan Output

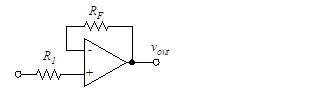

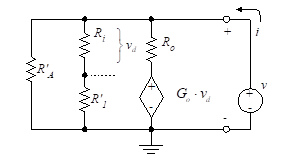

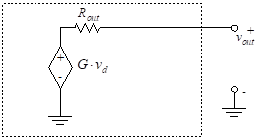

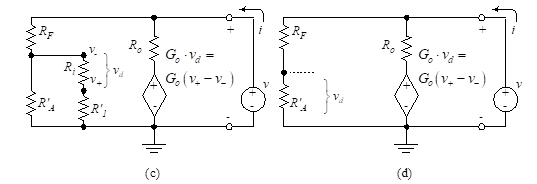

Sebagai langkah pertama dalam menentukan rintangan output, Rkeluar, kita dapati setara Thevenin untuk bahagian litar op-amp yang ditunjukkan dalam kotak yang dilampirkan dalam garisan putus-putus dalam Rajah 24. Perhatikan bahawa kita mengabaikan arus dan voltan mengimbangi dalam analisis ini.

(24)

Oleh kerana litar tidak mengandungi sumber bebas, voltan setara Thevenin adalah sifar, jadi litar setara dengan satu perintang. Nilai perintang tidak dapat dijumpai menggunakan kombinasi perintang. Untuk mencari rintangan yang setara, anggap bahawa sumber voltan, v, diterapkan pada petunjuk output. Kami kemudian mengira arus yang dihasilkan, i, dan ambil nisbah v/i. Ini menghasilkan rintangan Thevenin.

Rajah 25 (bahagian a) - Litar setara Thevenin

Rajah 25 (bahagian b)

Rajah 25 (a) menggambarkan sumber voltan yang digunakan. Litar dipermudahkan kepada yang ditunjukkan dalam Rajah 25 (b).

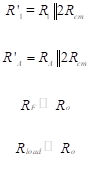

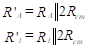

Litar boleh dikurangkan lagi kepada yang ditunjukkan dalam Rajah 25 (c), di mana kita menentukan dua rintangan baru seperti berikut:

(48)

Kami membuat andaian itu R 'A << (R '1 + Ri) dan Ri >> R '1. Litar mudah bagi Rajah 25 (d) hasil.

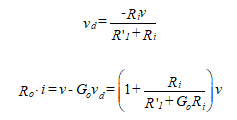

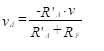

Voltan pembezaan masukan, vd, didapati dari litar mudah ini menggunakan nisbah pembahagi voltan.

(49)

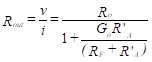

Untuk mencari rintangan output, kita mulakan dengan menulis persamaan gelung keluaran.

(50)

Rajah 25 (bahagian c dan d) - Litar setara Thevenin yang dikurangkan

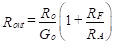

Rintangan output kemudian diberikan oleh Persamaan (51).

(51)

Dalam kebanyakan kes, Rcm begitu besar itu R 'A»RA and R1'»R1. Persamaan (51) boleh dipermudahkan menggunakan keuntungan voltan frekuensi sifar, Go. Hasilnya adalah Persamaan (52).

(52)

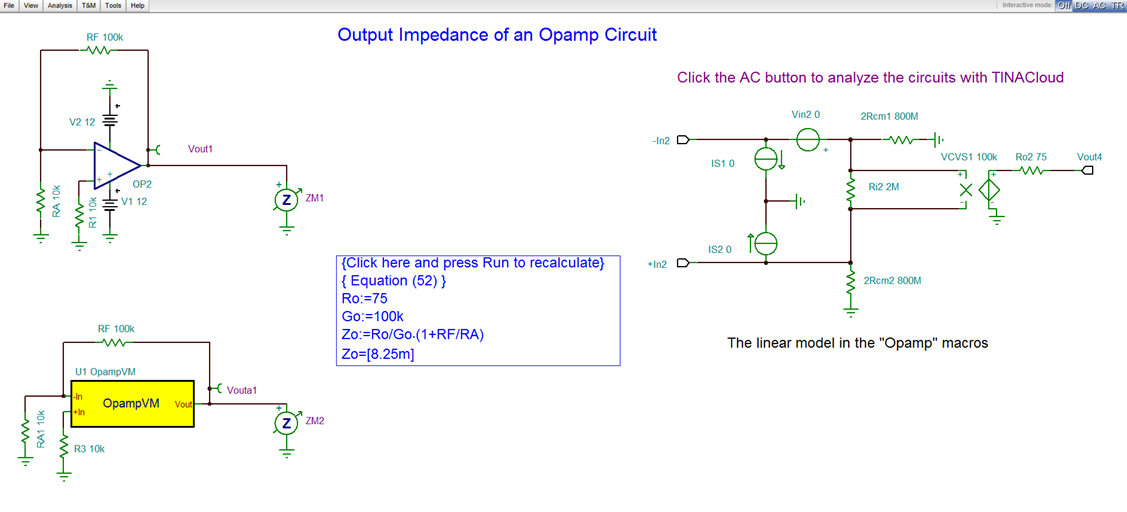

PERMOHONAN

Anda boleh mengira Output Impedance litar 25 (a) dengan simulasi litar menggunakan TINACloud Circuit Simulator dengan mengklik pautan di bawah.

Output Impedance daripada Simulasi Litar Opamp dengan TINACloud

Output Impedance daripada Simulasi Litar Opamp dengan TINACloud

2 Contoh

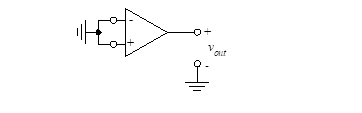

Cari impedans keluaran penampan kesatuan-persamaan seperti yang ditunjukkan dalam Rajah 26.

penyelesaian: Apabila litar Rajah 26 dibandingkan dengan litar umpan balik Rajah 24, kita dapati itu

Oleh itu,

Persamaan (51) tidak boleh digunakan, kerana kita tidak pasti bahawa ketidaksamaan yang membawa kepada penyederhanaan Rajah 25 (c) terpakai dalam kes ini. Iaitu, penyederhanaan memerlukannya

Tanpa penyederhanaan ini, litar mengambil bentuk yang ditunjukkan dalam Rajah 27.

Litar ini dianalisis untuk mencari hubungan berikut:

Dalam persamaan pertama ini, kami telah mengandaikannya Ro<< (R '1+Ri) << 2Rcm. Rintangan keluaran kemudiannya diberikan oleh

Di mana kita sekali lagi menggunakan keuntungan voltan frekuensi sifar, Go.

SEMASA - 5. Op-amp praktikal

SEMASA - 5. Op-amp praktikal SEBELUMNYA- 4. Spesifikasi pengeluar

SEBELUMNYA- 4. Spesifikasi pengeluar