4। FET एम्पलीफायर कन्फिगुरेसन र बिजिङ

FET एम्पलीफायर कन्फिगुरेसन र बिजिङ

BJTs को पूर्वाग्रहका लागि उपयोग गरिएका दृष्टिकोणहरू MOSFETS biasing को लागि पनि प्रयोग गर्न सकिन्छ। हामी एकीकृत सर्किट एम्पलीफायरहरू विरुद्ध विषम घटकका लागि प्रयोग गर्नेहरूलाई ती दृष्टिकोणहरू अलग गर्न सक्दछौं। असंगत घटक डिजाइनहरूले ठूलो युग्मन र प्रत्येक एम्पलीफायर चरणको लागि डीसी पूर्वाग्रहलाई अलग गर्न को लागी क्याप्सेरेटर प्रयोग गर्दछ, धेरै विषम घटक BJT एम्पलीफायरहरू जस्तै। आईसी MOSFET एम्पलीफायर सामान्यतया सीधा युग्मित हुन्छन् किनकी ठूला क्याप्सेरेटर व्यावहारिक छैनन्। आईसी MOSFET एम्पलीफायरहरू सामान्यतया डीसी हालका स्रोतहरू प्रयोग गरेर पूर्वाधारमा छन् जुन तीजहरू हुन् जुन BJT आईसी एम्पलीफायरहरूको लागि प्रयोग गरिन्छ।

4.1 डिस्कोट्री-घटक MOSFET Biasing

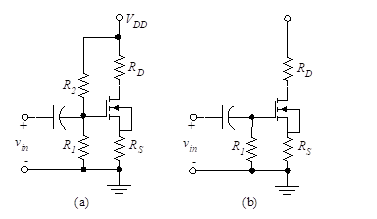

MOSFET एम्पलीफायरहरूको लागि विषम-घटक पूर्वाधार चित्रा 21 मा देखाइएको सर्किटसँग पूरा हुन्छ। गेट-देखि-स्रोत भोल्टेजले ट्रांजिस्टर कन्फिगरेसनको लागि आवश्यक हुन सक्ने सर्किटको प्रकार निर्धारण गर्छ। सुधार मोड ट्रांजिस्टरको लागि, त्यहाँ गेटमा एक सकारात्मक भोल्टेजको लागि सधैँ आवश्यक पर्दछ। भोल्टेज विभाजन पूर्वाग्रहमा, त्यहाँ हुनेछ R1 र R2 सकारात्मक वोल्टेज प्राप्त गर्न। गिरावटका लागि MOSFETs वा JFETs को लागी, R2 केडीई 21 (बी) मा देखाईएको जस्तै, परिमार्जन वा अनन्त हुन सक्छ।

चित्र २१ - एम्प्लीफायर biasing विन्यास

सामान्य स्रोत (सीएस)- यो ac आगत लागू हुन्छ CG, को ac आउटपुट मा लिइएको छ CD, र CS सँग जोडिएको छ dc भोल्टेज स्रोत वा जमीन। यो BJT को लागि आम-एमिटर कन्फिगरेसनमा अनुरूप छ।

-स्रोत रिजर्व (SR) - यो ac आगत लागू हुन्छ CG, को ac आउटपुट मा लिइएको छ CD र CS हटाइएको छ। यो BJT को लागि emitter-resistor विन्यास को अनुरूप छ।

-साधारण गेट (सीजी) - यो ac आगत लागू हुन्छ CS, को ac आउटपुट मा लिइएको छ CD र CG सँग जोडिएको छ dc भोल्टेज स्रोत वा जमीन। कहिलेकाहीँ सीजी कन्फिगरेसनमा, CG लुकाइएको छ र ढोका सीधा जोडिएको छ dc भोल्टेज आपूर्ति। सीजी सामान्य BGT को लागि आधार बेस कन्फिगरेसन अनुरूप छ, यद्यपि यो कहिलेकाहीं सर्किटमा देख्न सकिन्छ।

-स्रोत अनुयायी (एसएफ) - यो ac आगत लागू हुन्छ CG, को ac आउटपुट मा लिइएको छ CS र नाली वा एकै जडित छ dc भोल्टेज आपूर्ति प्रत्यक्ष वा मार्फत CD। यो कहिलेकाहीं सामान्य ड्रेन (सीडी) भनिन्छ र BJT को लागि एमिटर अनुयायी विन्यास कन्फिगरेसन हो।

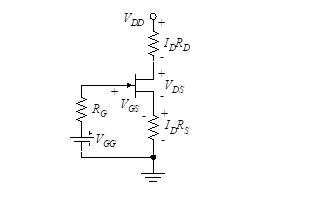

चित्रा 22 - थिभिन समतुल्य सर्किट

यी सबै कन्फिगरेसनहरू सेक्सन,, "FET एम्प्लिफायर विश्लेषण" मा अधिक विस्तृत रूपमा अध्ययन गरिन्छ।

किनकि विभिन्न कन्फिगरेसनहरू केवल क्याप्सेरेटर मार्फत आफ्नो जडानमा भिन्न हुन्छन्, र क्यापकोप्टरहरू खुला सर्किट हुन् dc भोल्टेज र धाराहरू, हामी अध्ययन गर्न सक्छौं dc सामान्य मामला को लागि पूर्वाग्रह। एम्पलीफायर डिजाइनको लागी, हामी ट्रांजिस्टर सक्रिय परिचालन क्षेत्रमा काम गर्न चाहन्छौं (यो पनि संतृप्ति क्षेत्र वा चुन्च बन्द मोडको रूपमा चिनिन्छ), त्यसैले हामी यन्त्रको लागि पिंच-च चतुर्थ विशेषता मान्छौं। (हामीले यस धारणालाई यो डिजाइनको अन्त्यमा सधैँ प्रमाणित गर्नुपर्छ!)

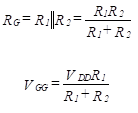

पूर्वाग्रह विश्लेषण को सरल बनाउन को लागि, हामी ट्रांजिस्टर को गेट मा सर्किट को मोडेल को रूप मा चितवन 22 मा दिखाया को रूप मा एक स्वेनिन स्रोत को उपयोग गर्दछ।

(24)

चूंकि पूर्वाग्रहको लागि सेट गर्न तीन अज्ञात चरहरू छन् (ID, VGS, र VDS), हामीलाई तीन चाहिन्छ dc समीकरण। पहिलो, द dc गेटको वरिपरि समीकरण - स्रोत लूप लेखिएको छ।

![]()

(25)

ध्यान दिनुहोस् कि गेट अहिले शून्य छ, एक शून्य भोल्टेज ड्रप भर पर्दछ RG। एक सेकेन्ड dc ड्रेनेस-स्रोत लूपमा किर्चहोफको कानून समीकरणबाट समीकरण फेला पर्दछ।

![]()

(26)

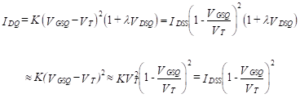

तेस्रो dc पूर्वाधार बिन्दु स्थापित गर्न समीकरण आवश्यक समीकरण (20) बाट फेला पर्यो  सेक्सन "जंक्शन फिल्ड-इफेक्ट ट्रान्जिस्टर (JFET)" जुन यहाँ दोहोर्याइएको छ।

सेक्सन "जंक्शन फिल्ड-इफेक्ट ट्रान्जिस्टर (JFET)" जुन यहाँ दोहोर्याइएको छ।

(27)

पहिलो अनुमानित हुन्छ यदि |λVDS| << १ (जुन प्रायः सँधै सहि हुन्छ) र युग्मित समीकरणहरूको समाधानलाई काफी सरलीकृत गर्दछ।

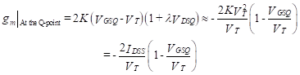

हामी समीकरण गर्न सक्छौं gm [समीकरण (22)]

(22)

एक समान ढाँचामा कि डिजाइनमा उपयोगी साबित हुनेछ।

(28)

समीकरण (25) - (28) पूर्वाग्रह स्थापित गर्न पर्याप्त छन्। असुरक्षित MOSFET एम्पलीफायरहरूका लागि, हामी क्यू-बिन्दुको केन्द्रमा राख्न आवश्यक छैन ac लोड लाइनको रूपमा हामीले प्राय: BJT biasing को लागी गर्नुभयो। यो किनभने किनभने असुरक्षित एफईटी एम्पलीफायर सामान्य रूपमा एम्पलीफायर चेन्जको पहिलो चरणको रूपमा उच्च इनपुट प्रतिरोधको फाइदा लिन प्रयोग गरिन्छ। पहिलो चरणको रूपमा प्रयोग गर्दा वा preamplifier, भोल्टेज स्तर धेरै सानो छ कि हामी ठूलो यात्रामा preamplifier को उत्पादन ड्राइव गर्दैनौं।

CURRENT - F. FET एम्प्लिफायर कन्फिगरेसन र बायसिasing

CURRENT - F. FET एम्प्लिफायर कन्फिगरेसन र बायसिasing PREVIOUS- 3। जंक्शन फिल्ड-प्रभाव ट्रांजिस्टर (JFET)

PREVIOUS- 3। जंक्शन फिल्ड-प्रभाव ट्रांजिस्टर (JFET)