5। MOSFET एकीकृत सर्किट

MOSFET एकीकृत सर्किट

जब MOSFET ट्रांजिस्टर एक एकीकृत सर्किट को भाग को रूप मा बनाइन्छ, व्यावहारिक विचार सर्किट विन्यास मा दुई प्रमुख परिवर्तनहरुको आवश्यकता छ। पहिलो, भ्रामक एम्पलीफायरहरूमा प्रयोग गरिने ठूलो युग्मन र बाईपास क्यापसेन्टरहरू व्यावहारिक रूपमा सर्किटहरूमा सानो आकारको कारणले ढाक्न सक्दैन। हामी यो अचानक प्रत्यक्ष सीमानी एम्पलीफायरहरू फैलेर हामी नजिक छौं।

दोस्रो प्रमुख परिवर्तन यो हो कि हामी बायोगिक सर्किट्री को भाग को रूप मा प्रयोग गरे प्रतिरोधकहरुलाई आसानी देखि नहीं बना सकते। यसको सट्टा, हामी सक्रिय लोडहरू र MOS ट्रांजिस्टरहरू समावेश भएका हालको स्रोतहरू प्रयोग गर्दछौं।

एकीकृत सर्किट NMOS र PMOS circuitry दुवै प्रयोग। CMOS डिजिटल सर्किट्रीमा अधिक सामान्य छ, जबकि NMOS सामान्यतया उच्च घनत्व आईसी (जस्तै, प्रति प्रति अधिक प्रकार्य) को लागि प्रयोग गरिन्छ।

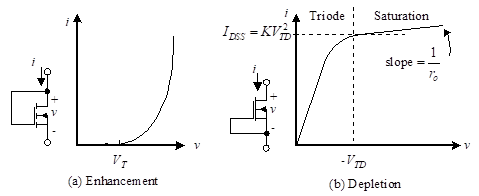

सक्रिय लोड सिमुलेशन एमओएस विशेषता घटाउने ढलानको फाइदा लिन्छ। चित्रा 23 दुई प्रकारको सक्रिय लोडहरू देखाउँछ। चित्रा 23 (ए) मा, हामी NMOS वृद्धि भार देखाउँछौं, जबकि 23 (बी) एक एनएमओएस कमी लोड लोड देखाउँछ। यो पनि आंकडामा देखाइएको प्रासंगिक विशेषता curves हो।

चित्रा 23 - सक्रिय लोड

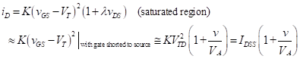

NMOS वृद्धि भारको लागि, भोल्टेज र वर्तमान बीचको सम्बन्ध द्वारा दिइएको छ

![]()

(29)

यस कन्फिगुरेसनको बराबरको प्रतिरोध भनेको 1 /gm, जहाँ ट्रांक्क्रिप्शनको मूल्य भनेको पूर्वाग्रह बिन्दुमा लागू हुन्छ।

एनएमओएस घटाउने भारमा बराबर प्रतिरोध छ जुन निम्न समीकरण द्वारा दिइएको विशेषताको ढलान द्वारा निर्धारित हुन्छ

(30)

5.1 Biasing MOSFET एकीकृत सर्किट

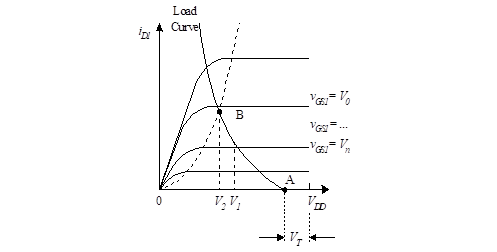

अब हामीसँग सक्रिय लोड अनुकरण गर्न दुई प्रविधिहरू छन्, हामी बाइसेज मुद्दालाई सम्बोधन गर्न सक्छौं। हामी सर्किट कन्फिगरेसनमा लोड प्रतिरोधको स्थानमा सक्रिय लोड प्रयोग गर्छौं। यी विश्लेषणको लागि प्रविधि देखाउनको लागि, हामी एनएनओएस एम्पलीफायरलाई वृद्धि लोडको प्रयोग गरेर विचार गरौं, जस्तै चित्रा 24 मा देखाइएको छ।

ट्रांजिस्टर लेबल गरियो Q2 प्रतिस्थापन गर्दछ RD हाम्रो पहिलेको सर्किट शान्त ऑपरेटिंग पोइन्ट निर्धारण गर्न, हामी हामीले सेक्शन,, "FET एम्प्लिफायर कन्फिगरेसन र बायसिasing" मा गरे जस्तै उही प्रविधिहरू प्रयोग गर्छौं, केवल प्रतिरोधक लोड लाइनको लागि एन्हान्समेन्ट लोड ग्राफिकल विशेषतालाई प्रतिस्थापन गर्दछौं। त्यो हो, हामीले लोड लाइन को समीकरणको साथ FET ट्रान्जिस्टर विशेषताहरूको एकैसाथ समाधान खोज्नु पर्छ। हामी चित्र २ 4 मा देखाइए जस्तै यो चित्रण गर्न सक्छौं।

पैरामीट वक्रहरू एम्पलीफाइन्ट ट्रांजिस्टरका लागि विशेषता वक्रहरू हुन्1। सक्रिय लोड को वर्तमान विशेषता बनाम भोल्टेज, Q2 चित्रा 23 को हुन्। आउटपुट भोल्टेज, vबाहिर, बीचको भिन्नता हो VDD र सक्रिय लोड मा भोल्टेज। सक्रिय लोडमा हाल एक प्रवर्द्धन ट्रांजिस्टरमा नाली जस्तो छ। यसैले हामी चित्रा 23 को विशेषता को स्थानांतरित आईना छवि ले लिएर लोड लाइन को निर्माण गर्छन। परिचालन बिन्दुले यो वक्र को चौर्खा उचित ट्रांजिस्टर विशेषता वक्रको साथ हो। हामीले गेट-देखि-स्रोत भोल्टेजलाई फेला पार्न आवश्यक छ जुन ट्रांजिस्टर वक्र छनौट गर्न जान्दछ। जस्तै हामी अर्को देख्नेछौँ, इनपुट पूर्वाग्रह भोल्टेज अक्सर सक्रिय हालको स्रोतद्वारा प्रतिस्थापित गरिएको छ।

चित्रा 25 - क्यू-बिन्दुको लागि ग्राफिकल समाधान

अब हामी जान्दछौं कि सक्रिय लोड कसरी अनुकरण गर्न, हामी हाम्रो पूर्वाधारलाई वर्तमान स्रोत पूर्वाधार सर्किट्रीरीको भागको रूपमा प्रयोग गर्न सन्दर्भको पीढीमा परिणत गर्दछौं। यी हालका स्रोतहरू प्रयोगमा प्रयोग गरिन्छ जसमा हामीले तिनीहरूलाई प्रयोग गरेका थियौं।

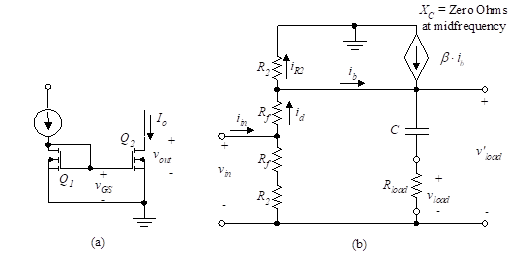

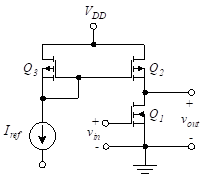

चित्रा 26 - वर्तमान दर्पण

हामी MOSFET का विश्लेषण गर्छौं वर्तमान दर्पण। हालको आईना चित्र 26 मा देखाइएको छ। दुई ट्रांजिस्टरहरू पूर्ण रूपमा मेल खाने अनुमान गरिन्छ। आउटपुट हालको ड्रेन हो Q2, र एक संदर्भ वर्तमान ड्राइव Q1। यदि ट्रान्जिस्टरहरू पूर्ण रूपमा मेल खाए भने, आउटपुट वर्तमान बिल्कुल सन्दर्भ वर्तमान बराबर हुनेछ। यो सत्य हो किनकि ट्रान्जिस्टरहरू समानान्तरमा जडित छन्। जसरी बीज्टको वर्तमान दर्पणको सम्बन्धमा भएको थियो त्यस्तै सन्दर्भ २ Figure (बी) मा देखाइए अनुसार सन्दर्भ प्रतिरोधात्मक पार सन्दर्भ भोल्टेज लागू गरेर सन्दर्भ वर्तमान उत्पन्न गर्न सकिन्छ।

विभिन्न subcircuits (एक साथ, सक्रिय भार र सन्दर्भ वर्तमान) राखेर चित्रा 27 को CMOS एम्पलीफायरमा परिणाम गर्दछ।

यो एम्पलीफायरको लाभ द्वारा दिइएको छ

![]()

(31)

चित्रा 27 - CMOS एम्पलीफायर

5.2 शरीर प्रभाव

सेक्सन "२ को बारेमा हाम्रो छलफल। मेटल-अक्साइड सेमीकन्डक्टर FET (MOSFET) "MOSFET को सब्सट्रेट (वा शरीर) लाई सन्दर्भित गरियो। यस सब्सट्रेटले च्यानल स्थापना गर्न महत्त्वपूर्ण भूमिका खेल्छ। असभ्य MOSFETs को अपरेशनमा, शरीर प्राय: उर्जा स्रोतसँग जोडिएको हुन्छ। त्यस्ता अवस्थाहरूमा सब्सट्रेटले उपकरणको अपरेशनमा कुनै प्रत्यक्ष प्रभाव पार्दैन, र यस अध्यायमा सुरुमा विकास गरिएको कर्भहरू लागू हुन्छन्।

स्थिति परिवर्तन गर्दा MOSFET एकीकृत एकीकृत सर्किट को भाग को रूप मा बनाइन्छ। त्यस्तो अवस्थामा, प्रत्येक ट्रांजिस्टरको सब्सट्रेट अन्य सबस्ट्रेटहरूबाट अलग हुँदैन। वास्तवमा, एक सब्सट्रेट प्राय: सबै MOSFET मा एक चिप मा साझा गरिन्छ। एक PMOS आईसीमा, साझा सब्सट्रेट सबै भन्दा सकारात्मक स्रोत टर्मिनलसँग जडान हुनेछ, जबकि NMOS मा यो जमीन (वा हालैमा नकारात्मक आपूर्तिमा) जडान भएको छ। यो स्रोत र प्रत्येक ट्रांजिस्टर को शरीर को बीच एक पूर्वाग्रह पूर्वाग्रह स्थापित गर्दछ। यस रिवर्स पूर्वाग्रहको प्रभाव परिचालन विशेषताहरू परिवर्तन गर्न हो। उदाहरणका लागि, एक n-च्यानल उपकरण, यसले प्रभावकारी ढंगले थ्रेसहोल्ड (VT)। थ्रेडहोल्ड परिवर्तनले भौतिक परिमितिहरू र यन्त्र निर्माणमा निर्भर गर्दछ। NMOS को लागी, यो परिवर्तन द्वारा सन्न सकिन्छ

![]()

(32)

समीकरणमा (32), γ एक उपकरण प्यारामिटर हो जुन जो 0.3 र 1 बीचको फरक हुन्छ (V-1 / 2). VSB स्रोत बाट शरीर भोल्टेज छ, र छ Fermi क्षमता। यो सामग्रीको सम्पत्ति हो, र एक सामान्य मान सिलिकनका लागी 0.3 V हो।

CURRENT - M. MOSFET एकीकृत सर्किट

CURRENT - M. MOSFET एकीकृत सर्किट PREVIOUS- 4। FET एम्पलीफायर कन्फिगुरेसन र बिजिङ

PREVIOUS- 4। FET एम्पलीफायर कन्फिगुरेसन र बिजिङ