1। विभेदकारी एम्पलीफायरहरू

विभेदकारी एम्पलीफायरहरू

अधिक परिचालन एम्पलीफायरहरु ट्रांजिस्टर, प्रतिरोधक, र एक एकल चिप मा एक पूर्ण प्रणाली बनाउन कैपेसिटर्स को एक श्रृंखला को शामिल हो। आज उपलब्ध एम्पलीफायरहरू विश्वसनीय छन्, सानो आकारमा, र धेरै सानो शक्ति खपत गर्छन।

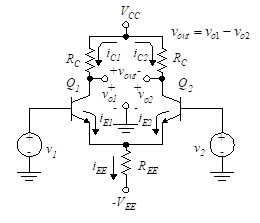

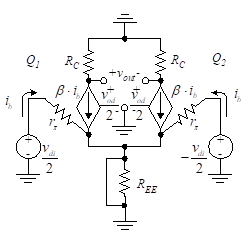

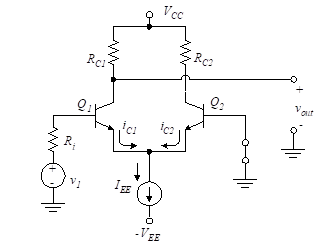

धेरै अप-एप्सहरूको इनपुट चरण डी छifferential एम्पलीफायर जस्तै 1 मा यसको सरल रूप मा देखाइएको छ।

चित्रा 1 - भिन्नता एम्पलीफायर

अंतर एम्पलीफायर दुई एमिटर-युग्मित आम-emitter बाट बनाइएको छ dc एम्पलीफायरहरू। यसको दुई आगतहरू छन्, v1 र v2, र तीन outputs, vo1, vo2 र vबाहिर। तेस्रो उत्पादन, vबाहिर, बीचको भिन्नता हो vo1 र vo2.

1.1 डीसी ट्रान्सफर विशेषताहरु

अंतर एम्पलीफायरले ठूलो संकेत इनपुटहरूको साथ linearly काम गर्दैन। विश्लेषण को सरल गर्न को लागी हामी मानिन्छ कि रे ठूलो छ, कि प्रत्येक ट्रांजिस्टर को आधार प्रतिरोध नगरी छ र प्रत्येक ट्रांजिस्टर को उत्पादन प्रतिरोध ठूलो छ। ध्यान दिनुहोस् कि हामी विभेदक एम्पलीफायरमा RE को बरु REE को प्रयोग गर्छौं किनकि यहाँ प्रयोग हुनेवाला रिजस्टर ठूलो छ र हालको स्रोतको बराबर प्रतिरोध हुन सक्छ। REE को ठूलो मूल्य लगभग निरंतर एमिटर रिस्जिस्टर भोल्टेज ड्रप राख्छ।

अब हामी यस सर्किटलाई आउटपुट भोल्टेजको लागि समाधान गर्दछौं। चितवन 1 को सर्किटका लागि हामी आधार जंक्शन लुप वरपरको केवील समीकरण लेखनद्वारा सुरु गर्छौं।

(1)

(2)

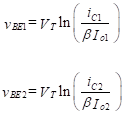

हामीले कलेक्टर संस्करणको लागि अभिव्यक्ति खोज्न आवश्यक छ, iC1 र iC2। आधार-एमिटर वोल्टेजहरू समीकरण द्वारा दिइएको छ,

समीकरण (2) मा Io1 र Io2 को लागि उल्टो संतृप्ति धाराहरू छन् Q1 र Q2 क्रमशः। ट्रांजिस्टरहरू समान हुन मानिन्छ। संयोजन समीकरण (1) र (2) उपज

(3)

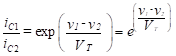

हालको अनुपातको लागि सुलभ समीकरण (3), हामी पाउँछौं,

(4)

हामी मान्न सक्छौं iC1 लगभग बराबर छ iE1 र iC2 लगभग बराबर छ iE2। यसैले

(5)

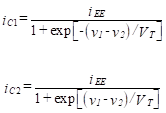

संयोजन समीकरण (4) र (5), हामीसँग छ

(6)

कि नोट

(7)

समीकरण (6) देखेर एक महत्वपूर्ण अवलोकन गर्न सकिन्छ। यदि v1 - v2 धेरै सौ millivolts भन्दा ठूलो हुन्छ, ट्रांजिस्टर हालको ट्रांजिस्टर 2 मा सानो हुन्छ र ट्रांजिस्टर अनिवार्य रूपमा काटिएको छ। ट्रान्जिस्टर 1 मा कलेक्टर हालको लगभग बराबर छ iEE, र यो ट्रांजिस्टर संतृप्त छ। कलेक्टर धाराहरू, र यसैले आउटपुट भोल्टेज vबाहिर, दुई इनपुट भोल्टहरू बीचको अंतरबाट स्वतन्त्र हुनुहोस्।

रैखिक प्रवर्द्धन केवल 100 एमवी भन्दा कम इनपुट भोल्टेज डिभाइसहरूको लागि मात्र हुन्छ। इनपुट भोल्टेजको रैखिक दायरा बढाउनको लागि, सानो एमिटर प्रतिरोधक थप्न सकिन्छ।

1.2 सामान्य-मोड र भिन्नता मोड लाभहरू

अंतर एम्पलीफायर केवल दुई इनपुट भोल्टेज को बीच को अंतर को जवाब दिनु पर्छ, v1 र v2। तथापि, एक व्यावहारिक सेप्टेम्बरमा आउटपुट यी इनपुटहरूको योगमा केही डिग्रीमा निर्भर गर्दछ। उदाहरणका लागि, यदि दुवै इनपुट बराबर छ भने, आउटपुट भोल्टेज आदर्श रूपमा शून्य हुनु पर्दछ, तर व्यावहारिक एम्पलीफायरमा यो होइन। जब सर्किटले फरक फरक पार्छ, हामी यो मामलालाई लेबल गर्दछौं अंतर मोड। यदि दुई आगतहरू समान बनाइन्छ भने, हामी सर्किट हो भनेर भन्छौं सामान्य मोड। आदर्श रूप देखि हामी सर्किट केवल अंतर विधा मा एक उत्पादन को उत्पादन गर्न को अपेक्षा गर्नेछन्।

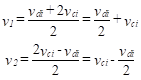

कुनै पनि दुई इनपुट वोल्टेज, v1 र v2, एक साधारण र एक अंतर भाग मा हल गर्न सकिन्छ। हामी निम्न दुईवटा नयाँ भोल्टेजहरू परिभाषित गर्दछौँ:

(8)

भोल्टेज, vdi, अंतर-मोड इनपुट भोल्टेज हो र यो केवल दुई इनपुट भोल्टहरू बीचको भिन्नता हो। भोल्टेज, vci, सामान्य मोड इनपुट भोल्टेज हो, र यो दुई इनपुट भोल्टहरूको औसत हो। मूल इनपुट भोल्टहरू यी नयाँ मात्राहरूको सन्दर्भमा व्यक्त गर्न सकिन्छ:

(9)

यदि हामी दुई इनपुट भोल्टहरू बराबर सेट गर्छौं भने, हामीसँग छ

(10)

दुई इनपुट बराबर बराबर भएकोले, इमिटर-बेस जंक्शन भल्टेज बराबर हुन्छ (यदि ट्रान्जिस्टरहरू समान छन्)। यसरी, कलेक्टर धाराहरू पनि समान हुनुपर्छ।

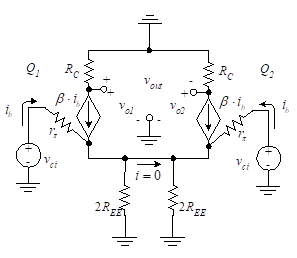

चित्रा 2 (ए) भिन्न-मोड एम्पलीफायर बराबर बराबर सर्किट

अब हामी चित्रकला 2 (ए) मा देखाईएको अक्ष-मोड इनपुट भोल्टेज को बराबर बराबर सर्किट देख्छौं। ध्यान दिनुहोस् कि हालको रूपमा Q1 सर्किट बढ्छ, वर्तमान मा Q2 सर्किट एउटै दर र आयाममा घट्छ। यो इनपुट देखि सत्य हो Q2 यसको बराबर हो Q1 तर 180o चरण बाहिर। यसैले भोल्टेज परिवर्तन हुन्छ REE शून्य हो। यसबाट ac सिग्नल भोल्टेज REE शून्य हो, यो सर्ट सर्किट द्वारा प्रतिस्थापित गर्न सकिन्छ ac बराबर सर्किट। ध्यान दिनुहोस् कि प्रत्येक ट्रांजिस्टर आधारमा वोल्टेज राख्ने जो आयाम तर 180 मा बराबर छo चरण को बाहिर दुई आयाम को दुई ट्रांजिस्टर को आधार मा एक भोल्टेज को बराबर को बराबर छ। भोल्टेज vo1 र vo2 समान समानता को हो तर विपरीत चरण र अंतर-मोड लाभ हो

(11)

यो अंतर-मोड लाभ एक मा परिभाषित गरिएको छ एकल समाप्ति आउटपुट किनकि यो एक कलेक्टर र जमीन बीचमा लिइन्छ। यदि आउटपुट बीचमा लिइन्छ भने vo1 र vo2, विन्डो मोड फाइदा एक छ डबल-आउटपुट आउटपुट र द्वारा दिइएको छ

(12)

एक समान विश्लेषण चित्रा 2 (बी) मा सामान्य-मोड बराबर सर्किटमा लागू गर्न सकिन्छ।

चित्रा 2 (बी) साधारण मोड एम्पलीफायर समतुल्य सर्किट

यदि हामी रिस्जिस्टर विभाजित गर्दछौं REE दुई समानांतर प्रतिरोधकहरुमा प्रत्येक मूल मूल प्रतिरोध को दोश्रो, हामी सर्किट को केवल आधा को विश्लेषण गरेर आउटपुट पा सकते हो। ट्रांजिस्टरहरू समान छन् र साधारण-मोड इनपुट भोल्टहरू बराबर र इन-चरण हुन्, 2 को भोल्टेजहरू।REE प्रतिरोधहरू उस्तै छन्। यसकारण, दुई समानांतर प्रतिरोधकहरू बीचको शून्यको लागि देखाइएको छ र हामी सर्किटको एक मात्र पक्षलाई मात्र हेर्दछ। सामान्य-मोड भोल्टेज लाभ हो

(13)

समीकरण (13) मानिन्छ REE ठूलो र re<<REE.

हामी सामान्य-मोड र अंतर-मोड लाभको रूपमा डबल-आउटपुट आउटपुट भोल्टेज फेला पार्छौं:

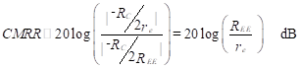

(14)

यो विन्डोज-मोडको लाभ आम-मोड फाइदा भन्दा धेरै ठूलो हुनको लागि वांछनीय छ ताकि एम्पलीफायर मुख्य इनपुट इनपुट भोल्टहरूको बीचमा फरक पार्छ। The साधारण-मोड अस्वीकार अनुपात, CMRR, सामान्य मोड फाइदाको विभेद मोड मोडको अनुपातको रूपमा परिभाषित गरिएको छ। यो सामान्यतया डीबीमा व्यक्त गरिएको छ।

(15)

अब हामी एम्पलीफायर दुवै इनपुट मोड र साधारण मोड मा इनपुट प्रतिरोध को निर्धारण गर्छन। विभेद मोडको लागि, हामी दुवै ट्रांजिस्टरको आधारमा एम्पलीफायरमा हेर्छौं। यो दुवै ट्रांजिस्टरहरूको emitter मार्फत पूर्ण सर्किटमा परिणाम गर्दछ, र इनपुट प्रतिरोध छ

(16)

अब आम मोड इनपुटको लागि, हामी चित्रा 2 (बी) मा एम्पलीफायरमा हेर्छौं। यसरी, इनपुट प्रतिरोध छ

(17)

यी नतीजाले संकेत गर्दछ कि सामान्य मोडको इनपुट प्रतिरोध विभेद मोडको तुलनामा धेरै अधिक हुन्छ।

हाम्रो अंतर एम्पलीफायर विश्लेषण BJTs मा ट्रांजिस्टर बिल्डिंग ब्लक को रूप मा आधारित छ। FETs पनि अंतर एम्पलीफायरहरूमा प्रयोग गर्न सकिन्छ जुन कम इनपुट पूर्वाधार र लगभग अनंत इनपुट प्रतिबाधाको परिणामस्वरूप फाईलहरू। FET को प्रयोग गरेर अंतर एम्पलीफायर को विश्लेषण त्यहि तरिका मा पूरा भएको छ जस्तै बीजेटी विश्लेषण को।

विभेदकारी एम्पलीफायरहरूले ट्रांजिस्टरहरूसँग मेल खाएको छ कि इन्टरनेसनल सही ढंगले सञ्चालन गर्दछ भन्ने विश्वास गर्नुहोस्। यदि अंतर एम्पलीफायर एक एकीकृत सर्किट मा छ, यो अतिरिक्त आवश्यकता एक समस्या को कम छ किनकी दुई ट्रांजिस्टरहरु एक नै समय मा एक नै सामाग्री को उपयोग गरेर बनाइयो।

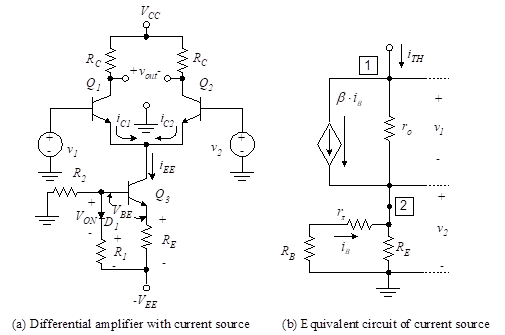

निरन्तर वर्तमान स्रोतको साथ 1.3 विभेदक एम्पलीफायर

बनाउन को लागी वांछनीय छ REE सामान्य-मोड आउटपुट घटाउन सम्भव ठूलो रूपमा। समीकरण देखि थाहा हुन्छ कि CMRR ठूलो बनाउन को लागी हामी बनाउन पर्छ REE ठूलो। ठूलो रिजर्भेसन आईसी चिप्समा निर्माण गर्न गाह्रो हुन्छ किनकि, हामी एक वैकल्पिक दृष्टिकोण खोज्छौं। यो प्रतिस्थापन गरेर पूरा हुन्छ REE एउटा dc हालको स्रोत। एक आदर्श वर्तमान स्रोत अनन्त प्रतिबाधा छ, त्यसैले हामी प्रतिस्थापन गर्ने सम्भावनाको खोजी गर्दछौं REE यस्तो स्रोतको साथ। चित्रा 9.3 एक अंतर प्रवर्धक को वर्णन गर्दछ जहां resistor, REE, स्थिर-हालको स्रोत संग प्रतिस्थापन गरिएको छ।

(18)

स्रोत नजिक नजिकको निरन्तर-हालको स्रोत हो, उच्च सामान्य मोड अस्वीकार अनुपात। हामी डायोड-मुआवजा निश्चित-पूर्वाग्रह हालको स्रोतको वर्णन गर्दछौं। क्षतिपूर्ति सर्किटको अपरेसनले तापमान भिन्नताहरूमा कम निर्भर गर्दछ। डायोड D1 र ट्रांजिस्टर Q3 चयन गरिएका छन् ताकि तिनीहरूसँग अपरेटिङ तापमानको दायरामा लगभग समान विशेषताहरू छन्।

चित्रा 3 (ए) को सर्किट को विश्लेषण गर्न र सीएमआरआर को खोज्नुहोस, हामी को बराबर प्रतिरोध को निर्धारण गर्न को लागि, RTH (निरन्तर वर्तमान स्रोत सर्किटको बराबर थिभिनिन)। समकक्ष प्रतिरोध द्वारा दिइएको छ [चित्रा 3 (बी)] हेर्नुहोस्

नोड 1 मा KCL समीकरण लेखन, हामीसँग छ

(19)

जहाँ ro निर्दिष्ट परिचालन बिन्दुमा ट्रांजिस्टरको आन्तरिक प्रतिरोध हो। यो द्वारा दिइएको छ

(20)

चित्रा 3 - निरन्तर-वर्तमान स्रोतको साथ भिन्नता एम्पलीफायर

नोड 2 उपजमा KCL समीकरण

(21)

जहाँ

(22)

मेटाउदैछ v1 र v2 नोड 2 मा समीकरण मा, हामीसँग छ

(23)

अन्त्यमा, थेभेनिन प्रतिरोध समीकरण (२२) र (२)) लाई इक्वेसन (१)) मा प्रतिस्थापित गरेर दिईन्छ।

(24)

अब हामी यो अभिव्यक्ति को सरल गर्न को लागि एक धारणा को श्रृंखला बनाइनेछ। पूर्वाधार स्थिरता कायम राख्न, हामी दिशानिर्देश प्रयोग गर्दछौं

(25)

को यो मूल्य घटाउदै RB समीकरणमा (24) र विभाजन गरेर β, हामी संग छ

(26)

हामी टिप्पणी गरेर यो अभिव्यक्ति सरल गर्न सक्छौं

(27)

हामीसँग छ

(28)

चूंकि दोस्रो समीकरणमा यो समीकरण पहिले भन्दा ठूलो छ, त्यसैले हामी बेवास्ता गर्न सक्छौं RE प्राप्त गर्न

(29)

यो समीकरण अझ थप सरलीकृत गर्न सकिन्छ यदि निम्न अवस्था अवस्थित छ:

(30)

त्यस अवस्थामा, हामीसँग सरल परिणाम छ

(31)

यसैले, यदि सबै अनुमानहरू वैध छन् भने, RTH बाट निस्क्रिय छ β र यसको मूल्य एकदम ठूलो छ।

एकल-अन्त्य गरिएको इनपुट र निर्गतको साथ 1.4 भिन्नता एम्पलीफायर

चित्रा 4 एक अंतर एम्पलीफायर दिखाता छ जहां दोस्रो इनपुट, v2, सेट शून्य बराबर छ र आउटपुट को रूपमा लिइन्छ vo1.

हामी निरन्तर निरन्तर स्रोतको प्रयोगमा REE, अघिल्लो खण्डमा छलफल भएको। यो एक को रूपमा चिनिन्छ एकल चरण अन्त र आउटपुट एम्पलीफायर चरण चरण को रूप मा। एम्पलीफायर सेटिङ द्वारा विश्लेषण गरिएको छ v2 = पहिले नै समीकरणमा 0। अंतर इनपुट मात्र सरल छ

(32)

त्यसैले आउटपुट हो

(33)

चित्रा 4 - चरण पुनर्गठनको साथ एकल-समाप्त इनपुट

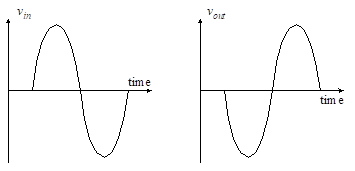

माइनस संकेतले यो एम्पलीफायरले 180 प्रदर्शन गर्दछo आउटपुट र इनपुट बीच चरण पारी। चित्रा 5 मा ठेठ sinusoidal इनपुट र आउटपुट चित्रण गरिएको छ।

चित्रा 5 - Sinusoidal इनपुट र आउटपुट

यदि आउटपुट सिग्नल ग्राउन्डमा उल्लेख गरिएको छ तर चरण पुन: रूपान्तरण वांछित छैन, आउटपुट ट्रांजिस्टरबाट लिन सकिन्छ Q2.

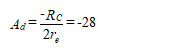

उदाहरण १ - डिफरेन्सियल एम्पलीफायर (विश्लेषण)

अंतर वोल्टेज लाभ, सामान्य-मोड भोल्टेज लाभ प्राप्त गर्नुहोस्, र चित्रा 1 मा देखाएको सर्किटको लागि CMRR। मानौं Ri = 0, RC = 5 kΩ, VEE = 15 V, VBE = 0.7 V, VT = 26 एमवी, र REE = 25 kΩ। गरौं v2 = 0 बाट र आउटपुट लिनुहोस् vo2.

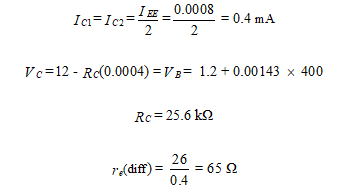

समाधान: हालको मार्फत REE क्विसन्ट शर्तमा पाइन्छ। आधारको रूपमा Q2 ग्राउन्ड गरिएको छ, एमिटर भोल्टेज हो VBE = 0.7 V, र

प्रत्येक ट्रांजिस्टरमा क्विसन्ट हाल यस रकमको आधा छ।

देखि

प्रत्येक ट्रांजिस्टर मा अंतर वोल्टेज लाभ छ

साधारण-मोड भोल्टेज लाभ हो

त्यसपछि आम-मोड अस्वीकार अनुपात द्वारा दिइन्छ

आवेदन

साथै, तपाइँ यी गणनाहरू TINA वा TINACloud सर्किट सिमुलेटरहरूसँग प्रयोग गर्न सक्नुहुन्छ, तलका लिङ्क क्लिक गरी तिनीहरूको इन्टरप्राइटर उपकरण प्रयोग गरेर।

1- भिन्नता एम्पलीफायर सर्किट सिमुलेशन

उदाहरण 2

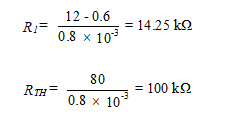

उदाहरण 1 मा वर्णित अंतर एम्पलीफायर को लागि, प्रतिस्थापन को लागि एक तापमान-क्षतिपूर्ति निश्चित-पूर्वाग्रह वर्तमान स्रोत (चित्रा 3) को डिजाइन REE र अंतर एम्पलीफायर को लागि नयाँ CMRR को निर्धारण, संग ro = 105 kΩ, VBE = 0.7 V, र β = 100। मान्नुहोस् R1 = R2.

समाधान: हामी ट्रांजिस्टर अपरेसन बिन्दुको बीचमा छु dc लोड लाइन।

त्यसपछि, चित्रा 3 (ए) को हालको स्रोतलाई उल्लेख गर्दै,

पूर्वाधार स्थिरताका लागि,

त्यसपछि

0.1 देखिRE>>re (जस्तै, १.२1.25 kΩ >> २ / / ०.26 Ω), तब इक्वेसनबाट ()१) हामीसँग छ

CMRR द्वारा दिइन्छ

आवेदन

साथै, तपाइँ यी गणनाहरू TINA वा TINACloud सर्किट सिमुलेटरहरूसँग प्रयोग गर्न सक्नुहुन्छ, तलका लिङ्क क्लिक गरी तिनीहरूको इन्टरप्राइटर उपकरण प्रयोग गरेर।

2- भिन्नता एम्पलीफायर सर्किट सिमुलेशन

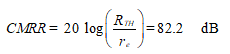

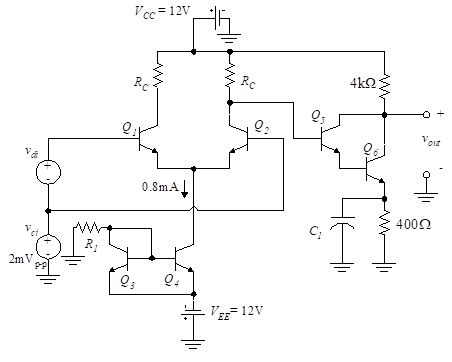

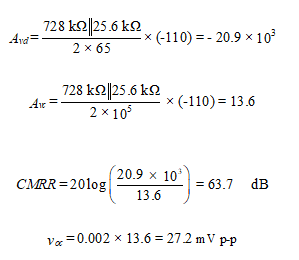

उदाहरण 3

चितवन 6 मा अधिकतम आउटपुट भोल्टेज स्विङको लागि निर्दिष्ट सर्तहरू प्राप्त गर्न सर्किटको डिजाइन गर्नुहोस्। पाँच ट्रांजिस्टर, Q1 लाई Q5, प्रत्येक छ β = 100 जबकि Q6 छ एक β को 200। VBE सबै ट्रांजिस्टरका लागि 0.6 V हो, VT = 26 एमवी, र VA = 80 V. सबै ट्रांजिस्टरहरू समान मानिन्छ।

निर्धारण गर्नुहोस्,

(a) RC, R1, र CMRR।

(बी) सामान्य मोड आउटपुट भोल्टेज।

(सी) भिन्न-भिन्न मोड आउटपुट भोल्टेज।

(घ) भिन्नता-मोड इनपुट भोल्टेज vdi अधिकतम आउटपुटको लागि।

समाधान: हामी सर्किटलाई तीन भागमा उपचार गर्नेछौं:

- 1। Darlington एम्पलीफायर।

- 2। भिन्न प्रवर्धक

- 3। सरल वर्तमान स्रोत

अब सम्पूर्ण प्रणालीको लागि, हामीसँग छ

अंतर इनपुट vdi अधिकतम पूर्वनिर्धारित आउटपुट भोल्टेज स्विङ उत्पादन गर्न आवश्यक छ

साथै, तपाइँ यी गणनाहरू TINA वा TINACloud सर्किट सिमुलेटरहरूसँग प्रयोग गर्न सक्नुहुन्छ, तलका लिङ्क क्लिक गरी तिनीहरूको इन्टरप्राइटर उपकरण प्रयोग गरेर।

3- भिन्नता एम्पलीफायर सर्किट सिमुलेशन

वर्तमान - १ भिन्न एम्पलीफायरहरू

वर्तमान - १ भिन्न एम्पलीफायरहरू अघिल्लो- व्यावहारिक अपरेशनल एम्पलीफायरहरू - परिचय

अघिल्लो- व्यावहारिक अपरेशनल एम्पलीफायरहरू - परिचय