4. Konfiguracje i zniekształcenia wzmacniacza FET

Konfiguracje i zniekształcenia wzmacniacza FET

Podejścia, które są wykorzystywane do odchylania BJT, można również wykorzystać do polaryzowania MOSFETÓW. Możemy rozdzielić te podejścia na te stosowane dla wzmacniaczy dyskretnych w porównaniu ze wzmacniaczami układów scalonych. Konstrukcje dyskretnych elementów wykorzystują duże kondensatory sprzęgające i obejściowe, aby izolować polaryzację prądu stałego dla każdego stopnia wzmacniacza, podobnie jak wzmacniacze dyskretne BJT. Wzmacniacze IC MOSFET są zazwyczaj sprzężone bezpośrednio, ponieważ duże kondensatory nie są praktyczne. Wzmacniacze IC MOSFET są zwykle zniekształcone przy użyciu źródeł prądu stałego analogicznych do tych stosowanych w wzmacniaczach BJT IC.

Odchylenie MOSFET komponentu 4.1

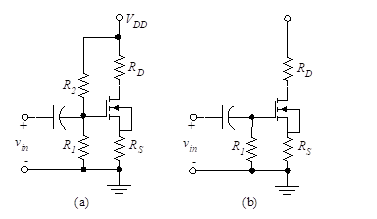

Odchylanie komponentów dyskretnych dla wzmacniaczy MOSFET jest realizowane za pomocą obwodów pokazanych na rysunku 21. Napięcie między bramką a źródłem określa typ obwodu, który może być wymagany dla tej konfiguracji tranzystora. Dla tranzystora w trybie wzmocnienia zawsze będzie potrzebne dodatnie napięcie na bramce. W polaryzacji podziału napięcia pojawi się R1 i R2 w celu uzyskania napięcia dodatniego. W przypadku wyczerpania MOSFET lub JFET, R2 może być skończony lub nieskończony, jak pokazano na rysunku 21 (b).

Rysunek 21 - Konfiguracje polaryzacji wzmacniacza

Wspólne źródło (CS)- ac wejście jest stosowane w CGThe ac dane wyjściowe są pobierane CD, CS jest podłączony do a dc źródło napięcia lub masa. Jest to analogiczne do konfiguracji wspólnego emitera dla BJT.

-Rezystor źródła (SR) - ac wejście jest stosowane w CGThe ac dane wyjściowe są pobierane CD i CS jest pominięty. Jest to analogiczne do konfiguracji rezystora emitera dla BJT.

-Common Gate (CG) - ac wejście jest stosowane w CSThe ac dane wyjściowe są pobierane CD i CG jest podłączony do a dc źródło napięcia lub masa. Czasami w konfiguracji CG, CG jest pomijany, a brama jest podłączona bezpośrednio do dc napięcie zasilające. CG jest analogiczna do wspólnej konfiguracji bazowej dla BJT, chociaż rzadko występuje w obwodach.

-Obserwator źródła (SF) - ac wejście jest stosowane w CGThe ac dane wyjściowe są pobierane CS a odpływ jest podłączony do a dc zasilanie bezpośrednio lub za pośrednictwem CD. Jest to czasami nazywane wspólnym drenem (CD) i jest analogiczne do konfiguracji nadajnika emiterów dla BJT.

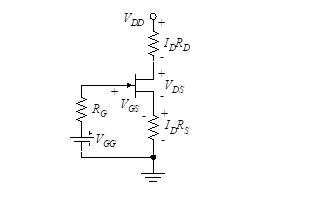

Rysunek 22 - równoważny obwód Thevenina

Każda z tych konfiguracji została szczegółowo omówiona w rozdziale 9, „Analiza wzmacniacza FET”.

Ponieważ różne konfiguracje różnią się tylko połączeniami za pośrednictwem kondensatorów, a kondensatory są obwodami otwartymi dc napięcia i prądy możemy badać dc stronniczość dla ogólnego przypadku. W przypadku konstrukcji wzmacniacza chcemy, aby tranzystor działał w aktywnym obszarze roboczym (określanym również jako region nasycenia lub tryb szczypania), więc zakładamy charakterystykę szczypania IV dla urządzenia. (Zawsze powinniśmy weryfikować to założenie pod koniec projektu!)

Aby uprościć analizę odchylenia, używamy źródła Thevenina do modelowania obwodu przy bramce tranzystora, jak pokazano na rysunku 22.

(24)

Ponieważ istnieją trzy nieznane zmienne, które należy ustawić na polaryzację (ID, VGS, VDS), potrzebujemy trzech dc równania. Po pierwsze dc równanie wokół pętli gate-source jest napisane.

![]()

(25)

Zauważ, że ponieważ prąd bramki wynosi zero, w całym obwodzie występuje zerowy spadek napięcia RG. Sekunda dc równanie znajduje się na podstawie równania prawa Kirchhoffa w pętli dren-źródło.

![]()

(26)

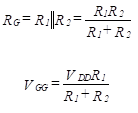

Trzeci dc równanie niezbędne do ustalenia punktu odchylenia można znaleźć w równaniu (20)  w sekcji „Tranzystor polowy łączeniowy (JFET)" który powtarza się tutaj.

w sekcji „Tranzystor polowy łączeniowy (JFET)" który powtarza się tutaj.

(27)

Pierwsze przybliżenie ma zastosowanie, jeśli |λVDS| << 1 (co jest prawie zawsze prawdziwe) i znacznie upraszcza rozwiązanie sprzężonych równań.

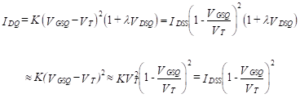

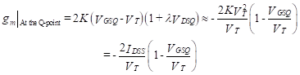

Możemy umieścić równanie dla gm [Równanie (22)]

(22)

w podobny format, który okaże się przydatny w projektowaniu.

(28)

Równania (25) - (28) są wystarczające do ustalenia odchylenia. W przypadku dyskretnych wzmacniaczy MOSFET nie musimy umieszczać punktu Q w środku ac linia obciążenia, jak to często robiliśmy dla polaryzacji BJT. Dzieje się tak, ponieważ dyskretne wzmacniacze FET są zwykle używane jako pierwszy etap w łańcuchu wzmacniaczy, aby wykorzystać wysoką rezystancję wejściową. Gdy jest używany jako pierwszy etap lub przedwzmacniacz, poziomy napięcia są tak małe, że nie napędzamy wyjścia przedwzmacniacza przez duże wyskoki.

CURRENT - 4. Konfiguracje wzmacniacza FET i odchylenie

CURRENT - 4. Konfiguracje wzmacniacza FET i odchylenie POPRZEDNI 3. Junction tranzystor polowy (JFET)

POPRZEDNI 3. Junction tranzystor polowy (JFET)