5. Układy scalone MOSFET

Układy scalone MOSFET

Gdy tranzystory MOSFET są wytwarzane jako część układu scalonego, względy praktyczne wymagają dwóch głównych zmian w konfiguracjach obwodów. Po pierwsze, duże kondensatory sprzęgające i obejściowe stosowane w wzmacniaczach dyskretnych nie mogą być praktycznie produkowane w układach scalonych ze względu na mały rozmiar. Pokonujemy tę wadę, wytwarzając wzmacniacze sprzężone bezpośrednio.

Drugą ważną zmianą jest to, że nie możemy łatwo wytworzyć rezystorów używanych jako część obwodów polaryzacji. Zamiast tego używamy aktywnych obciążeń i źródeł prądu składających się z tranzystorów MOS.

Układy scalone wykorzystują obwody NMOS i PMOS. CMOS jest bardziej powszechny w obwodach cyfrowych, podczas gdy NMOS jest zwykle stosowany w układach scalonych o większej gęstości (tj. Więcej funkcji na układ).

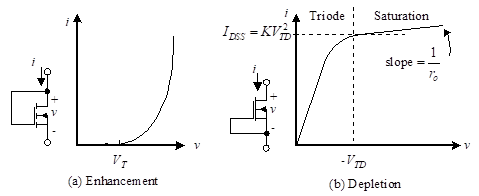

Symulowanie aktywnych obciążeń wykorzystuje nachylenie krzywych charakterystycznych MOS. Rysunek 23 pokazuje dwa typy aktywnych obciążeń. Na rysunku 23 (a) pokazujemy obciążenie wzmocnienia NMOS, podczas gdy 23 (b) pokazuje obciążenie zubożania NMOS. Na rysunku pokazano również odpowiednie krzywe charakterystyczne.

Rysunek 23 - Aktywne obciążenia

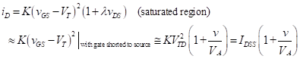

Dla obciążenia wzmocnienia NMOS związek między napięciem i prądem jest podawany przez

![]()

(29)

Równoważny opór tej konfiguracji to 1 /gm, gdzie wartość transkonduktancji jest wartością, która ma zastosowanie w punkcie obciążenia.

Obciążenie zubożenia NMOS ma równoważny opór, który jest określony przez nachylenie charakterystyki podanej przez poniższe równanie

(30)

5.1 Biasing układów scalonych MOSFET

Teraz, gdy mamy dwie techniki symulowania aktywnych obciążeń, możemy rozwiązać problem polaryzacji. Używamy aktywnego obciążenia zamiast rezystancji obciążenia w dowolnej konfiguracji obwodu. Aby pokazać technikę ich analizy, rozważmy wzmacniacz NMOS wykorzystujący obciążenie wzmacniające, jak pokazano na rysunku 24.

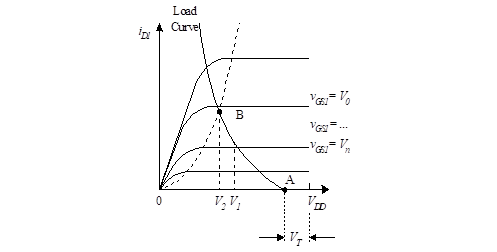

Etykietowany tranzystor Q2 Zastępuje RD naszych wcześniejszych obwodów. Aby określić spoczynkowy punkt pracy, używamy tych samych technik, co w Rozdziale 4, „Konfiguracje wzmacniacza FET i polaryzacja”, zastępując jedynie graficzną charakterystykę obciążenia wzmacniającego dla linii obciążenia rezystora. Oznacza to, że musimy znaleźć równoczesne rozwiązanie charakterystyki tranzystora FET z równaniem dla linii obciążenia. Możemy to zrobić graficznie, jak pokazano na rysunku 25.

Krzywe parametryczne są krzywymi charakterystycznymi dla tranzystora wzmacniającego, Q1. Charakterystyka napięcia względem prądu aktywnego obciążenia, Q2 są te z rysunku 23. Napięcie wyjściowe, vna zewnątrz, jest różnica między VDD i napięcie na aktywnym obciążeniu. Prąd w aktywnym obciążeniu jest taki sam jak prąd drenu w tranzystorze wzmacniającym. Dlatego konstruujemy linię obciążenia, biorąc przesunięte odbicie lustrzane charakterystyki rysunku 23. Punktem pracy jest przecięcie tej krzywej z odpowiednią krzywą charakterystyki tranzystora. Musimy znaleźć napięcie od bramki do źródła, aby wiedzieć, którą krzywą tranzystora wybrać. Jak zobaczymy dalej, napięcie polaryzacji wejściowej jest często zastępowane przez aktywne źródło prądu.

Rysunek 25 - rozwiązanie graficzne dla punktu Q

Teraz, gdy wiemy, jak symulować aktywne obciążenie, zwracamy naszą uwagę na generowanie prądu odniesienia, który będzie wykorzystywany jako część obwodu polaryzacji wejściowej. Te źródła prądu są używane w taki sam sposób, w jaki używaliśmy ich do polaryzacji wzmacniacza BJT.

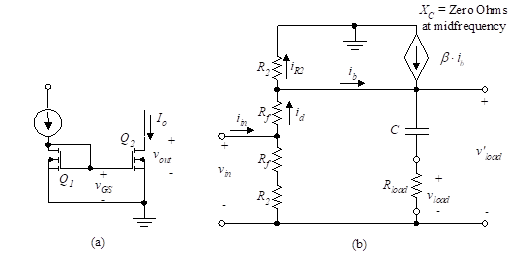

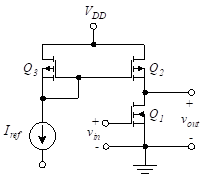

Rysunek 26 - Bieżące lustro

Analizujemy MOSFET lustro prądowe. Bieżące lustro jest pokazane na rysunku 26. Przyjmuje się, że oba tranzystory są idealnie dopasowane. Prąd wyjściowy to prąd drenu Q2oraz referencyjne napędy prądowe Q1. Jeśli tranzystory są idealnie dopasowane, prąd wyjściowy będzie dokładnie równy prądowi odniesienia. To prawda, ponieważ tranzystory są połączone równolegle. Podobnie jak w przypadku zwierciadła prądowego BJT, prąd odniesienia można wygenerować przez przyłożenie napięcia odniesienia do rezystancji odniesienia, jak pokazano na rysunku 26 (b).

Łączenie różnych podukładów (tj. Obciążenia aktywnego i prądu odniesienia) skutkuje wzmacniaczem CMOS z rysunku 27.

Wzmocnienie tego wzmacniacza daje

![]()

(31)

Rysunek 27 - wzmacniacz CMOS

5.2 Body Effect

Nasza dyskusja na temat sekcji „2. Półprzewodnik z tlenkiem metalu FET (MOSFET) ”odnosi się do podłoża (lub korpusu) tranzystora MOSFET. To podłoże odgrywa ważną rolę w tworzeniu kanału. Podczas działania dyskretnych tranzystorów MOSFET korpus jest często podłączony do źródła zasilania. W takich przypadkach podłoże nie ma bezpośredniego wpływu na działanie urządzenia i obowiązują krzywe opracowane wcześniej w tym rozdziale.

Sytuacja zmienia się, gdy MOSFET są wytwarzane jako część układów scalonych. W takich przypadkach substrat każdego pojedynczego tranzystora nie jest izolowany od innych substratów. Rzeczywiście, substrat jest często dzielony pomiędzy wszystkie MOSFETy na chipie. W układzie PMOS współużytkowane podłoże byłoby podłączone do najbardziej pozytywnego terminala źródłowego, podczas gdy w NMOS jest podłączone do uziemienia (lub do ujemnego źródła zasilania, jeśli jest obecne). Powoduje to odwrócenie polaryzacji między źródłem a ciałem każdego tranzystora. Efektem tego odwrotnego polaryzacji jest zmiana charakterystyk operacyjnych. Na przykład w n-kanałowe urządzenie, skutecznie podnosi próg (VT). Wielkość, o jaką zmiany progu zależą od parametrów fizycznych i konstrukcji urządzenia. W przypadku NMOS zmiana ta może być przybliżona przez

![]()

(32)

W równaniu (32) γ jest parametrem urządzenia, który zmienia się między 0.3 a 1 (V-1/2). VSB jest napięciem między źródłem a ciałem i jest Potencjał Fermiego. Jest to właściwość materiału, a typowa wartość to 0.3 V dla krzemu.

CURRENT - 5. Układy scalone MOSFET

CURRENT - 5. Układy scalone MOSFET POPRZEDNI 4. Konfiguracje i zniekształcenia wzmacniacza FET

POPRZEDNI 4. Konfiguracje i zniekształcenia wzmacniacza FET