IBIS simulacija

IBIS simulacija

Jump to TINA Main Page & General Information

IBIS simulacija

IBIS (specifikacija vhodno / izhodne informacije o pufru) je metoda za zagotavljanje informacij o modeliranju vhodnih / izhodnih medpomnilnikov integriranih vezij. Dobra stvar pri modelih IBIS je, da so pogosto na voljo tudi za naprave, kjer celotni modeli naprav niso na voljo pri proizvajalcih iz kakršnega koli razloga (npr. Kompleksnost, zaščitena zaščita informacij itd.).

Ena izmed najbolj priljubljenih uporab modelov IBIS je analiza integritete signala, vključno z usklajevanjem impedance in še več.

TINA trenutno podpira najbolj razširjeno različico IBIS 4.2.

V TINA-ju lahko pretvorite IBIS modele v TINA Spice in jih nato uporabite v vseh vezjih v TINA. Prav tako lahko dokončate poenostavljene modele digitalnih naprav - npr. MCU z modeli IBIS -, da bolje opišete njihovo analogno vedenje.

V nadaljevanju bomo prikazali uporabo IBIS modelov s pomočjo primera fiksiranja celovitosti signala med Texas Instruments TMS320C6748 DSP in ADS1259 delta-sigma ADC.

Izberite Datoteka / Uvoz / datoteka IBIS (* .ibs)tako, da izberete c6748zce.ibs iz TINA imenik >Primeri IBIS.

Prikaže se naslednje pogovorno okno. V tem pogovornem oknu lahko izberete model za uvoz.

Sedaj izberite SPI1CLK_GP213 signal, model PBFZP18LL_X50_PI_3P3 (celica, ki deluje pri 3.3V brez pullup ali pulldown), in Tip vrednost.

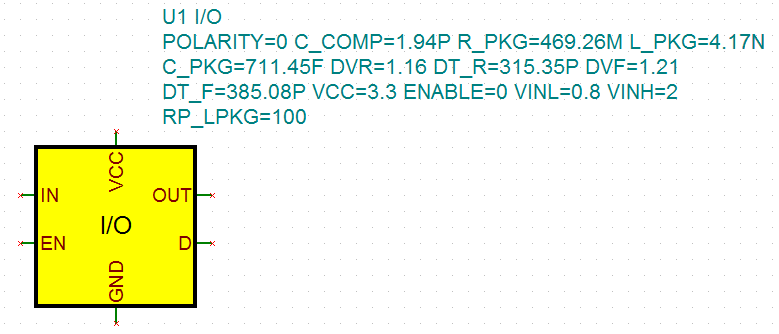

Pritisnite OK. IBIS model se samodejno pretvori v a Spice makro.

SPI1CLK_GP213 je serijski takt glavne urejevalne konfiguracije čipa TMS320C6748 za pogon takta SPI takta AD pretvornika, Texas Instruments ADS1259.

Izberite Datoteka / Uvoz / datoteka IBIS (* .ibs)tako, da izberete ads1259.ibs iz TINA imenik >Primeri IBIS.

Prikaže se naslednje pogovorno okno. V tem pogovornem oknu lahko izberete model za uvoz.

Sedaj izberite SCK vhodni signal, DIN_PD_3 model in max vrednost (za napetostno območje 3.3V DVDD).

Pritisnite OK. IBIS model se samodejno pretvori v a Spice makro.

Priključite vmesnik DSP I / O na vhod ADC-ja z brezžično prenosno linijo.

Dodajte vir energije in generator napetosti, da ustvarite signal ure na strani DSP. Postavite napetostne igle za simulacijo na signalna vozlišča.

Parametre prenosne linije prilagajamo na nekaj centimetrov sledi mikrostripov, ki smo jih preusmerili na štiriplastni PCB. To povzroči cc. 500ps zakasnitev in 90 Ohm značilna impedanca.

Datoteka iz \ Primeri \ IBIS \ Ujemanje impedance TMS320C6748.TSC je pripravljen za uporabo.

Zdaj kliknite Analiza, Prehodno.

DSP prenaša signal takta SPI, kjer neenakomerna impedanca ustvarja odseve. Rezultat prikazuje odseve, ki jih povzroča neusklajenost impedance v tej simulaciji vezja.

Na strani ADC (pin EoTL) napetost presega tla in napajalno napetost, kar je v nasprotju z absolutno maksimalno vrednostjo digitalnega vhoda.

Da bi se izognili pod in prekoračitvam na koncu črte, se mora ujemati izhodna impedanca voznika z impedanco sledi z vstavitvijo upora med izhodom in sledjo.

Postavimo upor 100 now v seriji zdaj z izhodom.

Znova zaženite prehodno analizo in primerjajte rezultate s kopiranjem pomembnih krivulj med seboj.

Zdaj lahko vidimo, da je uporaba modela IBIS za razumevanje in iskanje kritičnih vprašanj pri simulaciji pomagala rešiti ta problem.