2. Kovinski oksidni polprevodniški FET (MOSFET)

Kovinski oksidni polprevodniški FET (MOSFET)

Kovinski oksidni polprevodnik FET (MOSFET) je štiri terminalna naprava. Terminali so vir (S), vrata (G) in odtok (D). substrat or telo predstavlja četrti terminal. MOSFET je zgrajen z vhodno spono, izolirano od kanala s silicijevim dioksidom. MOSFETi so lahko bodisi izčrpanosti or način izboljšave. Ta dva pojma bomo v kratkem opredelili.

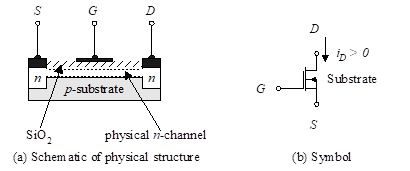

Slika 1 - MOSFET za izčrpavanje n-kanalov

MOSFET-ji se včasih imenujejo IGFET-i (izolirani prehodni tranzistorji za vrata) zaradi SiO2 plast, ki se uporablja kot izolator med vrati in podlago. Analizo začnemo z MOSFET-om. Tako kot je lahko tudi BJTs npn or pnpMOSFETi so lahko bodisi n-kanal (NMOS) ali p-kanal (PMOS). Slika 1 ponazarja fizično strukturo in simbol za n- izpraznjevanje kanalov MOSFET. Opazite, da je substrat povezan z izvornim terminalom. To bo skoraj vedno tako.

MOSFET za izčrpavanje je konstruiran z a fizično med kanalom in izvorom. Posledično, ko napetost, vDS, se uporablja med odtokom in izvorom, tok, iD, obstaja med odtokom in izvorom, čeprav terminal G ostane nepovezan (vGS = 0 V).

Gradnja n- izpraznitev kanalov MOSFET se začne s p-dodani silicij. The nizviri in odtočni vodnjaki tvorijo nizkoodporne povezave med koncema n-kanal, kot je prikazano na sliki 1. Tanka plast silicijevega dioksida se odlaga tako, da pokriva območje med virom in odtokom. SiO2 je izolator. Na izolatorju silicijevega dioksida se tvori plast aluminija, ki tvori vrata terminala. V delovanju je negativen vGS potisne elektrone iz območja kanala, s čimer izčrpa kanal. Kdaj vGS doseže določeno napetost, VT, kanal je stisnjeno. Pozitivne vrednosti. \ T vGS poveča velikost kanala, kar povzroči povečanje toka odtoka. MOSFET za izčrpavanje lahko deluje s pozitivnimi ali negativnimi vrednostmi vGS. Ker so vrata izolirana od kanala, je tokovni tok zanemarljivo majhen (po vrstnem redu 10-12 A).

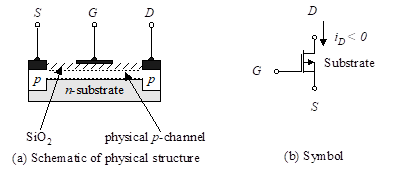

Slika 2 - P-kanal izpraznjevanje MOSFET

Slika 2 je primerljiva s sliko 1, razen da smo spremenili n- izpraznjevanje kanalov MOSFET v a p- izpraznjevanje kanalov MOSFET.

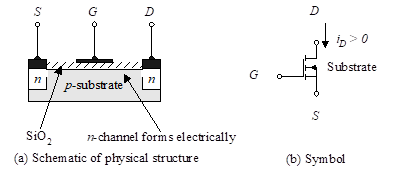

O n-Kanalna izboljšava MOSFET je prikazan na sliki 3 skupaj s simbolom vezja. To je najpogosteje uporabljena oblika tranzistorja s efektom polja.

Slika 3 - MOSFET za izboljšanje n-kanalov

O n-Kanalna izboljšava MOSFET se od izpraznjenega MOSFET-a razlikuje tako, da nima tankega nplast. Zahteva pozitivno napetost med vrati in virom za vzpostavitev kanala. Ta kanal nastane z delovanjem pozitivne napetosti od vrat do vira, vGS, ki privlači elektrone iz regije substrata med n-odporen odtok in vir. Pozitivno vGS povzroči, da se elektroni nabirajo na površini pod oksidno plastjo. Ko napetost doseže prag, VT, da je to območje privabilo zadostno število elektronov, da bi delovalo kot vodenje n-kanal. Brez znatnega toka odtoka iD obstaja do vGS presega VT.

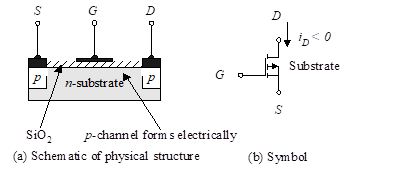

Slika 4 je primerljiva s sliko 3, razen da smo spremenili n-kanalna izboljšava MOSFET na a p-Kanalna izboljšava MOSFET.

Slika 4 - P-kanalni izboljšava MOSFET

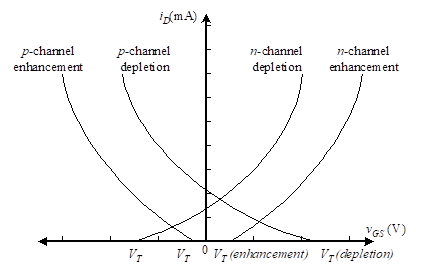

Kot povzetek, družina MOSFET kaže identifikacijo iD v primerjavi z vGS krivulje, prikazane na sliki 5. Vsaka karakteristična krivulja je razvita z zadostno napetostjo odvodnega vira vDS za vzdrževanje naprave v običajnem delovnem območju. \ t iD v primerjavi z vDS krivulje. Razprava v poznejših delih bo določila napetost praga VT tako za izboljšanje MOSFET kot za izčrpavanje MOSFET.

Slika 5 - iD v primerjavi z vGS značilnosti družine MOSFET za zadostno napetost iztoka VDS

Značilnosti terminala za izboljšanje MOSFET načina 2.1

Zdaj, ko smo predstavili osnovno strukturo in osnovo za delovanje MOSFET-a, smo uporabili pristop za preučitev vedenja terminala naprave za izboljšanje. Najprej podajmo nekaj splošnih opažanj s slike 1. Pomislite na normalen pretok toka v MOSFET-u, ki teče od odtoka do vira (tako kot v BJT je med kolektorjem in oddajnikom). Tako kot pri npn BJT, dve povratni diodi obstajata med odtokom in izvorom. Zato moramo na vrata uporabiti zunanje napetosti, da lahko tok teče med odtokom in izvorom.

Če ozemljimo vir in uporabimo pozitivno napetost na vratih, je napetost dejansko napetost od vrat do vira. Pozitivna napetost vrat privlači elektrone in odbija luknje. Ko napetost preseže prag (VT), dovolj elektronov se pritegne, da tvorijo prevodni kanal med odtokom in izvorom. V tem trenutku se vklopi tranzistor in tok je funkcija obeh vGS in vDS. Jasno bi moralo biti VT je pozitivno število za n-kanalna naprava in negativno število za p-kanalna naprava.

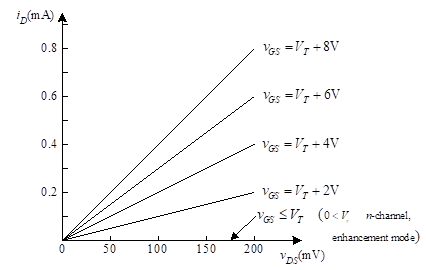

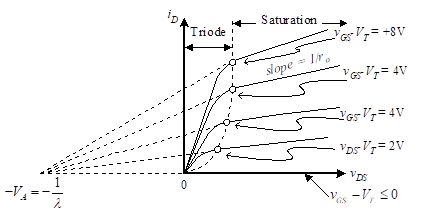

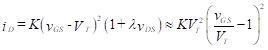

Ko je kanal ustvarjen (tj. vGS >VT), tok lahko pride v tem kanalu med odtokom in izvorom. Ta tok je odvisen od tega vDS, odvisno pa je tudi od vGS. Pri vGS komaj presega napetost praga, lahko teče zelo majhen tok. Kot vGS presega prag, kanal vsebuje več nosilcev in višje tokove so možne. Slika 6 prikazuje razmerje med iD in vDS Kje vGS je parameter. Upoštevajte to za vGS manj kot prag, brez trenutnih tokov. Za višje vGS, odnos med iD in vDS je približno linearna, kar pomeni, da se MOSFET obnaša kot upor, od katerega je odvisen upor vGS.

Slika 6 -iD v primerjavi z vDS za način izboljšave n-kanal MOSFET, ko vDS je majhna

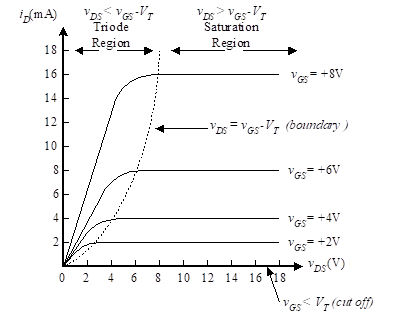

Krivulje slike 6 izgledajo kot ravne črte. Vendar pa se ne bodo nadaljevale kot ravne črte, ko vDS postane večja. Spomnimo se, da se za ustvarjanje prevodnega kanala uporablja pozitivna napetost vrat. To počne s privabljanjem elektronov. Pozitivna odvodna napetost počne isto stvar. Ko se približujemo odtočnemu koncu kanala, se napetost ustvari vGS-vDS ker oba vira nasprotujeta. Če je ta razlika manjša od VT, kanal več ne obstaja za celoten prostor med izvorom in odtokom. Kanal je omejene na koncu odvoda in nadaljnje povečanje v. \ t vDS ne povečajo iD. To je znano kot običajno območje delovanja ali nasičenost območje, prikazano na sliki 7, s horizontalnim prerezom karakterističnih krivulj. Če je razlika večja od VT, to imenujemo trioda način, saj potenciali na vseh treh terminalih močno vplivajo na tok.

Prejšnja razprava vodi do obratovalnih krivulj na sliki 7.

Slika 7 -iD v primerjavi z vGS za MOSFET izboljšanega načina

Prehod med triodom in normalnim delovnim območjem (imenovanim območje nasičenja in pogosto opredeljen kot delovanje v načinu izklopa) delovanja je prikazan kot črtkana črta na sliki 7, kjer

![]()

(1)

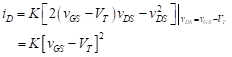

Na meji triode območja kolena krivulj približno sledijo razmerju,

![]()

(2)

V enačbi (2) je K konstanta za dano napravo. Njegova vrednost je odvisna od dimenzij naprave in uporabljenih materialov v njeni konstrukciji. Konstanta je podana z,

![]()

(3)

V tej enačbi, μn je mobilnost elektronov; Coksidoksidna kapacitivnost je kapacitivnost na enoto površine vrat; W je širina vrat; L je dolžina vrat. Enačba kaže na zapleten in nelinearni odnos med iD in dveh napetosti, vDS in vGS. Ker bi želeli odvodni tok spreminjati približno linearno vGS (neodvisno od. \ t vDS), se FET v triodni regiji običajno ne uporablja.

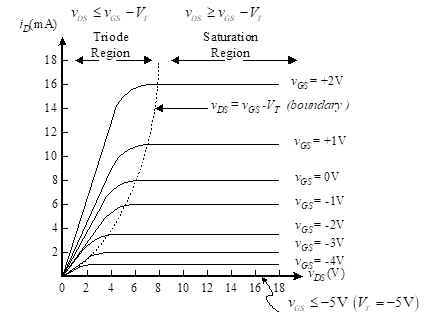

Zdaj želimo najti enačbo za obratovalne krivulje v območju nasičenja. Vrednosti pri prehodu med triodo in nasičeno regijo lahko določimo z vrednotenjem enačbe (2) na prehodu (koleno). To je,

(4)

Ta enačba določa velikost odtočnega toka na meji (črtkana črta na sliki 8) kot funkcijo napetosti od vrat do vira. vGS. Če je potrebno, lahko računamo rahlo naklon karakterističnih krivulj v območju nasičenja z dodajanjem linearnega faktorja.

![]()

(5)

V enačbi (5), λ je majhna konstanta (naklon skoraj vodoravnega odseka karakterističnih krivulj, prikazanih na sliki 8). Običajno je manj kot 0.001 (V-1). Potem pa

![]()

(6)

Vse naše prejšnje razprave so obravnavale tranzistor NMOS. Zdaj na kratko razpravljamo o potrebnih spremembah za PMOS. Za PMOS, vrednosti vDS bo negativna. Poleg tega, da ustvarite kanal v PMOS, ![]() .

.

Slika 8 - Značilnosti terminala tranzistorja MOSFET

Edina sprememba glede na značilnosti NMOS tranzistorjev (slika 7) je, da je horizontalna os zdaj -vDS namesto + vDS, in parametrične krivulje predstavljajo večji odtočni tok, ko se napetost vrat zmanjša (namesto da se poveča za tranzistor NMOS). Krivulje za povečanje vrednosti toka ustrezajo več negativni napetosti vrat. Kdaj vGS > VT, tranzistor je izklopljen. Za izboljšavo PMOS, VT je negativna in za izčrpavanje PMOS, VT je pozitiven.

Enačba za tok pri tranziciji triode regije za tranzistor PMOS je enaka kot pri NMOS. To je,

![]()

(7)

Upoštevajte, da vGS in vDS obe negativni količini. Enačba za območje nasičenja v tranzistorju PMOS je prav tako enaka kot NMOS. To je,

(8)

Upoštevajte, da λ je negativen za PMOS tranzistorje od hitrosti spremembe krivulje (![]() ) je negativna.

) je negativna.

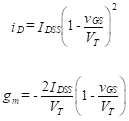

Če vzamemo delno izpeljanko obeh strani enačbe (6) glede na vGS, ![]() , dobimo

, dobimo

![]()

(9)

Raje imamo vrednost gm biti konstanten, zlasti pri velikih nihanjih signalov. Vendar pa lahko ta pogoj le približamo, če uporabimo FET za majhne aplikacije signala. Pri velikih pogojih signala je lahko popačenje valovne oblike v nekaterih aplikacijah nesprejemljivo.

MOSFET za osiromašeni način 2.2

Prejšnji razdelek je obravnaval MOSFET izboljšave. Zdaj je to v nasprotju z MOSFET-om. Za n-kanalni način izboljšave, da bi dobili kanal smo morali uporabiti pozitivno napetost na vratih. Ta napetost je morala biti dovolj velika, da bi zadostno število mobilnih elektronov povzročilo tok v induciranem kanalu.

Slika 9 - Način izčrpavanja n-kanal MOSFET

v n-MOSFET v načinu izpraznitve kanala, ne potrebujemo te pozitivne napetosti, ker imamo fizično vsaden kanal. To nam omogoča, da imamo tok med odtočno in izhodno sponko tudi pri negativni napetosti, ki deluje na vrata. Seveda obstaja meja količine negativne napetosti, ki se lahko priklopi na vrata, medtem ko še vedno teče tok med odtokom in izvorom. Ta meja je ponovno označena kot mejna napetost, VT. Sprememba iz načina izboljšave je, da je napetost od vrat do vira lahko zdaj negativna ali pozitivna, kot je prikazano na sliki 9.

Enačbe, ki definirajo delovanje MOSFET-a, so zelo podobne tistim v izboljševalnem načinu. Vrednost toka odtoka, ko vGS je enaka nič IDSS. To se pogosto imenuje tok zasičenja odtočnega viraAli ničelni tok odtoka. Primerjamo enačbe MOSFET-a z izboljšanim načinom delovanja s tistimi iz načina izčrpavanja, ki ga najdemo

![]()

(10)

Nato najdemo,

(11)

Način izčrpavanja MOSFET-i so na voljo v diskretni obliki ali pa so izdelani na čipih integriranih vezij, skupaj s tipi izboljšav. To vključuje oboje p-tip in n-tip. To omogoča večjo fleksibilnost pri oblikovanju vezij.

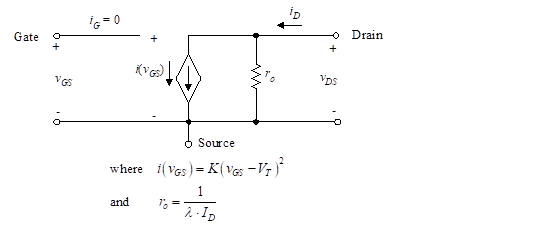

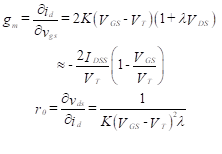

2.3 Sklop ekvivalenta velikega signala

Zdaj želimo razviti enakovredno vezje, ki predstavlja značilnosti velikih signalov na sliki 8 [Equation (5) ali (8)] v območju nasičenja. Upoštevajte, da odtočni tok, iD, odvisno od vGS in vDS. Pri konstantni napetosti od vrat do vira delujemo vzdolž ene od parametričnih krivulj slike, razmerje pa je približno ravno. Enosmerno razmerje med tokom in napetostjo modelira upor. Ekvivalentno vezje je torej sestavljeno iz upora vzporedno s tokovnim virom, kjer vrednost tokovnega vira določa del odtočnega toka zaradi vGS. Nagib krivulje je odvisen od vGS. Nagib je delni derivat,

![]()

(12)

Kje r0 je inkrementalni izhodni upor. Iz enačbe [(5) ali (8) vidimo, da je ta odpor podan z

![]()

(13)

kjer uporabljamo zgornji primer VGS da pokaže, da je upor definiran za določeno konstantno vrednost napetosti od vrat do vira. Končni približek v enačbi (13) je rezultat enačbe (5) s predpostavko, da λ je majhna. Odpornost je zato obratno sorazmerna s tokom prednapetosti, ID. Model ekvivalenta velikega signala je nato podan s sliko 11, kjer r0 je razvit v enačbi (13).

Slika 11 - Sklop ekvivalenta velikega signala

2.4 Small-Signal Model MOSFET

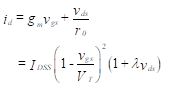

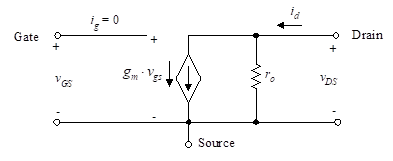

Zdaj želimo pogledati postopne učinke, povezane z enačbo. Trije parametri vezja v tej enačbi, iD, vGS in vDS sestavljeni iz obeh dc (pristranskost) in ac komponente (zato smo v izrazih uporabili zgornje indeksne zapise). Zanima nas ac komponente za model majhnega signala. Vidimo, da je odtočni tok odvisen od dveh napetosti, od vrat do vira in od odvoda do vira. Za inkrementalne vrednosti lahko to razmerje zapišemo kot

(14)

V enačbi (14), gm is prepustnost naprej in r0 je izhodna upornost. Njihove vrednosti najdemo z uporabo delnih derivatov v enačbi (5). Tako

(15)

Približek v enačbi (15) je rezultat opazovanja λ če je majhna. Enačba (14) vodi do modela majhnega signala na sliki 12.

Slika 12 - Model z majhnim signalom MOSFET

TEK - 2. Kovinsko-oksidni polprevodnik FET (MOSFET)

TEK - 2. Kovinsko-oksidni polprevodnik FET (MOSFET) PREJŠNJA-1. Prednosti in slabosti FETs

PREJŠNJA-1. Prednosti in slabosti FETs