5. Integrirana vezja MOSFET

Integrirana vezja MOSFET

Ko so MOSFET tranzistorji izdelani kot del integriranega vezja, praktični vidiki zahtevajo dve večji spremembi konfiguracij vezja. Prvič, veliki sklopni in obvodni kondenzatorji, ki se uporabljajo v diskretnih ojačevalnikih, zaradi majhnosti ne morejo biti praktično izdelani v integriranih vezjih. To pomanjkljivost obvladujemo s proizvajanjem ojačevalnikov z neposredno povezavo.

Druga velika sprememba je, da ne moremo zlahka izdelati uporov, ki se uporabljajo kot del pristranskih vezij. Namesto tega uporabljamo aktivne obremenitve in tokovne vire, ki jih sestavljajo MOS tranzistorji.

Integrirana vezja uporabljajo tako NMOS kot PMOS vezje. CMOS je pogostejša v digitalnih vezjih, medtem ko se NMOS običajno uporablja za IC-je z večjo gostoto (tj. Več funkcij na čip).

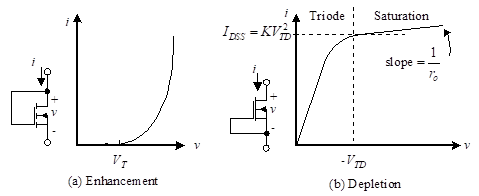

Simulacija aktivnih obremenitev izkorišča nagib karakterističnih krivulj MOS. Slika 23 prikazuje dve vrsti aktivnih obremenitev. Na sliki 23 (a) je prikazana obremenitev NMOS, medtem ko je 23 (b) pokazal obremenitev z zmanjšanjem NMOS. Na sliki so prikazane tudi ustrezne karakteristične krivulje.

Slika 23 - Aktivne obremenitve

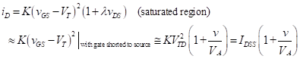

Za povečanje obremenitve NMOS je razmerje med napetostjo in tokom podano z

![]()

(29)

Enakovredna upornost te konfiguracije je 1 /gm, kjer je vrednost prepustnosti tista, ki velja za pristransko točko.

Obremenitev z izpraznjenostjo NMOS ima enakovredno odpornost, ki jo določa naklon karakteristik, podan v naslednji enačbi

(30)

5.1 Biasing integriranih vezij MOSFET

Zdaj, ko imamo dve tehniki za simulacijo aktivnih bremen, lahko rešimo vprašanje pristranskosti. Aktivno obremenitev uporabljamo namesto upornosti obremenitve v kateri koli konfiguraciji vezja. Da bi prikazali tehniko za analizo teh analiz, si oglejte ojačevalnik NMOS, ki uporablja povečano obremenitev, kot je prikazano na sliki 24.

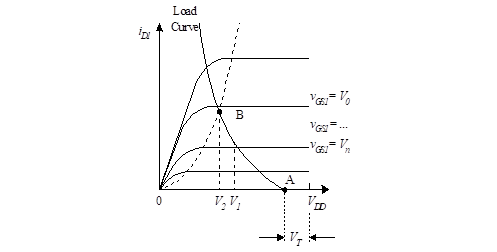

Tranzistor je označen Q2 nadomešča RD našega prejšnjega vezja. Za določitev mirujoče delovne točke uporabljamo enake tehnike, kot smo jih storili v oddelku 4, "Konfiguracije ojačevalnika FET in pristranskost", le da nadomestimo grafično značilnost ojačevalne obremenitve za uporovno obremenitveno črto. To pomeni, da moramo najti sočasno rešitev lastnosti tranzistorja FET z enačbo za tovorno črto. To lahko naredimo grafično, kot je prikazano na sliki 25.

Parametrične krivulje so karakteristične krivulje za ojačevalni tranzistor Q1. Napetostna / aktualna karakteristika aktivne obremenitve, Q2 so tiste na sliki 23. Izhodna napetost, vven, je razlika med VDD in napetost na aktivni obremenitvi. Tok v aktivni obremenitvi je enak kot odvodni tok v ojačevalnem tranzistorju. Zato konstruiramo linijo obremenitve tako, da vzamemo premaknjeno zrcalno sliko karakteristike slike 23. Delovna točka je presečišče te krivulje z ustrezno karakteristično krivuljo tranzistorja. Moramo najti napetost od vrat do vira, da vemo, katero krivuljo tranzistorja izberemo. Kot bomo videli v nadaljevanju, je napetost vhodne pristranosti pogosto zamenjana z aktivnim izvorom toka.

Slika 25 - grafična rešitev za točko Q

Zdaj, ko vemo, kako simulirati aktivno obremenitev, usmerimo našo pozornost na generiranje referenčnega toka, ki se bo uporabljal kot del vhodnega vezja. Ti trenutni viri se uporabljajo na enak način, kot smo jih uporabljali za premikanje ojačevalnika BJT.

Slika 26 - Trenutna ogledala

Analiziramo MOSFET trenutna ogledalo. Trenutno sliko je prikazano na sliki 26. Predpostavlja se, da sta dva tranzistorja popolnoma usklajena. Izhodni tok je odtočni tok Q2in referenčne tokovne pogone Q1. Če so tranzistorji popolnoma usklajeni, bo izhodni tok popolnoma enak referenčnemu toku. To drži, saj so tranzistorji povezani vzporedno. Tako kot v primeru trenutnega zrcala BJT, lahko referenčni tok generiramo z uporabo referenčne napetosti na referenčni upor, kot je prikazano na sliki 26 (b).

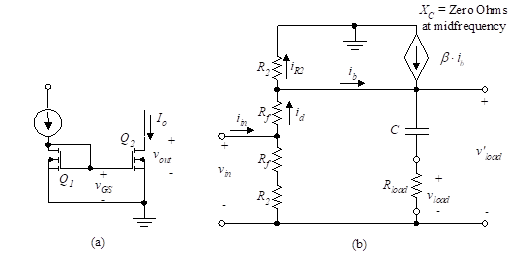

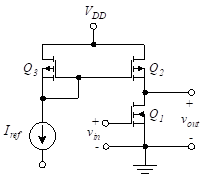

Prenos različnih subcircuits skupaj (tj, aktivno obremenitev in referenčni tok) rezultate v CMOS ojačevalnik na sliki 27.

Dobitek tega ojačevalnika je podan z

![]()

(31)

Slika 27 - CMOS ojačevalnik

Učinek telesa 5.2

Naša razprava o poglavju „2. Kovinsko-oksidni polprevodnik FET (MOSFET) «se nanaša na podlago (ali telo) MOSFET-a. Ta podlaga igra pomembno vlogo pri vzpostavljanju kanala. Pri delovanju diskretnih MOSFET-jev je telo pogosto povezano z virom energije. V takih primerih podlaga nima neposrednega vpliva na delovanje naprave in veljajo krivulje, razvite prej v tem poglavju.

Stanje se spremeni, ko so MOSFET-i izdelani kot del integriranih vezij. V takih primerih substrat vsakega posameznega tranzistorja ni izoliran od drugih substratov. Podlaga se pogosto deli med vse MOSFET-e na čipu. V PMOS IC, skupni substrat bi bilo povezano z najbolj pozitivni vir terminal, medtem ko je v NMOS je povezan z zemljo (ali negativno dobavo, če je prisotna). To vzpostavlja obratno pristranskost med izvorom in telesom vsakega tranzistorja. Posledica te povratne pristranskosti je sprememba obratovalnih karakteristik. Na primer, v n-kanalna naprava, učinkovito poveča prag (VT). Znesek, pri katerem se spremeni prag, je odvisen od fizikalnih parametrov in konstrukcije naprave. Za NMOS se lahko ta sprememba približa s

![]()

(32)

V enačbi (32) je γ parameter naprave, ki se spreminja med 0.3 in 1 (V)-1 / 2). VSB je napetost od vira do telesa in je Fermijev potencial. To je lastnost materiala, tipična vrednost pa je 0.3 V za silicij.

TOK - 5. Vgrajena vezja MOSFET

TOK - 5. Vgrajena vezja MOSFET PREJŠNJA-4. Konfiguracije in dvigovanje FET ojačevalnikov

PREJŠNJA-4. Konfiguracije in dvigovanje FET ojačevalnikov