2. Metalloxid Halvledare FET (MOSFET)

Metalloxid Halvledare FET (MOSFET)

Metalloxidhalvledaren FET (MOSFET) är en fyra terminalanordning. Terminalerna är källa (S), grind (G) och dränera (D). De substrat or kropp bildar den fjärde terminalen. MOSFET är konstruerad med portanslutningen isolerad från kanalen med en dielektrisk kiseldioxid. MOSFET kan också vara tömning or förbättringsläge. Vi definierar dessa två termer inom kort.

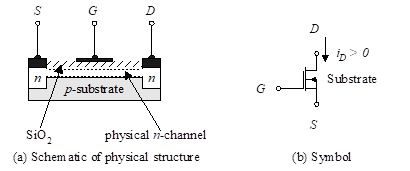

Figur 1 - n-kanalutarmning MOSFET

MOSFETs kallas ibland som IGFETs (Isolerade Gate Field Effect Effect Transistors) på grund av SiO2 skikt som används som en isolator mellan grinden och substratet. Vi börjar vår analys med MOSFET-uttömningsläget. Precis som BJTs kan vara heller npn or pnp, MOSFET kan också vara n-kanalen (NMOS) eller p-kanalen (PMOS). Figur 1 illustrerar den fysiska strukturen och symbolen för en n-kanalutarmning MOSFET. Observera att substratet är anslutet till källkontakten. Detta kommer nästan alltid att vara fallet.

Utarmningen MOSFET är konstruerad med a fysisk kanal införd mellan avloppet och källan. Som ett resultat, när en spänning, vDS, appliceras mellan dränering och källa, en ström, iD, existerar mellan dränering och källa även om grindanslutning G förblir inkopplad (vGS = 0 V).

Byggandet av n-kanalutarmning MOSFET börjar med p-doped kisel. De n-dopade käll- och dräneringsbrunnar bildar lågmotståndsförbindelser mellan ändarna av n-kanalen, som visas i figuren 1. Ett tunt lager av kiseldioxid deponeras som täcker området mellan källan och avloppet. SiO2 är en isolator. Ett aluminiumskikt deponeras på kiseldioxidisolatorn för att bilda grindsterminalen. I drift, en negativ vGS skjuter elektroner ut ur kanalområdet och därigenom tömmer kanalen. När vGS når en viss spänning, VT, kanalen är klyvas av. Positiva värden på vGS Öka kanalstorleken, vilket resulterar i en ökning av dräneringsströmmen. Utarmningen MOSFET kan fungera med antingen positiva eller negativa värden på vGS. Eftersom porten är isolerad från kanalen är grindströmmen försumbar liten (i storleksordningen 10-12 EN).

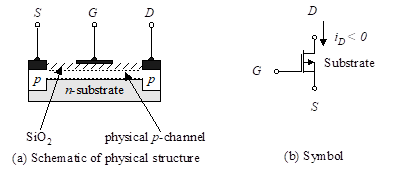

Figur 2 - p-kanalutarmning MOSFET

Figur 2 kan jämföras med Figur 1, förutom att vi har ändrat n-kanalutarmning MOSFET till a p-kanalutarmning MOSFET.

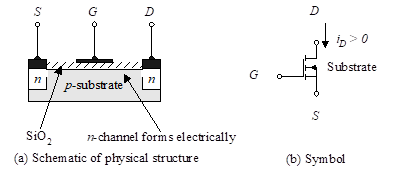

Smakämnen n-kanalförstärkning MOSFET illustreras i figur 3 tillsammans med kretssymbolen. Detta är den vanligaste formen av fälteffekttransistor.

Figur 3 - n-kanalförbättring MOSFET

Smakämnen n-kanalförstärkning MOSFET skiljer sig från uttömningen MOSFET genom att inte ha den tunna n-lager. Det kräver en positiv spänning mellan porten och källan för att upprätta en kanal. Denna kanal bildas av åtgärden av en positiv spänning från grind till källa, vGS, som lockar elektroner från substratregionen mellan n-doped avlopp och källan. Positiv vGS orsakar att elektroner ackumuleras vid ytan under oxidskiktet. När spänningen når ett tröskelvärde, VT, tillräckligt många elektroner lockas till denna region för att få det att fungera som en ledande n-kanalisera. Ingen märkbar dräneringsström, iD existerar till vGS överstiger VT.

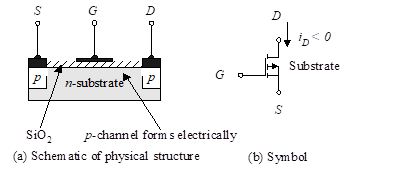

Figur 4 kan jämföras med Figur 3, förutom att vi har ändrat n-kanalförbättring MOSFET till en p-kanalförstärkning MOSFET.

Figur 4 - p-kanalförstärkning MOSFET

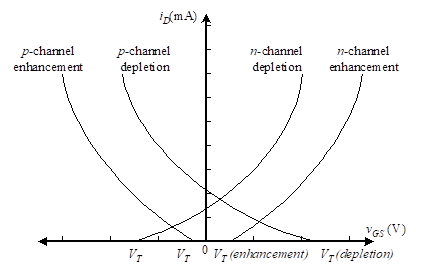

Som en sammanfattning visar MOSFET-familjen identifieringen iD kontra vGS kurvor som visas i figur 5. Varje karaktäristisk kurva är utvecklad med tillräcklig avloppsspänning vDS för att behålla enheten i det normala driftsområdet för iD kontra vDS kurvor. Diskussionen i senare avsnitt definierar tröskelspänningen VT för både MOSFET-förstärkare och uttömningsmosfeter.

Figur 5 - iD kontra vGS egenskaper hos MOSFET-familjen för tillräcklig avloppsspänning VDS

2.1 Enhancement-Mode MOSFET-terminalegenskaper

Nu när vi har presenterat den grundläggande strukturen och basen för drift av MOSFET använder vi ett tillvägagångssätt för att undersöka terminalbeteendet hos enhancement-mode-enheten. Låt oss först göra några allmänna observationer från figur 1. Tänk på det normala strömflödet i MOSFET som från avloppet till källan (precis som i BJT är det mellan kollektor och emitter). Som med npn BJT finns två back-to-back-dioder mellan dränering och källa. Därför måste vi tillämpa externa spänningar i porten för att tillåta strömflöde mellan avloppet och källan.

Om vi markerade källan och tillämpa en positiv spänning på porten, är den spänningen effektivt gate-to-source spänningen. Den positiva grindspänningen lockar elektroner och avstötar hål. När spänningen överstiger tröskelvärdet (VT) attraheras tillräckligt många elektroner för att bilda en ledande kanal mellan dränering och källa. Vid denna tidpunkt sätts transistorn på och strömmen är en funktion av båda vGS och vDS. Det bör vara klart att VT är ett positivt tal för en n-kanalsenhet och ett negativt tal för a pkanalkanal.

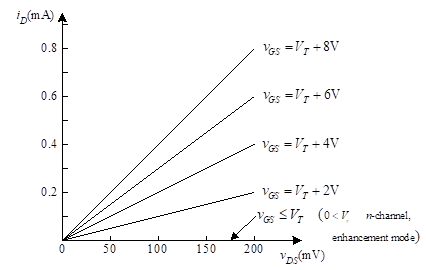

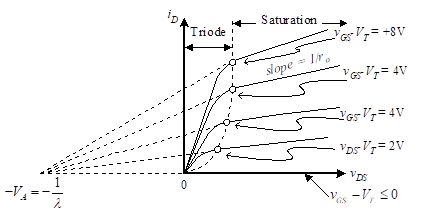

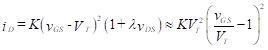

När en kanal har skapats (dvs. vGS >VT) kan strömflödet inträffa i den här kanalen mellan dränering och källa. Detta strömflöde beror på vDS, men det beror också på vGS. När vGS bara knappt överskrider tröskelspänningen, kan mycket lite ström flöda. Som vGS ökar utöver tröskeln, kanalen innehåller fler bärare och högre strömmar är möjliga. Figur 6 visar förhållandet mellan iD och vDS var vGS är en parameter. Observera att för vGS mindre än tröskeln, ingen ström strömmar. För högre vGS, Relationen mellan iD och vDS är ungefär linjär vilket indikerar att MOSFET beter sig som ett motstånd vars motstånd beror på vGS.

Figur 6 -iD kontra vDS för ett förbättringsläge n-kanalen MOSFET när vDS är liten

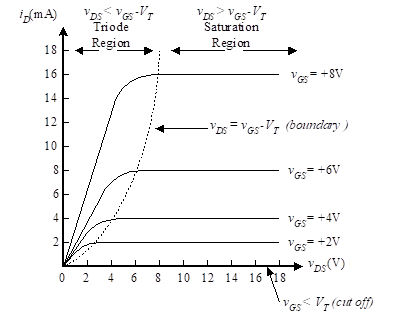

Kurvorna i Figur 6 ser ut som raka linjer. Men de kommer inte fortsätta som raka linjer när vDS blir större. Minns att en positiv grindspänning används för att skapa ledningskanalen. Det gör det genom att locka till elektroner. Den positiva avloppsspänningen gör samma sak. När vi närmar oss kanalens avloppsände närmar sig spänningen som skapar kanalen vGS-vDS eftersom de två källorna motsätter varandra varandra. När denna skillnad är mindre än VT, kanalen finns inte längre för hela utrymmet mellan källa och dränering. Kanalen är tvungen vid avloppsänden, och ytterligare ökar i vDS resultera inte i någon ökning i iD. Detta är känt som det normala driftsområdet eller mättnad regionen som visas i figur 7 av den horisontella sektionen av karaktäristiska kurvor. När skillnaden är större än VT, vi kallar det här triod läge, eftersom potentialerna vid alla tre terminalerna starkt påverkar strömmen.

Den tidigare diskussionen leder till driftskurvorna i Figur 7.

Figur 7 -iD kontra vGS för en MOSFET-förstärkningsläge

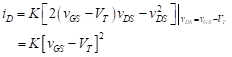

Övergången mellan trioden och den normala operationsregionen (refererad till som mättningsregionen och ofta identifierad som funktion i nypa-läge) visas som streckad linje i figur 7, där

![]()

(1)

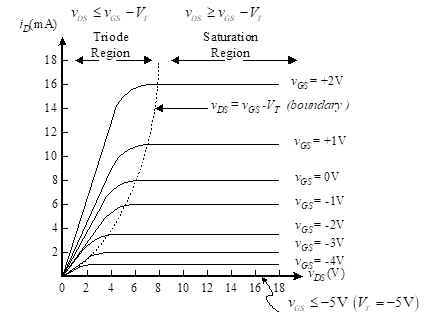

Vid triodregionens gräns följer kurvornas knä ungefär förhållandet,

![]()

(2)

I ekvation (2) är K en konstant för en given anordning. Dess värde beror på enhetens dimensioner och material som används vid konstruktionen. Konstanten ges av,

![]()

(3)

I denna ekvation, μn är elektronmobiliteten; Coxid, oxidkapacitansen är kapacitansen per enhetens område av grinden; W är portens bredd; L är portens längd. Ekvation indikerar ett komplicerat och olinjärt förhållande mellan iD och de två spänningarna, vDS och vGS. Eftersom vi skulle vilja dränera nuvarande att variera ungefär linjärt med vGS (oberoende av vDS) används FET generellt inte i triodregionen.

Vi vill nu hitta en ekvation för driftkurvorna i mättningsområdet. Vi kan fastställa värdena vid övergången mellan triod och mättningsregionen genom att utvärdera ekvation (2) vid övergången (knäet). Det är,

(4)

Denna ekvation fastställer storleken av dräneringsströmmen vid gränsen (streckad linje i figur 8) som en funktion av spänningen från grind till källa vGS. Om det behövs kan vi ta hänsyn till den svaga lutningen av karaktäristiska kurvor i mättnadsområdet genom att lägga till en linjär faktor.

![]()

(5)

I ekvation (5) λ är en liten konstant (lutningen på den närmre horisontella delen av de karakteristiska kurvorna som visas i figur 8). Det är vanligtvis mindre än 0.001 (V-1). Sedan

![]()

(6)

Alla våra tidigare diskussioner handlade om NMOS transistorn. Vi diskuterar nu kort de nödvändiga ändringarna för PMOS. För PMOS, värdena för vDS kommer att vara negativ. För att skapa en kanal i PMOS, ![]() .

.

Figur 8 - Terminalegenskaper för en MOSFET-transistor

De enda förändringarna från egenskaperna hos NMOS-transistorer (Figur 7) är att den horisontella axeln nu är -vDS istället för + vDS och parametriska kurvorna representerar högre avloppsström när portspänningen minskar (i stället för att öka för NMOS transistorn). Kurvorna för ökande nuvarande värden motsvarar mer negativ grindspänning. När vGS > VT, transistorn är avskuren. För förstärkning PMOS, VT är negativ, och för uttömning PMOS, VT är positiv.

Ekvationen för strömmen vid trioderegionens övergång för PMOS-transistorn är identisk med den för NMOS. Det är,

![]()

(7)

Observera att vGS och vDS är båda negativa kvantiteter. Ekvationen för mättningsområdet i PMOS-transistorn är också identisk med NMOS. Det är,

(8)

Observera att λ är negativ för PMOS-transistorer eftersom kurvväxlingshastigheten (![]() ) är negativ.

) är negativ.

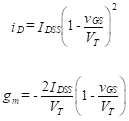

Tar det partiella derivatet av båda sidor av ekvation (6) med avseende på vGS, ![]() , vi får

, vi får

![]()

(9)

Vi föredrar värdet av gm att vara konstant, speciellt för stora signalsvingningar. Vi kan dock bara approximera detta villkor om vi använder FET för små signaler. För stora signalförhållanden kan förvrängning av vågformen vara oacceptabel i vissa applikationer.

2.2 Depletion-Mode MOSFET

I föregående avsnitt behandlades MOSFET-förstärkningsläget. Vi kontrasterar nu detta till MOSFET-uttömningsläget. För n-kanalförbättringsläge för att förvärva en kanal som vi var tvungna att tillämpa en positiv spänning på porten. Denna spänning måste vara stor nog för att tvinga tillräckligt antal mobila elektroner för att producera en ström i en inducerad kanal.

Figur 9 - Nätkanal MOSFET

I n-kanalutarmningsläge MOSFET, vi behöver inte denna positiva spänning eftersom vi har en fysiskt implanterad kanal. Detta gör att vi kan ha ström mellan avlopps- och källanslutningar även med negativa spänningar som appliceras på grinden. Naturligtvis finns det en gräns för mängden negativ spänning som kan appliceras på grinden medan den fortfarande har strömflöde mellan avlopp och källa. Denna gräns identifieras åter som tröskelspänningen, VT. Förändringen från förbättringsläget är att grind-till-källspänningen nu kan vara antingen negativ eller positiv, som visas i figur 9.

Ekvationerna som definierar driften av uttömningsmodus MOSFET är väldigt lik dem i förbättringsläget. Värdet av dräneringsströmmen när vGS noll är identifierad som IDSS. Detta kallas ofta som avlopps-mättnadsströmmen, Eller nollgränsavloppsström. Att jämföra ekvationerna i förstärkningsläge MOSFET med de av uttömningsläget finner vi

![]()

(10)

Vi hittar då,

(11)

MOSFET-utlösningsläge finns i diskret form, eller de kan tillverkas på integrerade kretsar i kombination med förbättringsmodstyper. Detta inkluderar båda p-typ och n-typ. Detta möjliggör mer flexibilitet i kretsdesignstekniker.

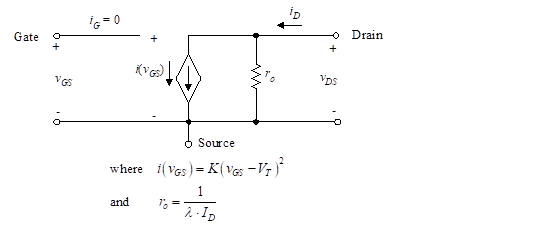

2.3 Stor signalkvivalent krets

Vi vill nu utveckla en ekvivalent krets som representerar storignalegenskaperna i Figur 8 [ekvation (5) eller (8)] i mättningsområdet. Observera att dräneringsströmmen, iD, beror på vGS och vDS. För en konstant gate-to-source-spänning arbetar vi längs en av figurens parametriska kurvor, och förhållandet är en ungefär rak linje. Ett linjärt förhållande mellan ström och spänning modelleras av ett motstånd. Den ekvivalenta kretsen består därför av ett motstånd parallellt med strömkällan där värdet på strömkällan fastställer delen av avloppsströmmen pga. vGS. Kurvens lutning beror på vGS. Lutningen är det partiella derivatet,

![]()

(12)

var r0 är inkrementell utgångsresistans. Vi ser från ekvation [(5) eller (8)] som detta motstånd ges av

![]()

(13)

där vi använder övre fall VGS för att indikera att resistansen definieras för ett särskilt konstant värde av gate-to-source-spänning. Den slutliga approximationen i ekvation (13) kommer från ekvation (5) med antagandet att λ är liten. Motståndet är därför omvänt proportionellt mot biasströmmen, ID. Den stora signalekvivalenta modellen ges sedan av Figur 11 där r0 är som utvecklad i ekvation (13).

Figur 11 - Stor-signalekvivalent krets

2.4 Små signal modell av MOSFET

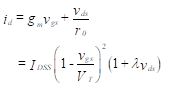

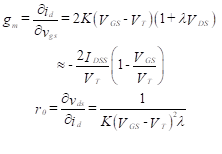

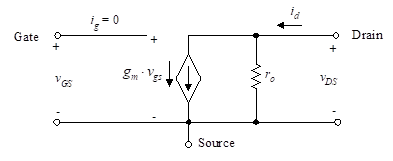

Vi vill nu titta på inkrementella effekter relaterade till ekvation. De tre kretsparametrarna i den ekvationen, iD, vGS och vDS består av båda dc (bias) och ac komponenter (det är därför vi har använt stora bokstäver i uttryck). Vi är intresserade av ac komponenter för småsignalmodellen. Vi ser att avloppsströmmen är beroende av två spänningar, gate-to-source och drain-to-source. För inkrementella värden kan vi skriva detta förhållande som

(14)

I ekvation (14) gm is den främre transkonduktansen och r0 är utmatningsmotståndet. Deras värden återfinns genom att ta partiella derivat i ekvation (5). Således,

(15)

Nivån i ekvation (15) beror på observationen att λ om små. Ekvation (14) leder till små signalmodellen i Figur 12.

Figur 12 - Small-signal MOSFET-modell

STRÖM - 2. Metalloxid halvledare FET (MOSFET)

STRÖM - 2. Metalloxid halvledare FET (MOSFET) TIDLIGARE - 1. Fördelar och nackdelar med FET

TIDLIGARE - 1. Fördelar och nackdelar med FET