2. Металооксидний напівпровідниковий транзистор (MOSFET)

Металооксидний напівпровідниковий транзистор (MOSFET)

Металооксидний напівпровідник FET (MOSFET) - це чотири кінцеві пристрої. Термінали є джерело (S), ворота (G) та сток (D), субстрат or тіло утворює четвертий термінал. МОП-транзистор побудований з висновком затвора, ізольованим від каналу діелектриком діоксиду кремнію. MOSFETs може бути або виснаження or режиму розширення. Ми визначаємо ці два терміни найближчим часом.

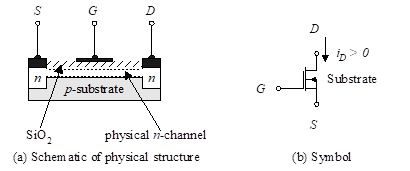

Малюнок 1 - виснаження каналу n-MOSFET

MOSFETs іноді називають IGFETs (ізолюючими воротами польових транзисторів) через SiO2 шар, що використовується в якості ізолятора між затвором і підкладкою. Ми починаємо наш аналіз з вичерпанням режиму MOSFET. Так само, як і BJTs npn or PNP, MOSFETs може бути або n-канал (NMOS) або p-канал (PMOS). Малюнок 1 ілюструє фізичну структуру і символ для nвиснаження каналу MOSFET. Зверніть увагу, що підкладка підключена до вихідного терміналу. Це майже завжди буде так.

Виснаження MOSFET будується з a фізичний канал вставлений між стоком і джерелом. В результаті, коли напруга, vDS, застосовується між стоком і джерелом, струмом, iD, існує між стоком і джерелом, хоча термінал G затвора залишається незв'язаним (vGS = 0 V).

Будівництво nВиснаження каналу MOSFET починається з pкремній. The nДжерела-дренажні і дренажні свердловини утворюють низькоомні сполуки між кінцями n-канал, як показано на малюнку 1. Наносять тонкий шар діоксиду кремнію, що покриває область між джерелом і каналом. SiO2 є ізолятором. На ізолятор діоксиду кремнію наносять шар алюмінію, щоб сформувати затвор. В операції негативний vGS виштовхує електрони з області каналу, тим самим вичерпуючи канал. Коли vGS досягає певної напруги, VT, канал є відщипується. Позитивні значення vGS збільшити розмір каналу, що призводить до збільшення струму стоку. Виснаження MOSFET може працювати як з позитивними, так і з негативними значеннями vGS. Оскільки заслінка ізольована від каналу, струм затвора незначно малий (на замовлення 10-12 А).

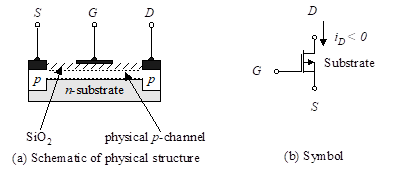

Малюнок 2 - p-канал виснаження MOSFET

Малюнок 2 можна порівняти з малюнком 1, за винятком того, що ми змінили n-канальний виснаження MOSFET до a pвиснаження каналу MOSFET.

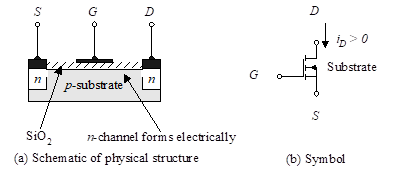

Команда nПідсилення каналів MOSFET ілюструється на малюнку 3 разом з символом схеми. Це найбільш поширена форма польового транзистора.

Малюнок 3 - поліпшення n-канального MOSFET

Команда nПідсилення каналів MOSFET відрізняється від виснаження MOSFET, не маючи тонкого n-шару. Це вимагає позитивного напруги між затвором і джерелом для встановлення каналу. Цей канал утворений дією позитивної напруги від воріт до джерела, vGS, який притягує електрони з області субстрату між n-наділений стік і джерело. Позитивний vGS призводить до накопичення електронів на поверхні під шаром оксиду. Коли напруга досягає порогу, VTдостатню кількість електронів притягується до цієї області, щоб змусити її діяти як провідник n-канал. Немає помітного струму стоку, iD існує до vGS перевищує VT.

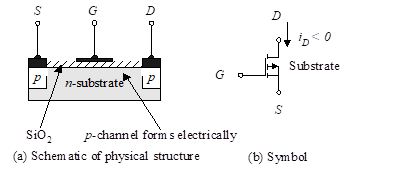

Малюнок 4 можна порівняти з малюнком 3, за винятком того, що ми змінили n-канальне покращення MOSFET до a p-канальне покращення MOSFET.

Малюнок 4 - p-канальний поліпшення MOSFET

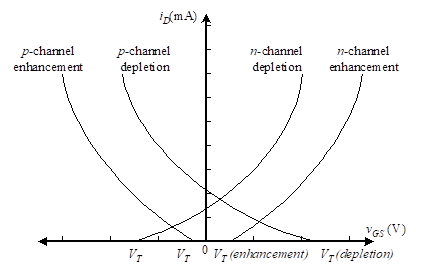

Як резюме, сім'я MOSFET демонструє ідентифікацію iD в порівнянні з vGS криві, показані на малюнку 5. Кожна характеристична крива розроблена з достатньою напругою вихідного джерела vDS для підтримки пристрою в звичайній робочій області iD в порівнянні з vDS криві. Обговорення в наступних розділах визначатиме порогову напругу VT для покращення MOSFETs і виснаження MOSFETs.

Малюнок 5 - iD в порівнянні з vGS характеристики сімейства MOSFET для достатньої напруги джерела зливу VDS

Характеристики терміналу MOSFET з покращенням режиму 2.1

Тепер, коли ми представили базову структуру та основи роботи MOSFET, ми використовуємо підхід для вивчення поведінки терміналу пристрою в режимі вдосконалення. Давайте спочатку зробимо деякі загальні спостереження з рисунка 1. Подумайте про нормальний потік струму в MOSFET як про те, що йде від стоку до джерела (так само, як і в BJT, він знаходиться між колектором і випромінювачем). Як і в npn BJT, два back-to-back діоди існують між стоку і джерела. Тому до воріт необхідно застосувати зовнішні напруги, щоб струм міг протікати між стоком і джерелом.

Якщо ми заземлити джерело, і застосувати позитивне напруга до воріт, це напруга є фактично напругою ворота до джерела. Позитивна напруга затвора притягує електрони і відштовхує отвори. Коли напруга перевищує поріг (VT), достатньо електронів притягується до утворення провідного каналу між стоком і джерелом. На цьому етапі транзистор включається і струм є функцією обох vGS та vDS. Повинно бути зрозуміло, що VT - позитивне число для n-канальний пристрій і негативне число для a p-канальний пристрій.

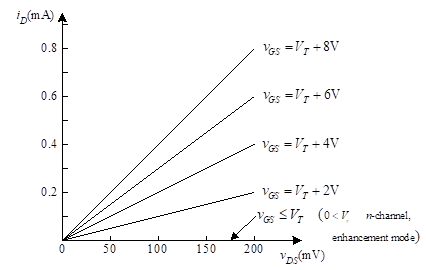

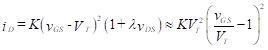

Після створення каналу (тобто vGS >VT), поточний потік може відбуватися в цьому каналі між каналом і джерелом. Цей струм залежить від vDS, але це також залежить від vGS. Коли vGS тільки ледве перевищує порогове напруга, дуже мало струму може протікати. Як vGS збільшується за межі порога, канал містить більше носіїв і можливі більш високі струми. На малюнку 6 показано взаємозв'язок між ними iD та vDS де vGS є параметром. Зверніть увагу, що для vGS менше порога, поточних потоків немає. Для вищих vGS, відносини між ними iD та vDS є приблизно лінійним, що вказує, що MOSFET веде себе як резистор, від якого залежить опір vGS.

Малюнок 6 -iD в порівнянні з vDS для режиму розширення n-канальний MOSFET коли vDS невеликий

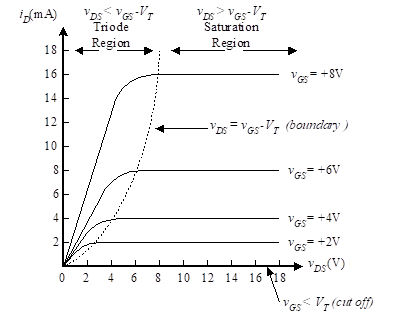

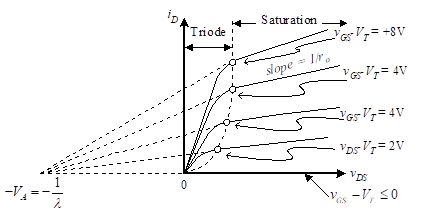

Криві на малюнку 6 виглядають як прямі. Однак, вони не будуть продовжуватися як прямі лінії vDS стає більше. Нагадаємо, що для створення каналу провідності використовується позитивне напруга затвора. Він робить це за допомогою залучення електронів. Позитивна напруга стоку робить те ж саме. Коли ми наближаємося до зливного каналу каналу, наближається напруга, що створює канал vGS-vDS оскільки два джерела протистоять один одному. При цьому різниця менше VT, канал більше не існує для всього простору між джерелом і каналом. Канал є обмежений на кінці зливу, і далі збільшується в vDS не призводять до збільшення в iD. Це відомо як звичайний діючий регіон або насичення Область показана на малюнку 7 по горизонтальному перетину характеристичних кривих. Коли різниця більше VT, ми називаємо це триод режим, тому що потенціали на всіх трьох терміналах сильно впливають на струм.

Попереднє обговорення призводить до робочих кривих на малюнку 7.

Малюнок 7 -iD в порівнянні з vGS для розширеного режиму MOSFET

Перехід між тріодом і нормальною робочою областю (що називається областю насичення і часто ідентифікований як операція в режимі віджимання) операції показаний як пунктирна лінія на малюнку 7,

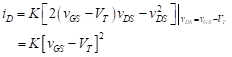

![]()

(1)

На кордоні тріодної області коліна кривих приблизно дотримуються співвідношення,

![]()

(2)

У рівнянні (2) K є константою для даного пристрою. Його величина залежить від розмірів пристрою та матеріалів, що використовуються при його будівництві. Константа задається,

![]()

(3)

У цьому рівнянні, μn - рухливість електронів; Cоксид, оксидна ємність, - ємність на одиницю площі затвора; W ширина воріт; L - довжина воріт. Рівняння вказує на складну і нелінійну залежність між iD і два напруги, vDS та vGS. Оскільки ми хотіли б, щоб струм зливу коливався приблизно лінійно vGS (незалежно від vDS), ТНЕ зазвичай не використовується в тріодної області.

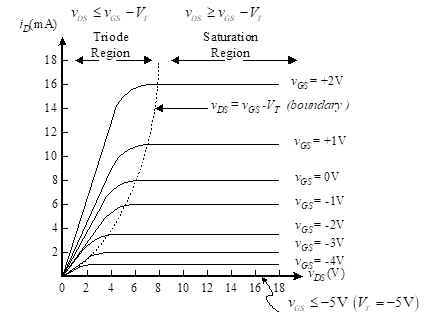

Тепер ми хочемо знайти рівняння для робочих кривих в області насичення. Ми можемо встановити значення при переході між тріодом і областю насичення, оцінюючи Рівняння (2) на переході (коліно). Це,

(4)

Це рівняння встановлює величину струму стоку на кордоні (пунктирна лінія на малюнку 8) як функція напруги від джерела до джерела. vGS. При необхідності можна пояснити невеликий нахил характеристичних кривих в області насичення шляхом додавання лінійного фактора.

![]()

(5)

У рівнянні (5), λ - невелика константа (нахил близького горизонтального ділянки характеристичних кривих, показаний на малюнку 8). Він зазвичай менше 0.001 (V-1). Потім

![]()

(6)

Всі наші попередні дискусії стосувалися транзистора NMOS. Тепер ми коротко обговоримо необхідні модифікації для PMOS. Для PMOS, значення vDS буде негативним. Крім того, для створення каналу в PMOS, ![]() .

.

Малюнок 8 - Термінальні характеристики транзистора MOSFET

Єдина зміна від характеристик транзисторів NMOS (рисунок 7) полягає в тому, що горизонтальна вісь тепер -vDS замість + vDS і параметричні криві представляють більш високий струм стоку, коли напруга затвора зменшується (замість збільшення для транзистора NMOS). Криві для збільшення значень струму відповідають більшій негативній напрузі затвора. Коли vGS > VT, транзистор відсічний. Для покращення PMOS, VT є від'ємним, а для вичерпання PMOS - VT позитивний.

Рівняння для струму в переході триодної області для транзистора PMOS ідентичне такому для NMOS. Це,

![]()

(7)

Зверніть увагу, що vGS та vDS обидві негативні величини. Рівняння для області насичення в транзисторі PMOS також ідентично такому для NMOS. Це,

(8)

Зверніть увагу, що λ негативний для транзисторів PMOS, оскільки швидкість зміни кривої (![]() ) є негативним.

) є негативним.

Приймаючи часткову похідну від обох сторін рівняння (6) по відношенню до vGS, ![]() , ми отримуємо

, ми отримуємо

![]()

(9)

Ми віддаємо перевагу вартості gm бути постійними, особливо для великих коливань сигналу. Однак, ми можемо лише наблизити цю умову, якщо ми використовуємо FET для невеликих додатків сигналу. Для великих умов сигналу спотворення сигналу може бути неприйнятним у деяких додатках.

2.2 MOSFET з вичерпаним режимом

Попередній розділ стосувався MOSFET розширеного режиму. Тепер ми порівнюємо це з MOSFET з режимом виснаження. Для n-канальний режим підвищення, для придбання каналу нам довелося застосувати позитивне напруга на затворі. Ця напруга повинна була бути достатньо великою, щоб змусити достатню кількість мобільних електронів для створення струму в індукованому каналі.

Малюнок 9 - режим виснаження n-канального MOSFET

У n-режим виснаження каналу MOSFET, нам не потрібна ця позитивна напруга, оскільки у нас є імплантований фізично канал. Це дозволяє нам мати струм між стоками стоку та джерелом навіть при негативних напругах, що подаються на затвор. Звичайно, існує обмеження кількості негативної напруги, яке може подаватися на затвор, маючи при цьому струм струму між стоком і джерелом. Ця межа знову визначається як порогова напруга, VT. Зміна від режиму вдосконалення полягає в тому, що напруга від джерела до джерела тепер може бути як негативною, так і позитивною, як показано на малюнку 9.

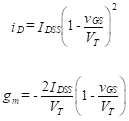

Рівняння, які визначають роботу MOSFET з виснаженим режимом, дуже схожі на ті, що використовуються в режимі підвищення. Значення струму стоку при vGS нуль ідентифікується як IDSS. Це часто називають струм насичення вихідного джерела, Або нульовий струм стоку стоку. Порівнюючи рівняння розширеного режиму MOSFET з рівняннями режиму виснаження, ми знаходимо

![]()

(10)

Потім ми знаходимо,

(11)

Режим виснаження МОП-транзистори доступні в дискретній формі, або вони можуть бути виготовлені на мікросхемах інтегральних мікросхем поряд з типом режимів підвищення. Це включає в себе обидва p-типу і n-типу. Це дозволяє підвищити гнучкість методів схемотехніки.

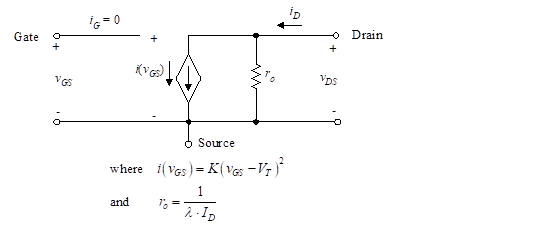

2.3 Велика сигнальна схема

Тепер ми хочемо розробити еквівалентну схему, яка представляє характеристики великого сигналу на рисунку 8 [Рівняння (5) або (8)] в області насичення. Відзначимо, що струм стоку, iD, залежить від vGS та vDS. Для постійної напруги від джерела до джерела ми працюємо вздовж однієї з параметричних кривих малюнка, і співвідношення є приблизно прямою лінією. Прямолінійна залежність між струмом і напругою моделюється резистором. Отже, еквівалентна схема складається з резистора, паралельно джерелу струму, де значення джерела струму встановлює частину струму стоку за рахунок vGS. Нахил кривої залежить від vGS. Нахил є частковою похідною,

![]()

(12)

де r0 є додатковим вихідним опором. Ми бачимо з Рівняння [(5) або (8)], що цей опір дається

![]()

(13)

де ми використовуємо верхній регістр VGS для вказівки на те, що опір визначається для певного постійного значення напруги від воріт до джерела. Остаточне наближення в рівнянні (13) випливає з рівняння (5) з припущенням, що λ невеликий. Таким чином, опір обернено пропорційно струму зміщення, ID. Модель великого еквівалентного сигналу потім задається на малюнку 11, де r0 як розроблено в Рівнянні (13).

Малюнок 11 - схема великого сигналу

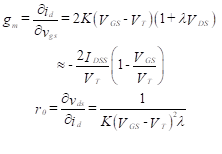

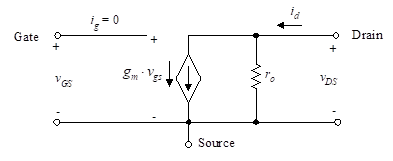

2.4 Малосигнальна модель MOSFET

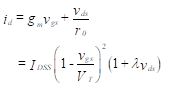

Тепер ми хочемо подивитися на додаткові ефекти, пов'язані з рівнянням. Три параметри ланцюга в цьому рівнянні, iD, vGS та vDS складаються з обох dc (упередження) і ac компонентів (тому у виразах ми використали верхній регістр). Нас цікавить ac компоненти для малосигнальної моделі. Ми бачимо, що струм стоку залежить від двох напруг, від воріт до джерела і від джерела до джерела. Для додаткових значень ми можемо написати цей зв'язок як

(14)

У рівнянні (14), gm is передня провідність та r0 є вихідним опором. Їх значення знайдені, приймаючи часткові похідні в рівнянні (5). Таким чином,

(15)

Наближення в рівнянні (15) є результатом спостереження λ якщо маленький. Рівняння (14) призводить до малосигнальної моделі з малюнка 12.

Малюнок 12 - Малогабаритна модель MOSFET

СТРУМ - 2. Металоксидний напівпровідник FET (MOSFET)

СТРУМ - 2. Металоксидний напівпровідник FET (MOSFET) ПОПЕРЕДНЯ 1. Переваги та недоліки FET

ПОПЕРЕДНЯ 1. Переваги та недоліки FET