5. Інтегральні схеми MOSFET

Інтегральні схеми MOSFET

Коли транзистори MOSFET виготовляються як частина інтегральної схеми, практичні міркування вимагають двох основних змін у конфігураціях схеми. По-перше, великі конденсатори зв'язку та обходу, що використовуються в дискретних підсилювачах, практично не можуть бути виготовлені в інтегральних схемах через малі розміри. Ми долаємо цей недолік, виготовляючи підсилювачі з прямим зв'язком.

Друга велика зміна полягає в тому, що ми не можемо легко виготовити резистори, що використовуються як частина схеми зсуву. Замість цього ми використовуємо активні навантаження і джерела струму, що складаються з МОП-транзисторів.

Інтегровані схеми використовують як NMOS, так і схему PMOS. CMOS є більш поширеним в цифровій схемі, в той час як NMOS, як правило, використовується для ICs більш високої щільності (тобто, більше функцій на чіп).

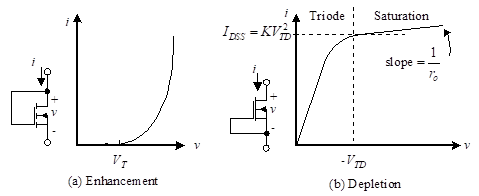

Моделювання активних навантажень використовує переваги нахилу характеристичних кривих МОП. На малюнку 23 показано два типи активних навантажень. На малюнку 23 (a) ми показуємо навантаження з підвищенням NMOS, тоді як 23 (b) показує виснаження NMOS. Також на малюнку показано відповідні характеристичні криві.

Малюнок 23 - Активні навантаження

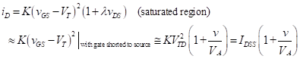

Для підсилюючого навантаження NMOS зв'язок між напругою і струмом задається

![]()

(29)

Еквівалентний опір цієї конфігурації 1 /gm, де значення проникності є тим, що застосовується в точці зміщення.

Навантаження виснаження NMOS має еквівалентний опір, який визначається нахилом характеристики, заданої наступним рівнянням

(30)

5.1 Зсув інтегральних схем MOSFET

Тепер, коли ми маємо дві методи для моделювання активних навантажень, ми можемо вирішити проблему зміщення. Ми використовуємо активне навантаження замість опору навантаження в будь-якій з конфігурацій схеми. Щоб показати техніку для їх аналізу, розглянемо підсилювач NMOS, використовуючи додаткове навантаження, як показано на малюнку 24.

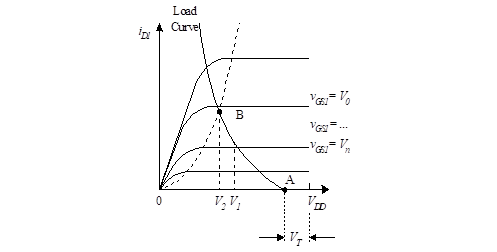

Транзистор позначений Q2 замінює RD наших попередніх схем. Щоб визначити робочу точку спокою, ми використовуємо ті самі методи, що й у розділі 4, «Конфігурації підсилювача FET та зміщення», лише замінюючи графічну характеристику навантаження посилення лінією навантаження резистора. Тобто нам потрібно знайти одночасне рішення характеристик транзистора FET з рівнянням для навантажувальної лінії. Ми можемо зробити це графічно, як показано на малюнку 25.

Параметричні криві є характеристичними кривими для підсилювального транзистора Q1. Напруга проти струму, що характеризує активне навантаження, Q2 є на малюнку 23. Вихідна напруга, vз, це різниця між VDD і напруга на активному навантаженні. Струм в активному навантаженні такий же, як і струм стоку в підсилює транзисторі. Тому ми конструюємо лінійку навантаження, взявши зміщений дзеркальний образ характеристики рисунка 23. Робочою точкою є перетин цієї кривої з відповідною кривою характеристик транзистора. Нам потрібно знайти напругу від воріт до джерела, щоб дізнатися, яку криву транзистора вибрати. Як ми побачимо далі, вхідна напруга зміщення часто замінюється активним джерелом струму.

Малюнок 25 - Графічне рішення для Q-точки

Тепер, коли ми знаємо, як імітувати активне навантаження, ми звертаємо нашу увагу на генерацію опорного струму, який буде використовуватися як частина схеми вхідного зміщення. Ці джерела струму використовуються так само, як ми використовували їх для зміщення підсилювача BJT.

Малюнок 26 - Поточне дзеркало

Ми аналізуємо MOSFET поточне дзеркало. Поточне дзеркало показано на малюнку 26. Два транзистори вважаються ідеально узгодженими. Вихідний струм - струм стоку Q2і еталонних поточних накопичувачів Q1. Якщо транзистори ідеально підібрані, вихідний струм буде точно дорівнювати опорному струму. Це вірно, оскільки транзистори з'єднані паралельно. Як і у випадку із дзеркалом струму BJT, опорний струм може генеруватися шляхом подання опорної напруги на опорний опір, як показано на малюнку 26 (b).

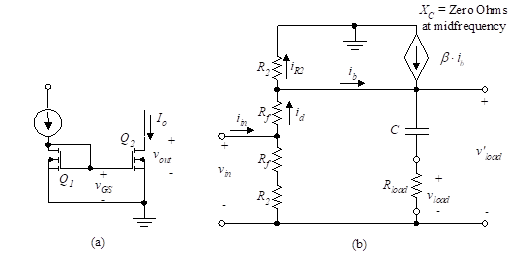

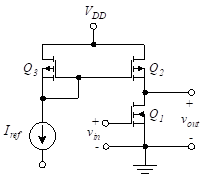

Введення різних підсхеми разом (тобто, активне навантаження і опорний струм) призводить до підсилення CMOS на рисунку 27.

Посилення цього підсилювача задається

![]()

(31)

Малюнок 27 - підсилювач CMOS

Ефект тіла 5.2

Наше обговорення розділу „2. Металооксидний напівпровідник FET (MOSFET) », що відноситься до підкладки (або тіла) MOSFET. Цей субстрат відіграє важливу роль у встановленні каналу. При роботі дискретних МОП-транзисторів тіло часто підключається до джерела живлення. У таких випадках основа не впливає безпосередньо на роботу пристрою, і застосовуються криві, розроблені раніше в цій главі.

Ситуація змінюється, коли MOSFETs виготовляються як частина інтегральних схем. У таких випадках підкладка кожного окремого транзистора не ізольована від інших підкладок. Дійсно, субстрат часто ділиться між усіма МОП-транзисторами на чіпі. У ICOS ICOS, загальний субстрат буде підключений до самого позитивного джерела терміналу, а в NMOS він підключений до землі (або до негативного харчування, якщо є). Це встановлює зворотне зміщення між джерелом і тілом кожного транзистора. Ефект цього зворотного ухилу полягає в зміні робочих характеристик. Наприклад, в n-канальний пристрій, він ефективно підвищує поріг (VT). Кількість, за якою змінюється поріг, залежить від фізичних параметрів і побудови пристрою. Для NMOS цю зміну можна апроксимувати

![]()

(32)

У Рівнянні (32), γ є параметром пристрою, який змінюється між 0.3 і 1 (V)-1/2). VSB є напругою від джерела до тіла, і є Потенціал Фермі. Це властивість матеріалу, і типовим значенням є 0.3 V для кремнію.

СТРУМ - 5. Інтегральні схеми MOSFET

СТРУМ - 5. Інтегральні схеми MOSFET ПОПЕРЕДНЯ 4. Конфігурації та зміщення підсилювача FET

ПОПЕРЕДНЯ 4. Конфігурації та зміщення підсилювача FET