KHAI THÁC. Mạch tích hợp MOSFE

Mạch tích hợp MOSFE

Khi các bóng bán dẫn MOSFET được chế tạo như một phần của mạch tích hợp, việc xem xét thực tế đòi hỏi hai thay đổi lớn trong cấu hình mạch. Đầu tiên, các tụ điện ghép và bỏ qua lớn được sử dụng trong các bộ khuếch đại rời rạc thực tế không thể được chế tạo trong các mạch tích hợp vì kích thước nhỏ. Chúng tôi khắc phục nhược điểm này bằng cách chế tạo các bộ khuếch đại ghép nối trực tiếp.

Thay đổi lớn thứ hai là chúng ta không thể dễ dàng chế tạo các điện trở được sử dụng như một phần của mạch sai lệch. Thay vào đó, chúng tôi sử dụng tải hoạt động và các nguồn hiện tại bao gồm các bóng bán dẫn MOS.

Mạch tích hợp sử dụng cả mạch NMOS và PMOS. CMOS phổ biến hơn trong mạch kỹ thuật số, trong khi NMOS thường được sử dụng cho các IC mật độ cao hơn (nghĩa là nhiều chức năng hơn trên mỗi chip).

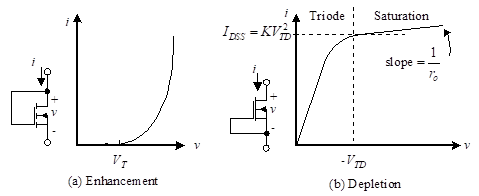

Mô phỏng tải hoạt động tận dụng độ dốc của các đường cong đặc trưng MOS. Hình 23 cho thấy hai loại tải hoạt động. Trong hình 23 (a), chúng tôi hiển thị tải tăng cường NMOS, trong khi 23 (b) hiển thị tải giảm NMOS. Cũng hiển thị trong hình là các đường cong đặc trưng có liên quan.

Hình 23 - Tải hoạt động

Đối với tải tăng cường NMOS, mối quan hệ giữa điện áp và dòng điện được đưa ra bởi

![]()

(29)

Điện trở tương đương của cấu hình này là 1 /gm, trong đó giá trị của độ dẫn là giá trị áp dụng tại điểm thiên vị.

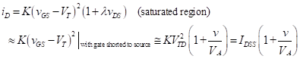

Tải trọng suy giảm NMOS có điện trở tương đương được xác định bởi độ dốc của đặc tính được cho bởi phương trình sau

(30)

Xu hướng 5.1 của mạch tích hợp MOSFET

Bây giờ chúng tôi có hai kỹ thuật để mô phỏng tải hoạt động, chúng tôi có thể giải quyết vấn đề sai lệch. Chúng tôi sử dụng tải hoạt động thay cho điện trở tải trong bất kỳ cấu hình mạch nào. Để hiển thị kỹ thuật phân tích những thứ này, chúng ta hãy xem xét bộ khuếch đại NMOS bằng cách sử dụng tải tăng cường, như trong Hình 24.

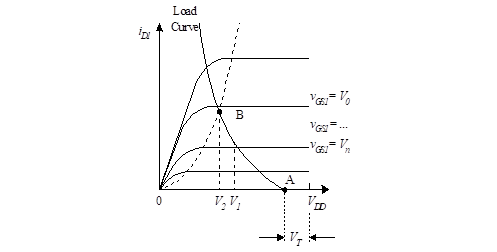

Các bóng bán dẫn có nhãn Q2 thay thế RD của mạch trước đó của chúng tôi. Để xác định điểm hoạt động tĩnh, chúng tôi sử dụng các kỹ thuật tương tự như chúng tôi đã làm trong Phần 4, “Cấu hình và xu hướng Bộ khuếch đại FET” chỉ thay thế đặc tính đồ họa tải nâng cao cho đường tải điện trở. Tức là chúng ta cần tìm nghiệm đồng thời của đặc tính transistor FET với phương trình đường tải. Chúng ta có thể thực hiện điều này bằng đồ thị như trong Hình 25.

Các đường cong tham số là các đường cong đặc trưng cho bóng bán dẫn khuếch đại, Q1. Điện áp so với đặc tính hiện tại của tải hoạt động, Q2 là những hình của 23. Điện áp đầu ra, vra, là sự khác biệt giữa VDD và điện áp trên tải hoạt động. Dòng điện trong tải hoạt động giống như dòng thoát trong bóng bán dẫn khuếch đại. Do đó, chúng tôi xây dựng đường tải bằng cách lấy hình ảnh phản chiếu đã dịch chuyển của đặc tính của Hình 23. Điểm hoạt động là giao điểm của đường cong này với đường cong đặc trưng của bóng bán dẫn thích hợp. Chúng ta cần tìm điện áp cổng tới nguồn để biết nên chọn đường cong bán dẫn nào. Như chúng ta sẽ thấy tiếp theo, điện áp phân cực đầu vào thường được thay thế bằng một nguồn hiện tại đang hoạt động.

Hình 25 - Giải pháp đồ họa cho điểm Q

Bây giờ chúng ta đã biết cách mô phỏng một tải hoạt động, chúng ta chuyển sự chú ý của mình sang việc tạo ra một dòng tham chiếu sẽ được sử dụng như một phần của mạch phân cực đầu vào. Các nguồn hiện tại này được sử dụng theo cách tương tự như chúng tôi đã sử dụng chúng cho xu hướng khuếch đại BJT.

Hình 26 - Gương hiện tại

Chúng tôi phân tích MOSFET nhân bản hiện tại. Một tấm gương hiện tại được hiển thị trong Hình 26. Hai bóng bán dẫn được giả định là hoàn toàn phù hợp. Dòng điện đầu ra là dòng thoát của Q2và một ổ đĩa hiện tại tham chiếu Q1. Nếu các bóng bán dẫn được kết hợp hoàn hảo, dòng điện đầu ra sẽ chính xác bằng dòng điện tham chiếu. Điều này đúng vì các bóng bán dẫn được kết nối song song. Cũng giống như trường hợp của gương dòng điện BJT, dòng điện chuẩn có thể được tạo ra bằng cách đặt một điện áp chuẩn qua điện trở chuẩn, như thể hiện trong Hình 26 (b).

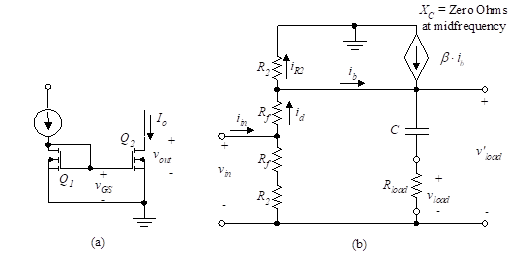

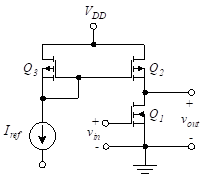

Đặt các mạng con khác nhau lại với nhau (nghĩa là tải hoạt động và dòng tham chiếu) dẫn đến bộ khuếch đại CMOS của Hình 27.

Độ lợi của bộ khuếch đại này được đưa ra bởi

![]()

(31)

Hình 27 - Bộ khuếch đại CMOS

Hiệu ứng cơ thể 5.2

Cuộc thảo luận của chúng tôi về Phần “2. FET bán dẫn oxit kim loại (MOSFET) ”được gọi là chất nền (hoặc phần thân) của MOSFET. Chất nền này đóng một vai trò quan trọng trong việc thiết lập kênh. Trong hoạt động của các MOSFET rời rạc, cơ thể thường được kết nối với nguồn điện. Trong những trường hợp như vậy, chất nền không ảnh hưởng trực tiếp đến hoạt động của thiết bị và các đường cong được phát triển trước đó trong chương này sẽ được áp dụng.

Tình hình thay đổi khi MOSFE được chế tạo như một phần của các mạch tích hợp. Trong những trường hợp như vậy, chất nền của mỗi bóng bán dẫn riêng lẻ không bị cô lập với các chất nền khác. Thật vậy, một chất nền thường được chia sẻ giữa tất cả các MOSFET trên chip. Trong IC PMOS, chất nền dùng chung sẽ được kết nối với thiết bị đầu cuối nguồn tích cực nhất, trong khi ở NMOS, nó được kết nối với mặt đất (hoặc với nguồn cung cấp âm nếu có). Điều này thiết lập một sự thiên vị ngược giữa nguồn và thân của mỗi bóng bán dẫn. Tác động của sai lệch ngược này là thay đổi các đặc tính vận hành. Ví dụ: trong một nthiết bị kênh, nó có hiệu quả tăng ngưỡng (VT). Số lượng thay đổi ngưỡng phụ thuộc vào thông số vật lý và cấu trúc thiết bị. Đối với NMOS, thay đổi này có thể được xấp xỉ bởi

![]()

(32)

Trong phương trình (32), là một tham số thiết bị khác nhau giữa khoảng 0.3 và 1 (V-1/2). VSB là điện áp từ nguồn đến thân và là Tiềm năng Fermi. Đây là một tính chất của vật liệu và giá trị tiêu biểu là 0.3 V cho silicon.

HIỆN TẠI - 5. Mạch tích hợp MOSFET

HIỆN TẠI - 5. Mạch tích hợp MOSFET TRƯỚC-4. Cấu hình và xu hướng khuếch đại FET

TRƯỚC-4. Cấu hình và xu hướng khuếch đại FET