KHAI THÁC. Bộ khuếch đại vi sai

Bộ khuếch đại vi sai

Hầu hết các bộ khuếch đại hoạt động bao gồm một loạt các bóng bán dẫn, điện trở và tụ điện tạo thành một hệ thống hoàn chỉnh trên một chip đơn. Các bộ khuếch đại có sẵn ngày nay là đáng tin cậy, kích thước nhỏ và tiêu thụ rất ít năng lượng.

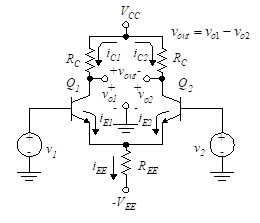

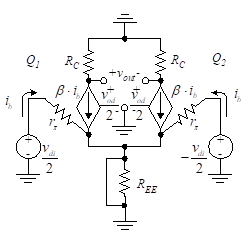

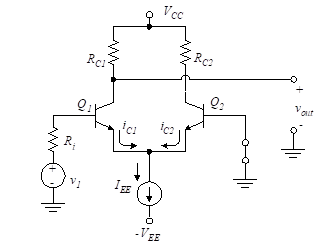

Giai đoạn đầu vào của hầu hết các op-amps là Dkhuếch đại hiệu quả như thể hiện ở dạng đơn giản nhất của nó trong Hình 1.

Hình 1 - Bộ khuếch đại vi sai

Bộ khuếch đại vi sai bao gồm hai bộ phát chung kết hợp bộ phát dc bộ khuếch đại. Nó có hai đầu vào, v1 và v2và ba đầu ra, vo1, vo2 và vra. Đầu ra thứ ba, vra, là sự khác biệt giữa vo1 và vo2.

Đặc điểm chuyển giao dcUMX

Bộ khuếch đại vi sai không hoạt động tuyến tính với đầu vào tín hiệu lớn. Để đơn giản hóa việc phân tích, chúng tôi giả định rằng RE là lớn, điện trở cơ sở của mỗi bóng bán dẫn là không đáng kể và điện trở đầu ra của mỗi bóng bán dẫn là lớn. Lưu ý rằng chúng tôi sử dụng REE thay vì RE trong bộ khuếch đại vi sai vì điện trở được sử dụng ở đây lớn và có thể là điện trở tương đương của nguồn hiện tại. Giá trị lớn của REE giữ cho điện áp bộ phát giảm gần như không đổi.

Bây giờ chúng ta giải quyết mạch này cho điện áp đầu ra. Chúng ta bắt đầu bằng cách viết một phương trình KVL xung quanh vòng lặp cơ sở cho mạch của Hình 1.

(1)

(2)

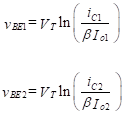

Chúng ta cần tìm biểu thức cho các dòng collector, iC1 và iC2. Các điện áp phát cơ sở được đưa ra bởi phương trình,

Trong phương trình (2) Io1 và Io2 là các dòng bão hòa ngược cho Q1 và Q2 tương ứng. Các bóng bán dẫn được giả định là giống hệt nhau. Kết hợp các phương trình (1) và (2)

(3)

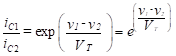

Giải phương trình (3) cho tỷ lệ hiện tại, chúng tôi thấy,

(4)

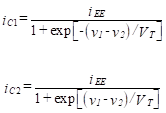

Chúng ta có thể giả định iC1 xấp xỉ bằng iE1 và iC2 xấp xỉ bằng iE2. vì thế

(5)

Kết hợp các phương trình (4) và (5), chúng ta có

(6)

Lưu ý rằng

(7)

Một quan sát quan trọng có thể được thực hiện bằng cách xem Công thức (6). Nếu v1 – v2 trở nên lớn hơn vài trăm millivolt, dòng collector trong bóng bán dẫn 2 trở nên nhỏ và bóng bán dẫn về cơ bản bị cắt. Dòng thu trong bóng bán dẫn 1 xấp xỉ bằng iEEvà bóng bán dẫn này đã bão hòa. Các dòng collector, và do đó điện áp đầu ra vra, trở nên độc lập với sự khác biệt giữa hai điện áp đầu vào.

Khuếch đại tuyến tính chỉ xảy ra đối với chênh lệch điện áp đầu vào nhỏ hơn khoảng 100 mV. Để tăng phạm vi tuyến tính của điện áp đầu vào, có thể thêm các điện trở bộ phát nhỏ.

1.2 Chế độ chung và chế độ vi sai

Bộ khuếch đại vi sai chỉ nhằm đáp ứng sự khác biệt giữa hai điện áp đầu vào, v1 và v2. Tuy nhiên, trong một op-amp thực tế, đầu ra phụ thuộc vào một mức độ nào đó trên tổng của các đầu vào này. Ví dụ, nếu cả hai đầu vào đều bằng nhau, điện áp đầu ra lý tưởng là bằng 0, nhưng trong một bộ khuếch đại thực tế thì không. Chúng tôi dán nhãn trường hợp khi mạch phản ứng với sự khác biệt là chế độ vi sai. Nếu hai đầu vào được làm bằng nhau, chúng ta nói mạch nằm trong chế độ thông thường. Lý tưởng nhất là chúng ta mong đợi mạch chỉ tạo ra một đầu ra ở chế độ vi sai.

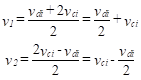

Bất kỳ hai điện áp đầu vào, v1 và v2, có thể được giải quyết thành một phần chung và một phần khác biệt. Chúng tôi xác định hai điện áp đầu vào mới như sau:

(8)

Điện áp, vdi, là điện áp đầu vào chế độ vi sai và nó chỉ đơn giản là sự khác biệt giữa hai điện áp đầu vào. Điện áp, vci, là điện áp đầu vào chế độ chung, và nó là trung bình của hai điện áp đầu vào. Các điện áp đầu vào ban đầu có thể được biểu thị theo các đại lượng mới này như sau:

(9)

Nếu chúng ta đặt hai điện áp đầu vào bằng nhau, chúng ta có

(10)

Vì hai đầu vào bằng nhau, nên điện áp tiếp giáp cơ sở phát ra bằng nhau (nếu các bóng bán dẫn giống hệt nhau). Do đó, các dòng thu cũng phải giống hệt nhau.

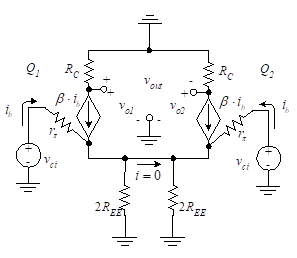

Hình 2 (a) Mạch tương đương bộ khuếch đại chế độ vi sai

Bây giờ chúng ta xem mạch tương đương cho điện áp đầu vào chế độ vi sai như trong hình 2 (a). Lưu ý rằng như hiện tại trong Q1 mạch tăng, dòng điện trong Q2 mạch giảm cùng tốc độ và biên độ. Điều này đúng vì đầu vào Q2 bằng với Q1 nhưng 180o ngoài giai đoạn. Do đó, điện áp thay đổi trên REE bằng không. Kể từ khi ac điện áp tín hiệu trên REE bằng không, nó có thể được thay thế bằng một mạch ngắn trong ac mạch tương đương. Lưu ý rằng việc đặt điện áp ở mỗi đế bán dẫn có biên độ bằng nhau nhưng 180o lệch pha tương đương với việc đặt một điện áp giữa hai cơ sở bóng bán dẫn có biên độ gấp đôi. Các điện áp tại vo1 và vo2 có biên độ bằng nhau nhưng ngược pha và khuếch đại chế độ vi sai là

(11)

Độ lợi chế độ vi sai này được xác định tại đầu ra đơn kể từ khi nó được thực hiện giữa một người thu gom và mặt đất. Nếu đầu ra được lấy giữa vo1 và vo2, mức tăng chế độ vi sai được gọi là đầu ra hai đầu và được đưa ra bởi

(12)

Một phân tích tương tự có thể được áp dụng cho mạch tương đương chế độ chung trong Hình 2 (b).

Hình 2 (b) Mạch tương đương bộ khuếch đại chế độ chung

Nếu chúng ta chia điện trở REE thành hai điện trở song song mỗi điện trở có điện trở ban đầu gấp đôi, chúng ta có thể tìm ra đầu ra bằng cách chỉ phân tích một nửa mạch. Do các bóng bán dẫn giống hệt nhau và các điện áp đầu vào chế độ chung là bằng nhau và cùng pha, nên các điện áp trên 2REE điện trở là như nhau. Do đó, dòng điện giữa hai điện trở song song hiển thị là 0 và chúng ta chỉ cần nhìn vào một phía của mạch. Mức tăng điện áp ở chế độ chung là sau đó

(13)

Giả sử phương trình (13) REE lớn và re<<REE.

Chúng tôi tìm thấy điện áp đầu ra hai đầu theo mức tăng của chế độ chung và chế độ vi sai như sau:

(14)

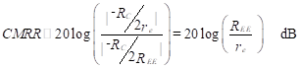

Điều mong muốn là mức tăng của chế độ vi sai lớn hơn nhiều so với mức tăng ở chế độ chung để bộ khuếch đại phản ứng chủ yếu với sự khác biệt giữa các điện áp đầu vào. Các tỷ lệ loại bỏ chế độ chung, CMRR, được định nghĩa là tỷ lệ của mức tăng chế độ vi sai với mức tăng chế độ chung. Nó thường được biểu thị bằng dB.

(15)

Bây giờ chúng tôi xác định điện trở đầu vào của bộ khuếch đại ở cả chế độ vi sai và chế độ chung. Đối với chế độ vi sai, chúng tôi xem xét bộ khuếch đại ở đế của cả hai bóng bán dẫn. Điều này dẫn đến một mạch hoàn chỉnh thông qua bộ phát của cả hai bóng bán dẫn và điện trở đầu vào là

(16)

Bây giờ đối với đầu vào chế độ chung, chúng tôi xem xét bộ khuếch đại trong Hình 2 (b). Do đó, điện trở đầu vào là

(17)

Những kết quả này cho thấy điện trở đầu vào của chế độ chung cao hơn nhiều so với chế độ vi sai.

Phân tích bộ khuếch đại vi sai của chúng tôi dựa trên các BJT như các khối xây dựng bóng bán dẫn. FET cũng có thể được sử dụng trong các bộ khuếch đại vi sai với lợi thế dẫn đến giảm dòng điện phân cực đầu vào và trở kháng đầu vào gần như vô hạn. Việc phân tích bộ khuếch đại vi sai bằng FET được thực hiện theo cách tương tự như phân tích BJT.

Bộ khuếch đại vi sai cần các bóng bán dẫn phù hợp để đảm bảo rằng mạch hoạt động chính xác. Nếu bộ khuếch đại vi sai nằm trên một mạch tích hợp, yêu cầu bổ sung này sẽ ít gặp vấn đề hơn vì hai bóng bán dẫn được chế tạo cùng một lúc bằng cùng một vật liệu.

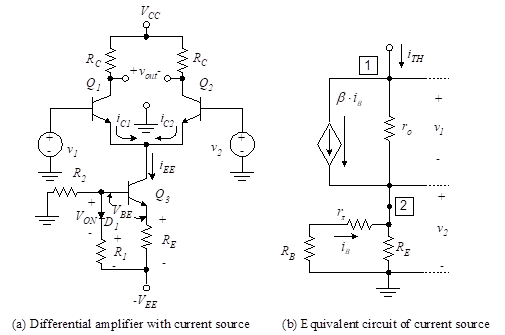

Bộ khuếch đại vi sai 1.3 với nguồn hiện tại không đổi

Đó là mong muốn để thực hiện REE càng lớn càng tốt để giảm đầu ra chế độ chung. Phương trình cho thấy rằng để làm cho CMRR lớn, chúng ta phải thực hiện REE lớn. Vì các điện trở lớn khó chế tạo trên chip IC, chúng tôi tìm cách tiếp cận thay thế. Điều này được thực hiện bằng cách thay thế REE với một dc nguồn hiện tại. Một nguồn hiện tại lý tưởng có trở kháng vô hạn, vì vậy chúng tôi điều tra khả năng thay thế REE với một nguồn hiện tại như vậy. Hình 9.3 minh họa một bộ khuếch đại vi sai trong đó điện trở, REE, được thay thế bằng một nguồn hiện tại không đổi.

(18)

Nguồn càng gần với nguồn dòng không đổi lý tưởng, tỷ lệ loại bỏ chế độ chung càng cao. Chúng tôi minh họa một nguồn hiện tại thiên vị cố định bù diode. Việc bù làm cho hoạt động của mạch ít phụ thuộc vào sự thay đổi nhiệt độ. Điốt D1 và bóng bán dẫn Q3 được chọn sao cho chúng có các đặc điểm gần như giống hệt nhau trong phạm vi nhiệt độ hoạt động.

Để phân tích mạch của Hình 3 (a) và tìm CMRR, chúng ta cần xác định điện trở tương đương, RTH (tương đương Thevenin của mạch nguồn hiện tại không đổi). Điện trở tương đương được đưa ra bởi [xem Hình 3 (b)]

Viết phương trình KCL tại nút 1, chúng ta có

(19)

Ở đâu ro là điện trở trong của bóng bán dẫn tại điểm vận hành được chỉ định. Nó được đưa ra bởi

(20)

Hình 3 - Bộ khuếch đại vi sai với nguồn dòng không đổi

Một phương trình KCL tại nút 2 mang lại

(21)

Ở đâu

(22)

Thay thế v1 và v2 vào phương trình tại nút 2, chúng ta có

(23)

Cuối cùng, lực cản Thevenin được đưa ra bằng cách thay thế các phương trình (22) và (23) thành phương trình (18).

(24)

Bây giờ chúng ta sẽ thực hiện một loạt các giả định để đơn giản hóa rất nhiều biểu thức này. Để duy trì sự ổn định thiên vị, chúng tôi sử dụng hướng dẫn rằng

(25)

Thay thế giá trị này của RB trong phương trình (24) và chia cho β, chúng ta có

(26)

Chúng ta có thể đơn giản hóa biểu thức này bằng cách lưu ý

(27)

Chúng ta sau đó có

(28)

Vì thuật ngữ thứ hai trong phương trình này lớn hơn nhiều so với thuật ngữ thứ nhất, vì vậy chúng ta có thể bỏ qua RE để có được

(29)

Phương trình này có thể được đơn giản hóa hơn nữa nếu tồn tại điều kiện sau:

(30)

Trong trường hợp đó, chúng tôi có kết quả đơn giản

(31)

Do đó, nếu tất cả các xấp xỉ là hợp lệ, RTH độc lập với β và giá trị của nó là khá lớn.

Bộ khuếch đại vi sai 1.4 với đầu vào và đầu ra một đầu

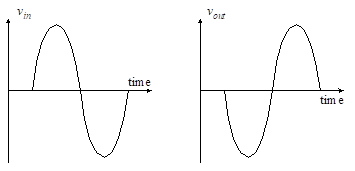

Hình 4 cho thấy một bộ khuếch đại vi sai trong đó đầu vào thứ hai, v2, được đặt bằng 0 và đầu ra được lấy là vo1.

Chúng tôi sử dụng một nguồn hiện tại không đổi thay cho REE, như đã thảo luận trong phần trước. Điều này được gọi là một bộ khuếch đại đầu vào và đầu ra một đầu có đảo pha. Bộ khuếch đại được phân tích bằng cách cài đặt v2 = 0 trong các phương trình trước đó. Đầu vào vi sai đơn giản là

(32)

vì vậy đầu ra là

(33)

Hình 4 - Đầu vào một đầu có đảo pha

Dấu trừ cho thấy bộ khuếch đại này thể hiện một 180o chuyển pha giữa đầu ra và đầu vào. Một đầu vào và đầu ra hình sin điển hình được minh họa trong Hình 5.

Hình 5 - Đầu vào và đầu ra hình sin

Nếu tín hiệu đầu ra được tham chiếu đến mặt đất nhưng không muốn đảo ngược pha, đầu ra có thể được lấy từ bóng bán dẫn Q2.

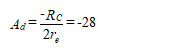

Ví dụ 1 - Bộ khuếch đại vi sai (Phân tích)

Tìm mức tăng điện áp vi sai, mức tăng điện áp ở chế độ chung và CMRR cho mạch được hiển thị trong Hình 1. Giả sử Ri = 0, RC = 5 kÎ ©, VEE = 15 V, VBE = 0.7 V, VT = 26 mV và REE = 25 kÎ ©. Để cho v2 = 0 và lấy đầu ra từ vo2.

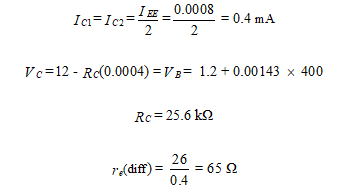

Giải pháp: Hiện tại thông qua REE được tìm thấy ở điều kiện không hoạt động. Kể từ khi cơ sở của Q2 được nối đất, điện áp phát là VBE = 0.7 V và

Dòng tĩnh trong mỗi bóng bán dẫn là một nửa số tiền này.

từ

mức tăng điện áp vi sai trong mỗi bóng bán dẫn là

Độ tăng điện áp ở chế độ chung là

Tỷ lệ loại bỏ chế độ chung sau đó được đưa ra bởi

ỨNG DỤNG

Ngoài ra, bạn có thể thực hiện các tính toán này với trình mô phỏng mạch TINA hoặc TINACloud, sử dụng công cụ Phiên dịch của họ bằng cách nhấp vào liên kết bên dưới.

1- Mô phỏng mạch khuếch đại vi sai

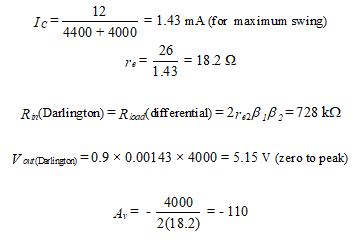

Ví dụ 2

Đối với bộ khuếch đại vi sai được mô tả trong Ví dụ 1, hãy thiết kế nguồn dòng phân cực cố định được bù nhiệt độ (Hình 3) để thay thế REE và xác định CMRR mới cho bộ khuếch đại vi sai, với ro = 105 kÎ ©, VBE = 0.7 V và β = 100. Giả định R1 = R2.

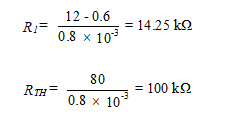

Giải pháp: Chúng tôi đặt điểm hoạt động của bóng bán dẫn ở giữa dc vạch tải trọng.

Sau đó, tham khảo nguồn hiện tại của Hình 3 (a),

Để ổn định thiên vị,

Sau đó

Kể từ khi 0.1RE>>re (tức là, 1.25 kΩ >> 26 / 0.57 Ω), thì từ Công thức (31) chúng ta có

CMRR được đưa ra bởi

ỨNG DỤNG

Ngoài ra, bạn có thể thực hiện các tính toán này với trình mô phỏng mạch TINA hoặc TINACloud, sử dụng công cụ Phiên dịch của họ bằng cách nhấp vào liên kết bên dưới.

2- Mô phỏng mạch khuếch đại vi sai

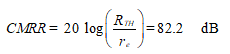

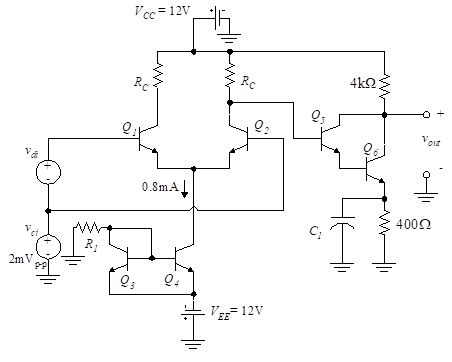

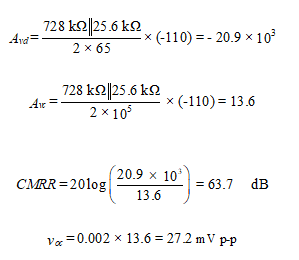

Ví dụ 3

Thiết kế mạch để đạt được các điều kiện như được chỉ định trong Hình 6 để xoay điện áp đầu ra tối đa. Năm bóng bán dẫn, Q1 đến Q5, mỗi cái có β = 100 trong khi Q6 có một β của 200. VBE là 0.6 V cho tất cả các bóng bán dẫn, VT = 26 mV và VA = 80 V. Giả sử tất cả các bóng bán dẫn là giống hệt nhau.

Mục đích,

(A) RC, R1và CMRR.

(b) Điện áp đầu ra chế độ chung.

(c) Điện áp đầu ra chế độ vi sai.

(d) Chế độ vi sai đầu vào Vôn vdi cho đầu ra tối đa.

Giải pháp: Chúng ta sẽ xử lý mạch trong ba phần:

- KHAI THÁC. Bộ khuếch đại Darlington.

- KHAI THÁC. Bộ khuếch đại vi sai

- KHAI THÁC. Nguồn hiện tại đơn giản

Bây giờ cho toàn bộ hệ thống, chúng tôi có

Đầu vào vi sai vdi cần thiết để tạo ra điện áp đầu ra không bị biến dạng tối đa là

Ngoài ra, bạn có thể thực hiện các tính toán này với trình mô phỏng mạch TINA hoặc TINACloud, sử dụng công cụ Phiên dịch của họ bằng cách nhấp vào liên kết bên dưới.

3- Mô phỏng mạch khuếch đại vi sai

HIỆN TẠI - 1. Bộ khuếch đại vi sai

HIỆN TẠI - 1. Bộ khuếch đại vi sai PREVIOUS- Bộ khuếch đại hoạt động thực tế- Giới thiệu

PREVIOUS- Bộ khuếch đại hoạt động thực tế- Giới thiệu