9. FET Gücləndiricinin təhlili

FET Gücləndiricinin təhlili

9.1 CS (və Resurs Resistor) Amplifikatçısı

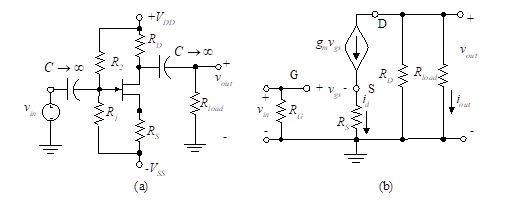

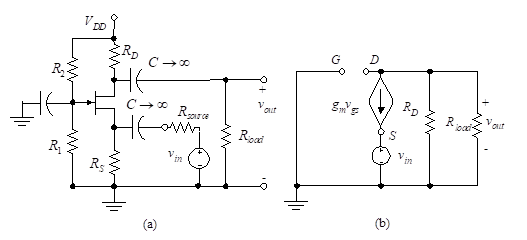

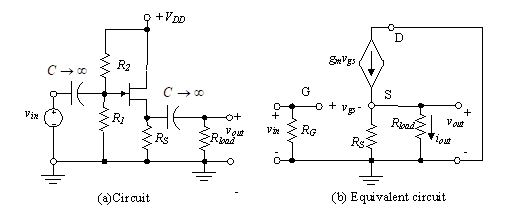

Şəkil 33 - Mənbə rezistorlu CS gücləndiricisi

Şəkil 33 (a) qaynar rezistorlu CS yükselticisini göstərir. Məqalələr ac ekvivalent circuit Şəkil 33 (b) -dədir. Güman edirik ro müqayisədə böyükdür, buna görə də laqeyd oluna bilər. Bir kondansatörün mənbə və torpaq arasında olması (yəni CS yükseltici) varsa, biz sadəcə müəyyənləşdirməliyik RS aşağıdakılarda sıfıra bərabərdir ac tənliklər. Bunu bu törəmənin nəticəsi olaraq edirik.

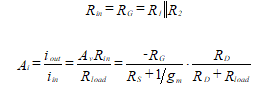

Şəkil 33-in (b) hissəsində, RG paralel birləşməsidir R1 və R2 və VGG bias dövrünün Thevenin ekvivalent gərginliyidir:

(41)

(41)

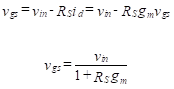

Təhlil etmək üçün ac ekvivalent circuit, qapı circuit ətrafında KVL tənliyi yazırıq.

(42)

(42)

Çıxış gərginliyi, vhəyatatərəfindən verilir

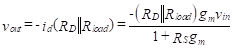

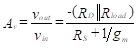

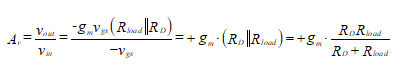

Gərginlik artımı, Avindi tapılmışdır.

(43)

(43)

Mənbənin müqaviməti, RS, bir kondansatör bypassed, biz imkan RS = 0 və geriləmə artımı artır

![]() (44)

(44)

Bu, adətən böyük bir mənfi nömrədir.

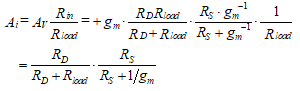

Giriş müqaviməti və cari mənfəət verilir

(45)

(45)

9.2 The CG Amplifier

Şəkil 37 (a) bir mərhələli ümumi qapalı gücləndiriciyi və Şəkil 6.37 (b) ac bərabərdir. Biz bir daha laqeyd qaldıq ro paralel kombinasiyaya nisbətən böyük olduğunu ehtimal edir RD ilə Ryükləmək.

Şəkil 37 - CG gücləndiricisi

Şəkil 37-dən (b) ən aşağı loopdan qapaqdan qaynaq gərginliyi tərəfindən verilir

![]() (46)

(46)

Bu günə qədər RS is

(47)

(47)

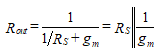

belə ki, mənbədən görülən (giriş) müqavimət

![]() (48)

(48)

Bu CS yükselticisi üçün Equation (45) ilə müqayisə edilməlidir. Görürük ki, qapı müqavimətinin yüksək olduğu halda, ümumi mənbəli gücləndiricinin giriş direnişi ümumi qapalı gücləndiricidən daha çox ola bilər. Əslində, CG gücləndiricisinin tətbiq sayıları aşağı giriş empedansı ilə bağlıdır.

Gərginlik mənfəəti ilə verilir

(49)

(49)

Denklem (44) ilə müqayisə edərək, mənbəyli dövrədə qeyri-sıxma müqavimət göstərən CS yükseltici üçün gərginliyin artımı CG gücləndiricisindən başqa CG gücləndiricisindən fərqlənir, fazı keçirmir.

Çıxış müqaviməti sadəcə verilir RD (bir test cərəyanı qoyun və qəbulu zamanı gərginliyi ölçün vin sıfır).

CG gücləndiricisinin cari gəliridir

(50)

(50)

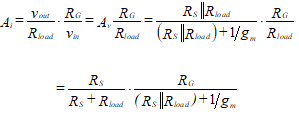

9.3 CD (SF) gücləndiricisi

Şəkil 39 (a) bir mərhələli ümumi yayma qaynaqlı izləyicisi (SF) gücləndiricisini və Şəkil 39 (b) ac bərabərdir. Analiz etdiyimiz hər bir konfiqurasiya ilə olduğu kimi, biz böyük müqaviməti, ro fərziyyə altında paralel birləşmədən çox daha böyükdür RS ilə Ryükləmək.

Şəkil 39 - CD gücləndiricisi

Giriş müqavimət sadəcə Rin = RG. Qapıdan qaynaqlı döngə ətrafında bir KVL tənliyi yazırıq

![]() (51)

(51)

əldə etdiklərimizdən

![]() (52)

(52)

Çıxış gərginliyi

![]() (53)

(53)

Gərginliyin artması çıxış gərginliyinə nisbətidır.

![]() (54)

(54)

Qeyd edək ki, bu gərginlik mənfəəti birləşmədən azdır və paralel birləşmə kimi birinə yaxınlaşır RS ilə Ryükləmək artırır.

İndi cari gəlir qazanırıq. Çıxış axını çıxış gərginliyinin yük müqavimətinə nisbəti. Giriş akımı giriş voltajı bölünür RG. Buna görə qazanc verilir

(55)

(55)

Çıxış müqavimətinə qarşı yük müqavimətçisinin bir test geriliyi ilə əvəzlənməsi mümkündür, vsınaqvə sonra ortaya çıxan cari tapmaq, isınaq. Bu test mənbəyi tərəfindən idarə olunan cari mənbədə bir node tənlikindən tapılır.

![]() (56)

(56)

Qapalı qaydanın gərginliyi sadədir -vsınaq çünki giriş gərginliyi sıfırdır. Buna görə çıxış direncidir

(57)

(57)

Cari - 9. FET Gücləndirici analizi

Cari - 9. FET Gücləndirici analizi Əvvəlki - 8. FET Gücləndiricilər - Kanonik konfiqurasiyalar

Əvvəlki - 8. FET Gücləndiricilər - Kanonik konfiqurasiyalar