2. Metallioksidipuolijohde FET (MOSFET)

Metallioksidipuolijohde FET (MOSFET)

Metallioksidipuolijohteinen FET (MOSFET) on neljän päätelaitteen. Terminaalit ovat lähde (S), portti (G) ja valua (D). substraatti or elin muodostaa neljännen terminaalin. MOSFET on rakennettu siten, että porttipäätelaite on eristetty kanavasta piidioksidielektrisellä. MOSFETit voivat olla joko ehtyminen or parannustila. Määrittelemme nämä kaksi termiä pian.

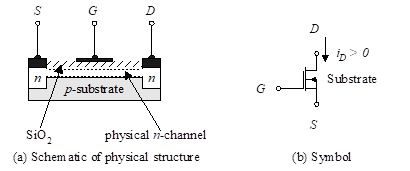

Kuva 1 - n-kanavan tyhjennys MOSFET

MOSFETeja kutsutaan joskus nimellä IGFET (eristetyt portti-kenttävaikutransistorit), jotka johtuvat SiO: sta2 kerros, jota käytetään eristeenä portin ja alustan välillä. Analyysi aloitetaan tyhjennystilassa MOSFET. Aivan kuten BJT: t voivat olla npn or pNPMOSFETit voivat olla joko n-kanava (NMOS) tai p-kanava (PMOS). Kuva 1 kuvaa fyysistä rakennetta ja symbolia n-kanavan poistaminen MOSFET. Huomaa, että substraatti on kytketty lähdepäätelaitteeseen. Näin on lähes aina.

MOSFET-tyhjennys on rakennettu a fyysinen kanavan, joka on sijoitettu viemärin ja lähteen väliin. Tämän seurauksena, kun jännite, vDS, käytetään viemärin ja lähteen, virran, iD, on olemassa tyhjennyksen ja lähteen välillä, vaikka portin pääte G ei ole yhteydessä toisiinsa (vGS = 0 V).

Rakentaminen n-kanavan poistaminen MOSFET alkaa p-dopattu pii. n-doped-lähde ja tyhjennyskaivot muodostavat matalan resistanssin väliset liitokset n-kanava, kuten kuvassa 1. Ohut kerros piidioksidia kerrostetaan, joka kattaa alueen lähteen ja viemärin välillä. SiO2 on eriste. Alumiinikerros kerrostetaan piidioksidi- eristimeen, jolloin muodostuu porttiliitin. Käytössä negatiivinen vGS työntää elektronit pois kanavan alueelta, jolloin kanava tyhjenee. Kun vGS saavuttaa tietyn jännitteen, VT, kanava on puristettu. Positiiviset arvot vGS lisää kanavan kokoa, mikä lisää viemärivirtaa. MOSFETin tyhjennys voi toimia joko positiivisilla tai negatiivisilla arvoilla vGS. Koska portti on eristetty kanavasta, porttivirta on vähäisen pieni (10: n järjestyksessä)-12 ).

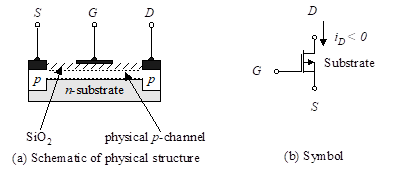

Kuva 2 - p-kanavan tyhjennys MOSFET

Kuva 2 on verrattavissa kuvaan 1, paitsi että olemme muuttaneet n-kanavan tyhjeneminen MOSFET a p-kanavan poistaminen MOSFET.

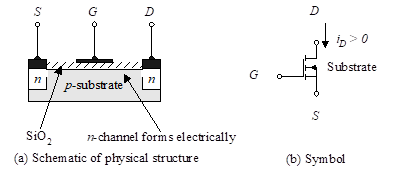

- n-kanavan lisäys MOSFET on esitetty kuvassa 3 yhdessä piirisymbolin kanssa. Tämä on yleisimmin käytetty kenttätransistorin muoto.

Kuva 3 - n-kanavan lisälaite MOSFET

- n-kanavan lisäys MOSFET poikkeaa MOSFET-tyhjennyksestä, koska siinä ei ole ohutta n-kerros. Se vaatii positiivisen jännitteen portin ja lähteen välille kanavan muodostamiseksi. Tämä kanava muodostuu positiivisen portin ja lähdön jännitteen vaikutuksesta, vGS, joka houkuttelee elektroneja substraattialueelta n-doped viemäri ja lähde. positiivinen vGS aiheuttaa elektronien kerääntymisen oksidikerroksen alapuolelle. Kun jännite saavuttaa kynnyksen, VTtähän alueeseen houkuttelee riittävästi elektroneja, jotta se toimisi johtavana n-kanavan. Ei merkittävää viemärivirtaa, iD on olemassa vGS ylittää VT.

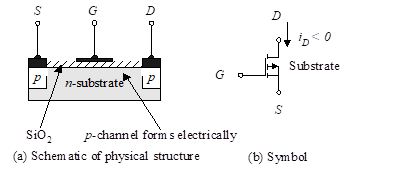

Kuva 4 on verrattavissa kuvaan 3, paitsi että olemme muuttaneet n-kanava-lisälaite MOSFET a p-kanavan lisälaite MOSFET.

Kuva 4 - p-kanavan lisälaite MOSFET

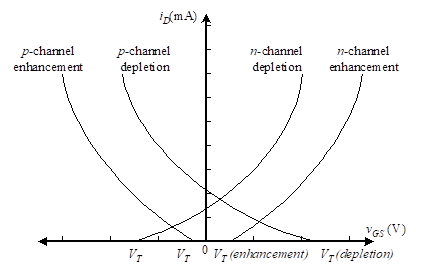

Yhteenvetona MOSFET-perhe näyttää tunnistuksen iD vastaan vGS kuviot 5. Jokainen ominaisuuskäyrä kehitetään riittävän tyhjennyslähteen jännitteellä vDS pitää laite normaalissa käyttöalueella iD vastaan vDS käyriä. Myöhemmissä osissa käytävä keskustelu määrittää kynnysjännitteen VT sekä MOSFET-laitteille että MOSFET-laitteille.

Kuva 5 - iD vastaan vGS MOSFET-perheen ominaisuudet riittävän tyhjennyslähteen jännitteelle VDS

2.1-parannustilan MOSFET-liitäntäominaisuudet

Nyt kun olemme esittäneet MOSFETin perusrakenteen ja toiminnan perustan, käytämme lähestymistapaa parannustilan laitteen päätelaitteiden käyttäytymisen tutkimiseen. Tehdään ensin joitain yleisiä havaintoja kuvasta 1. Ajattele MOSFETin normaalin virran kulkua viemäristä lähteeseen (aivan kuten BJT: ssä, se on kerääjän ja emitterin välillä). Kuten npn BJT: llä on olemassa kaksi takapalvelusta diodia viemärin ja lähteen välillä. Siksi meidän on käytettävä porttiin ulkoisia jännitteitä, jotta virta voi virrata viemärin ja lähteen välillä.

Jos maadoitamme lähteen ja käytämme positiivista jännitettä porttiin, jännite on tehokkaasti portin ja lähdön jännite. Positiivinen porttijännite houkuttelee elektroneja ja torjuu reiät. Kun jännite ylittää kynnyksen (VT), tarpeeksi elektroneja houkutellaan muodostamaan johtava kanava viemärin ja lähteen välillä. Tässä vaiheessa transistori kytkeytyy päälle ja virta on molempien funktio vGS ja vDS. On selvää VT on positiivinen luku n-kanavalaite ja negatiivinen luku a p-kanavalaite.

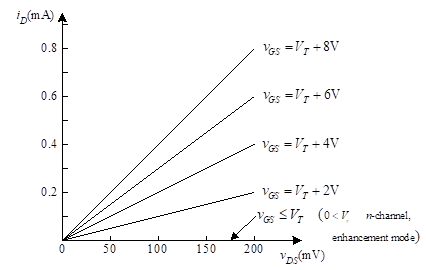

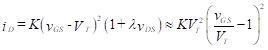

Kun kanava on luotu (eli vGS >VT), virtaus voi tapahtua kyseisessä kanavassa viemärin ja lähteen välillä. Tämä virtaus riippuu vDS, mutta se riippuu myös vGS. Kun vGS vain tuskin ylittää kynnysjännitteen, hyvin pieni virta voi virrata. Kuten vGS ylittää kynnyksen, kanava sisältää enemmän kantajia ja suuremmat virrat ovat mahdollisia. Kuva 6 näyttää välisen suhteen iD ja vDS jossa vGS on parametri. Huomaa, että vGS pienempi kuin kynnysarvo, ei virtaa. Korkeampi vGS, suhde välillä iD ja vDS on suunnilleen lineaarinen, mikä osoittaa, että MOSFET käyttäytyy kuin vastus, jonka resistanssi riippuu vGS.

Kuva 6 -iD vastaan vDS parannustilassa n-kanava MOSFET milloin vDS on pieni

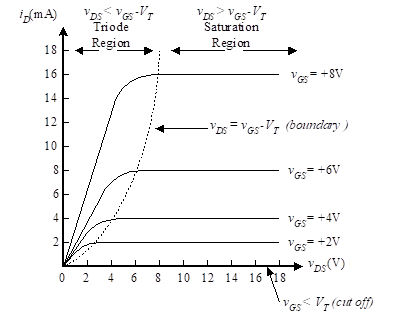

Kuvion 6 käyrät näyttävät suorilta viivoilta. Ne eivät kuitenkaan jatku suorina viivoina, kun vDS tulee suuremmaksi. Muista, että johtokanavan luomiseksi käytetään positiivista porttijännitettä. Se tekee tämän houkuttelemalla elektroneja. Positiivinen tyhjennysjännite tekee saman. Kun lähestymme kanavan tyhjennyspäätä, kanavan lähestyessä oleva jännite vGS-vDS koska molemmat lähteet vastustavat toisiaan. Kun tämä ero on pienempi kuin VT, kanava ei ole enää koko lähteen ja tyhjennyksen välissä. Kanava on rajoittavat viemäripäässä ja kasvaa edelleen vDS eivät aiheuta lisäystä iD. Tätä kutsutaan normaaliksi toiminta-alueeksi tai kyllästyminen kuvassa 7 esitetty alue ominaispiirteiden horisontaalisella osuudella. Kun ero on suurempi kuin VT, me kutsumme tätä transistori tilassa, koska potentiaalit kaikilla kolmella päätelaitteella vaikuttavat voimakkaasti virtaan.

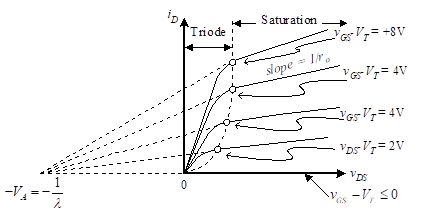

Aiempi keskustelu johtaa kuvion 7 toimintakäyriin.

Kuva 7 -iD vastaan vGS parannustilassa MOSFET

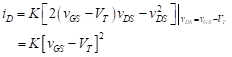

Siirtyminen triodin ja normaalin toiminta-alueen välillä (jota kutsutaan kyllästysalueeksi ja usein tunnistetaan toimintaan puristustilassa) on esitetty katkoviivana kuviossa 7, jossa

![]()

(1)

Triodialueen rajalla käyrien polvet noudattavat suunnilleen suhdetta,

![]()

(2)

Yhtälössä (2) K on tietyn laitteen vakio. Sen arvo riippuu laitteen mitoista ja sen rakentamisessa käytetyistä materiaaleista. Vakio annetaan,

![]()

(3)

Tässä yhtälössä μn on elektronin liikkuvuus; Coksidi, oksidikapasitanssi on kapasitanssi portin pinta-alaa kohti; W on portin leveys; L on portin pituus. Yhtälö osoittaa monimutkaisen ja epälineaarisen suhteen iD ja kaksi jännitettä, vDS ja vGS. Koska haluaisimme tyhjennysvirran vaihtelevan suunnilleen lineaarisesti vGS (itsenäinen vDS), FET: ää ei yleensä käytetä triodialueella.

Haluamme nyt löytää yhtälön kyllästysalueen toimintakäyrille. Voimme määrittää arvot siirtymässä triodin ja kylläisyyden välillä arvioimalla yhtälön (2) siirtymässä (polvi). Tuo on,

(4)

Tämä yhtälö määrittää tyhjennysvirran suuruuden rajalla (katkoviiva kuviossa 8) portin ja lähdön jännitteen funktiona vGS. Tarvittaessa voimme ottaa huomioon kyllästysalueen ominaispiirrosten pienen kaltevuuden lisäämällä lineaarisen tekijän.

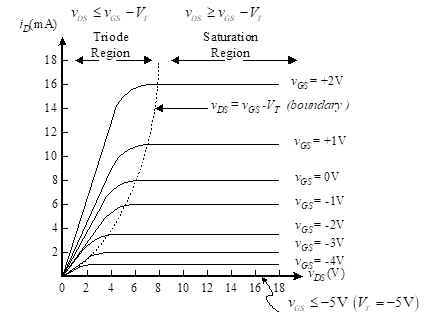

![]()

(5)

Yhtälössä (5) λ on pieni vakio (kuvassa 8 esitettyjen tunnusominaisuuksien käyrän lähellä olevan vaakasuoran osan kaltevuus). Se on yleensä pienempi kuin 0.001 (V-1). Sitten

![]()

(6)

Kaikki aiemmat keskustelut käsittelivät NMOS-transistoria. Keskustelemme nyt lyhyesti PMOS: n tarpeellisista muutoksista. PMOS: n arvot ovat vDS on negatiivinen. Lisäksi voit luoda kanavan PMOS: ssa ![]() .

.

Kuva 8 - MOSFET-transistorin päätteen ominaisuudet

Ainoat muutokset NMOS-transistoreiden ominaisuuksista (kuvio 7) on, että vaakasuora akseli on nyt -vDS + v: n sijaanDS, ja parametriset käyrät edustavat suurempaa tyhjennysvirtaa, kun porttijännite pienenee (sen sijaan, että NMOS-transistori kasvaisi). Virta-arvojen nousukäyrät vastaavat enemmän negatiivista porttijännitettä. Kun vGS > VT, transistori on katkaistu. Parannus PMOS, VT on negatiivinen, ja PMOS: n VT on positiivinen.

PMOS-transistorin triodialueen siirtymän virran yhtälö on identtinen NMOS-arvon kanssa. Tuo on,

![]()

(7)

Huomaa, että vGS ja vDS ovat molemmat negatiivisia määriä. PMOS-transistorin kyllästysalueen yhtälö on myös sama kuin NMOS: n. Tuo on,

(8)

Huomaa, että λ on negatiivinen PMOS-transistoreille, koska käyrän muutosnopeus (![]() ) on negatiivinen.

) on negatiivinen.

Kun otetaan yhtälön (6) molempien puolien osittainen johdannainen suhteessa vGS, ![]() , saamme

, saamme

![]()

(9)

Suosimme arvoa gm olla vakio, erityisesti suurten signaalin vaihteluiden osalta. Tätä tilannetta voidaan kuitenkin arvioida vain, jos käytämme FET: ää pieniin signaalisovelluksiin. Suurissa signaalin olosuhteissa aaltomuodon vääristyminen voi olla hyväksyttävää joissakin sovelluksissa.

2.2-tyhjennys-tila MOSFET

Edellisessä osassa käsiteltiin parannustilaa MOSFET. Kontrastamme tätä nyt tyhjennystilaan MOSFET. Varten n-kanavan tehostustila kanavan hankkimiseksi meidän piti soveltaa positiivista jännitettä portille. Tämän jännitteen oli oltava riittävän suuri pakottamaan riittävä määrä liikkuvia elektroneja tuottamaan virtaa indusoidussa kanavassa.

Kuva 9 - tyhjennystilan n-kanava MOSFET

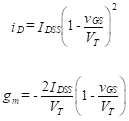

In n-kanavan tyhjennystila MOSFET, emme tarvitse tätä positiivista jännitettä, koska meillä on fyysisesti implantoitu kanava. Tämä antaa meille mahdollisuuden olla virtaa tyhjennys- ja lähdeliittimien välillä, vaikka porttiin kohdistettaisiin negatiivisia jännitteitä. Luonnollisesti portille kohdistettavan negatiivisen jännitteen määrälle on raja, vaikka virtaa edelleen valuu ja lähde. Tämä raja tunnistetaan jälleen kynnysjännitteeksi, VT. Muutos parannustilasta on se, että portti-lähde-jännite voi nyt olla joko negatiivinen tai positiivinen, kuten kuvassa 9 on esitetty.

Yhtälöt, jotka määrittävät tyhjennystilan MOSFET-toiminnon, ovat hyvin samankaltaisia kuin parannustilassa. Tyhjennysvirran arvo, kun vGS on nolla IDSS. Tätä kutsutaan usein nimellä tyhjennyslähteen kyllästysvirta, Tai nollaportin tyhjennysvirta. Verrattaessa parannustilan MOSFETin yhtälöitä tyhjennystilaan, löydämme

![]()

(10)

Sitten löydämme

(11)

Purkautumistila MOSFETit ovat saatavilla erillisissä muodoissa tai ne voidaan valmistaa integroitujen piirien siruilla aivan parannustilan tyyppien kanssa. Tämä sisältää molemmat p-tyyppinen ja n-tyyppi. Tämä mahdollistaa suuremman joustavuuden piirisuunnittelutekniikoissa.

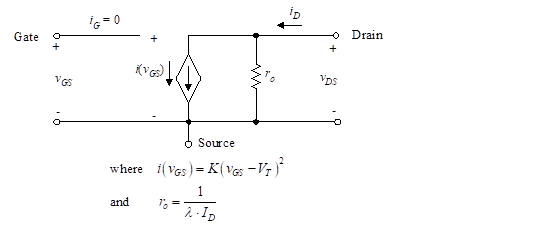

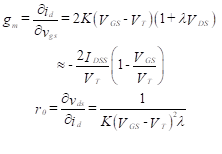

2.3 Suuren signaalin vastaava piiri

Haluamme nyt kehittää vastaavan piirin, joka edustaa kuvion 8 [yhtälö (5) tai (8)] suurten signaalien ominaisuuksia kyllästysalueella. Huomaa, että tyhjennysvirta, iD, riippuu vGS ja vDS. Vakiona portti-lähde-jännitteeksi käytämme yhtä kuvan parametrikäyristä ja suhde on suunnilleen suora. Suoraviivainen suhde virran ja jännitteen välille mallinnetaan vastuksella. Siksi vastaava piiri koostuu vastuksesta, joka on rinnakkain virtalähteen kanssa, jossa virtalähteen arvo määrittää osan tyhjennysvirrasta vGS. Käyrän kaltevuus riippuu vGS. Rinne on osittainen johdannainen,

![]()

(12)

jossa r0 on inkrementaalinen lähtöteho. Näemme yhtälöstä [(5) tai (8)], että tämä vastus on

![]()

(13)

missä käytämme isoja kirjaimia VGS osoitetaan, että vastus on määritelty tietylle vakioarvolle portti-lähde -jännitteelle. Lopullinen likiarvo yhtälössä (13) saadaan yhtälöstä (5) olettaen, että λ on pieni. Vastus on siis kääntäen verrannollinen virhevirtaan, ID. Suuren signaalin vastaavan mallin antaa sitten kuva 11 missä r0 on yhtä suuri kuin yhtälössä (13) kehitetty.

Kuva 11 - Suuri signaali vastaava piiri

2.4 MOSFETin pienimuotoinen malli

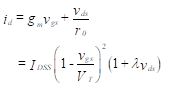

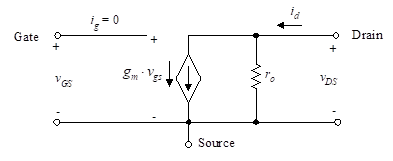

Haluamme nyt tarkastella yhtälöön liittyviä lisävaikutuksia. Kolmen piirin parametrit tässä yhtälössä, iD, vGS ja vDS koostuvat molemmista dc (bias) ja ac komponentteja (siksi olemme käyttäneet ilmaisuihin isoja kirjaimia). Olemme kiinnostuneita ac pienen signaalin mallin komponentit. Näemme, että tyhjennysvirta on riippuvainen kahdesta jännitteestä, portista lähteeseen ja valua lähteestä. Lisäarvojen osalta voimme kirjoittaa tämän suhteen

(14)

Yhtälössä (14) gm is eteenpäin suuntautuva johtavuus ja r0 on lähtöteho. Niiden arvot löytyvät ottamalla osittaiset johdannaiset yhtälössä (5). Täten,

(15)

Yhtälön (15) lähentyminen johtuu havainnosta, joka λ jos se on pieni. Yhtälö (14) johtaa kuvion 12 pieneen signaalimalliin.

Kuva 12 - pienimuotoinen MOSFET-malli

NYKYINEN - 2. Metallioksidipuolijohde FET (MOSFET)

NYKYINEN - 2. Metallioksidipuolijohde FET (MOSFET) PREVIOUS- 1. FET-järjestelmien edut ja haitat

PREVIOUS- 1. FET-järjestelmien edut ja haitat