2. Металооксидни полупроводникови FET (MOSFET)

Металооксидни полупроводникови FET (MOSFET)

Металооксидният полупроводник FET (MOSFET) е четири терминално устройство. Терминалите са източник (S), порта (G) намлява дренаж (D), Най- субстрат or тяло формира четвъртия терминал. MOSFET е конструиран с терминал на врата, изолиран от канала с диелектрик от силициев диоксид. MOSFETs може да бъде или изчерпване or режим на повишаване, Тези два термина определяме скоро.

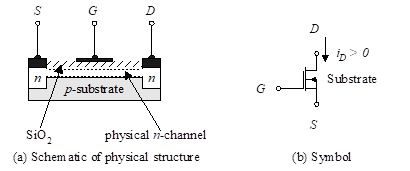

Фигура 1 - Изчерпване на n-каналите MOSFET

MOSFETs понякога се наричат IGFET (изолирани портални транзистори) поради SiO2 слой, използван като изолатор между вратата и основата. Ние започваме нашия анализ с MOSFET с изчерпване на режима. Точно както BJTs могат да бъдат или NPN or PNP, MOSFETs може да бъде един от двамата n-канал (NMOS) или p-канал (PMOS). Фигура 1 илюстрира физическата структура и символа за n-изчерпване на каналите MOSFET. Забележете, че субстратът е свързан към терминала на източника. Това почти винаги ще бъде така.

Изчерпването на MOSFET се конструира с a физически между канала и източника. В резултат, когато напрежението, vDS, се прилага между източник и източник, ток, iD, съществува между източник и източник, въпреки че терминалът на порта G остава несвързан (vGS = 0 V).

Изграждането на n- изчерпване на каналите MOSFET започва с p-прекъснат силиций. Най- nизкопните и отводнителните кладенци образуват връзки с ниско съпротивление между краищата на n-канал, както е показано на фигурата 1. Нанася се тънък слой силициев диоксид, покриващ зоната между източника и оттока. SiO2 е изолатор. Алуминиев слой се нанася върху изолатор от силициев диоксид, за да се образува терминал на врата. В действие, отрицателен vGS изтласква електрони от региона на канала, като по този начин изчерпва канала. Кога vGS достига определено напрежение, VT, каналът е притиснат, Положителни стойности на. \ T vGS увеличаване на размера на канала, което води до увеличаване на изтичащия ток. Изчерпването на MOSFET може да работи с положителни или отрицателни стойности на vGS, Тъй като портата е изолирана от канала, токът на вратата е пренебрежимо малък (по реда на 10-12 A).

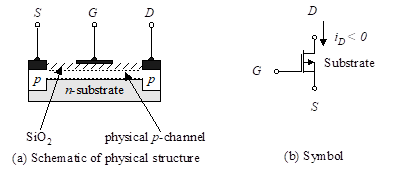

Фигура 2 - Изчерпване на P-канала MOSFET

Фигура 2 е сравнима с фигура 1, с изключение на това, че сме променили n-изчерпване на каналите MOSFET към a p-изчерпване на каналите MOSFET.

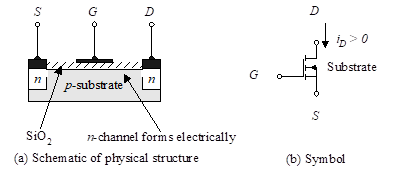

- nУсилване на каналите MOSFET е показано на фигура 3 заедно със символа на схемата. Това е най-често използваната форма на полеви транзистор.

Фигура 3 - MOSFET за подобряване на n-канала

- n-Подобряване на каналите MOSFET се различава от изчерпването на MOSFET, като не разполага с тънка n-слой. Тя изисква положително напрежение между портата и източника, за да се установи канал. Този канал се формира от действието на положително напрежение от врата до източник, vGS, който привлича електрони от субстратната област между n- изтичане и източник. Положителен vGS причинява електрони да се натрупват на повърхността под оксидния слой. Когато напрежението достигне праг, VTдостатъчен брой електрони се привличат в този регион, за да го накарат да действа като проводник nканален. Няма значим изтичащ ток, iD съществува до vGS надвишава VT.

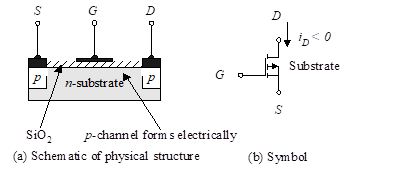

Фигура 4 е сравнима с фигура 3, с изключение на това, че сме променили n-канал подобрение MOSFET към a pусилване на каналите MOSFET.

Фигура 4 - P-канален усилвател MOSFET

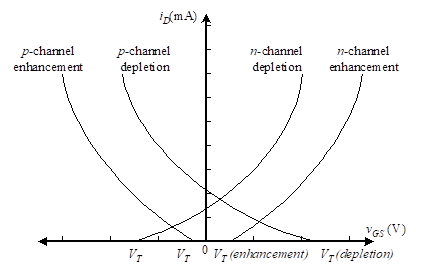

Като обобщение, фамилията MOSFET показва идентифицирането iD в сравнение с vGS криви, показани на фигура 5. Всяка характеристична крива е разработена с достатъчно напрежение на източник-източник vDS да поддържа устройството в нормалния работен район на. \ t iD в сравнение с vDS криви. Обсъждането в следващите раздели ще определи праговото напрежение VT за повишаване MOSFETs и изчерпване MOSFETs.

Фигура 5 - iD в сравнение с vGS характеристики на семейството MOSFET за достатъчно напрежение източник източник VDS

Характеристики на MOSFET за подобряване на режима на 2.1

Сега, след като представихме основната структура и основа за работа на MOSFET, използваме подход, за да изследваме поведението на терминала на устройството в режим на подобрение. Нека първо направим някои общи наблюдения от Фигура 1. Помислете за нормалния поток на тока в MOSFET като за оттичане към източника (точно както в BJT, той е между колектор и емитер). Както при NPN BJT, две гръб-назад диоди съществуват между изтичане и източник. Затова трябва да приложим външни напрежения към портата, за да позволим на тока да тече между изтичането и източника.

Ако ние земята на източника, и се прилага положително напрежение към портата, че напрежението е ефективно на врата-към-източник на напрежение. Положителното напрежение на вратата привлича електрони и отблъсква дупките. Когато напрежението надвишава прага (VT), достатъчно електрони се привличат, за да образуват проводящ канал между източник и източник. В този момент транзисторът се включва и токът е функция и на двете vGS намлява vDS, Трябва да е ясно, че VT е положително число за n-канално устройство и отрицателно число за a p-канално устройство.

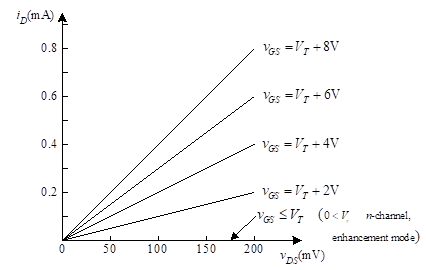

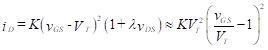

Веднъж създаден канал (т.е. vGS >VT), текущият поток може да възникне в този канал между източник и източник. Този ток зависи от това vDS, но също така зависи и от vGS. Когато vGS едва превишава прага на напрежението, много малко ток може да тече. Като vGS увеличава над прага, каналът съдържа повече носители и са възможни по-високи токове. Фигура 6 показва връзката между iD намлява vDS където vGS е параметър. Обърнете внимание на това за vGS по-малко от прага, няма текущи потоци. За по-висока vGS, връзката между iD намлява vDS е приблизително линейно, което показва, че MOSFET се държи като резистор, чието съпротивление зависи от vGS.

Фигура 6 -iD в сравнение с vDS за режим на подобрение n-канал MOSFET кога vDS е малък

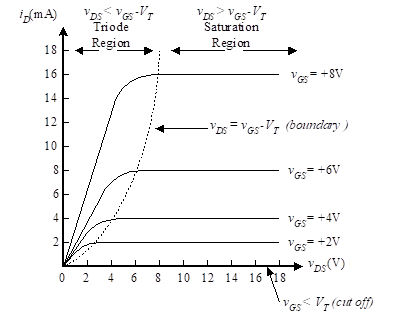

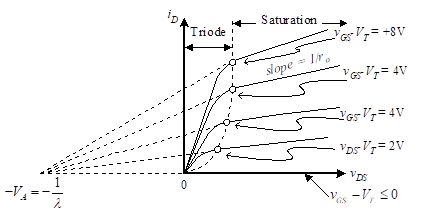

Кривите на фигура 6 приличат на прави линии. Въпреки това, те няма да продължат като прави линии, когато vDS става по-голям. Припомнете си, че за създаване на проводящия канал се използва положително напрежение. Той прави това чрез привличане на електрони. Положителното напрежение на изтичане прави същото нещо. Когато се приближаваме към края на канала, напрежението, което създава канала, се приближава vGS-vDS тъй като двата източника се противопоставят един на друг. Когато тази разлика е по-малка от VT, каналът вече не съществува за цялото пространство между източник и източване. Каналът е скован в края на изтичането и по-нататъшно увеличаване на vDS не водят до увеличаване на iD, Това е известно като нормален работен регион или насищане Област, показана на фигура 7, по хоризонталната част на характеристичните криви. Когато разликата е по-голяма от VT, ние наричаме това триод режим, защото потенциалът на трите терминала влияе силно на тока.

Предишната дискусия води до работните криви на фигура 7.

Фигура 7 -iD в сравнение с vGS за MOSFET с подобрен режим

Преходът между триод и нормален работен регион (наричан регион на насищане и често идентифициран като операция в режим на изключване) е показан като пунктирана линия на фигура 7, където

![]()

(1)

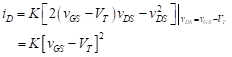

На границата на триодната област коленете на кривите приблизително следват връзката,

![]()

(2)

В уравнение (2), K е константа за дадено устройство. Неговата стойност зависи от размерите на устройството и използваните материали в неговата конструкция. Константата се дава от,

![]()

(3)

В това уравнение, μn е подвижността на електрони; Cокисоксидният капацитет е капацитетът на единица площ на портата; W е ширината на портата; L е дължината на портата. Уравнението показва сложна и нелинейна връзка между iD и двете напрежения, vDS намлява vGS, Тъй като ние бихме искали изтичане на ток да се различават приблизително линейно с vGS (независим от vDS), БНТ обикновено не се използва в триодната област.

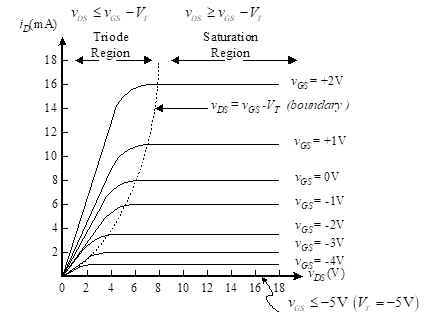

Сега искаме да намерим уравнение за работните криви в региона на насищане. Можем да установим стойностите при прехода между триодната и наситената зона чрез оценяване на Уравнение (2) при прехода (коляно). Това е,

(4)

Това уравнение установява величината на тока на изтичане на границата (пунктирана линия на фигура 8) като функция на напрежението от врата до източник. vGS, Ако е необходимо, можем да обясним лекия наклон на характеристичните криви в областта на насищане, като добавим линеен фактор.

![]()

(5)

В уравнение (5), λ е малка константа (наклонът на близката хоризонтална част на характеристичните криви, показани на фигура 8). Обикновено е по-малък от 0.001 (V-1). Тогава

![]()

(6)

Всички наши предишни дискусии се занимаваха с транзистора NMOS. Сега ще обсъдим накратко необходимите промени за PMOS. За PMOS стойностите на vDS ще бъде отрицателен. Освен това, за да създадете канал в PMOS, ![]() .

.

Фигура 8 - Терминални характеристики на MOSFET транзистор

Единствената промяна от характеристиките на NMOS транзисторите (Фигура 7) е, че хоризонталната ос сега е -vDS вместо + vDS, и параметричните криви представляват по-голям изходен ток, тъй като напрежението на затвора намалява (вместо да се увеличава за NMOS транзистора). Кривите за увеличаване на токовите стойности съответстват на повече отрицателно напрежение на задвижването. Кога vGS > VT, транзисторът е прекъснат. За подобряване на PMOS, VT е отрицателен, а за изчерпване на PMOS, VT е положителна.

Уравнението за тока при прехода на триодния регион за транзистора PMOS е идентичен с този на NMOS. Това е,

![]()

(7)

Имайте предвид, че vGS намлява vDS и двете са отрицателни количества. Уравнението за областта на насищане в транзистора PMOS също е идентично с това на NMOS. Това е,

(8)

Имайте предвид, че λ е отрицателен за PMOS транзистори, тъй като скоростта на промяна на кривата (![]() ) е отрицателен.

) е отрицателен.

Поемане на частичната производна на двете страни на уравнението (6) по отношение на vGS, ![]() , получаваме

, получаваме

![]()

(9)

Ние предпочитаме стойността на gm да бъде постоянен, особено при големи колебания на сигнала. Въпреки това, ние можем само да приближим това условие, ако използваме БНТ за малки сигнални приложения. При големи условия на сигнала изкривяването на вълната може да бъде неприемливо в някои приложения.

MOSFET за изчерпване на режима 2.2

Предишният раздел разглеждаше MOSFET от подобрения режим. Сега контрастираме с MOSFET с изчерпване на режима. За n-канал подобрение режим, за да придобият канал, ние трябваше да приложи положително напрежение на портата. Това напрежение трябваше да бъде достатъчно голямо, за да принуди достатъчен брой мобилни електрони да произведат ток в индуциран канал.

Фигура 9 - режим на изчерпване n-channel MOSFET

в n-режим на изчерпване на канала MOSFET, нямаме нужда от това положително напрежение, тъй като имаме физически имплантиран канал. Това ни позволява да имаме ток между клемите за източване и източника дори при отрицателни напрежения, приложени към портата. Разбира се, има ограничение за размера на отрицателното напрежение, което може да се приложи към портата, като същевременно има токов поток между канализацията и източника. Тази граница отново се определя като праговото напрежение, VT. Промяната от режима на подобрение е, че напрежението от врата към източник вече може да бъде отрицателно или положително, както е показано на Фигура 9.

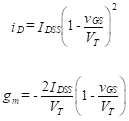

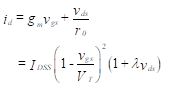

Уравненията, които определят работата на MOSFET с изчерпване на режима, са много сходни с тези на режима на усилване. Стойността на изтичащия ток, когато vGS е нула е идентифициран като IDSS, Това често се нарича ток на насищане на източник-източникИли нулев входен ток на източване, Сравнявайки уравненията на MOSFET с подобрения режим с тези на режима на изчерпване, откриваме

![]()

(10)

След това откриваме,

(11)

Режимът на изчерпване MOSFETs се предлагат в дискретна форма, или могат да бъдат произведени върху чипове на интегрални схеми, заедно с типовете подобрения. Това включва и двете p-тип и n-Тип. Това позволява по-голяма гъвкавост в техниките за проектиране на вериги.

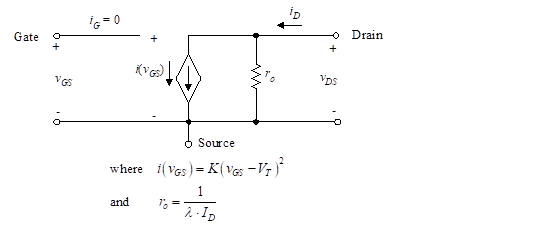

2.3 Схема на еквивалент на голям сигнал

Сега искаме да разработим еквивалентна схема, която представя характеристиките на големия сигнал на фигура 8 [Уравнение (5) или (8)] в областта на насищане. Имайте предвид, че изтичащият ток, iD, зависи от vGS намлява vDS. За постоянно напрежение от порта към източника работим по една от параметричните криви на фигурата и връзката е приблизително права линия. Правата връзка между тока и напрежението се моделира от резистор. Следователно еквивалентната верига се състои от резистор, паралелен на източника на ток, където стойността на източника на ток установява частта от източващия ток vGS, Наклонът на кривата зависи от vGS, Наклонът е частично производно,

![]()

(12)

където r0 е нарастващото изходно съпротивление. От Уравнение (5) или (8) виждаме, че това съпротивление е дадено от

![]()

(13)

където използваме горен случай VGS за да покаже, че съпротивлението е определено за конкретна постоянна стойност на напрежението от вход към източник. Крайното приближение в уравнението (13) е резултат от уравнение (5) с предположението, че λ е малък. Следователно съпротивлението е обратно пропорционално на тока на отклонение, ID, Големият еквивалентен модел на сигнала след това се дава от фигура 11, където r0 е както е разработено в Уравнение (13).

Фигура 11 - Схема на еквивалент на голям сигнал

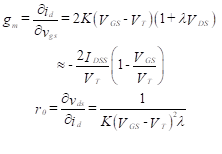

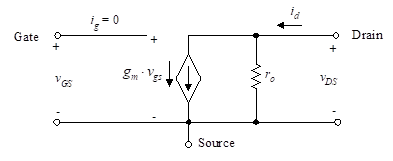

2.4 Малък сигнален модел на MOSFET

Сега искаме да разгледаме постепенните ефекти, свързани с уравнението. Трите параметъра на веригата в това уравнение, iD, vGS намлява vDS са съставени и от двете dc (пристрастие) и ac компоненти (затова сме използвали горни регистърни букви в изразите). Ние се интересуваме от ac компоненти за модела с малък сигнал. Виждаме, че изтичането на ток зависи от две напрежения, от портата до източника и от източване към източник. За инкременталните стойности можем да напишем тази връзка като

(14)

В уравнение (14), gm is напрежението напред намлява r0 е изходното съпротивление. Техните стойности се намират чрез поемане на частични производни в уравнение (5). Поради това,

(15)

Апроксимацията в уравнението (15) е резултат от наблюдението λ ако е малък. Уравнението (14) води до малък сигнал от фигура 12.

Фигура 12 - Малък сигнален MOSFET модел

ТОК - 2. Металооксиден полупроводник FET (MOSFET)

ТОК - 2. Металооксиден полупроводник FET (MOSFET) ПРЕДИШЕН - 1. Предимства и недостатъци на FETs

ПРЕДИШЕН - 1. Предимства и недостатъци на FETs