5. MOSFET интегрални схеми

MOSFET интегрални схеми

Когато MOSFET транзисторите са произведени като част от интегрална схема, практическите съображения изискват две големи промени в конфигурациите на веригата. Първо, големите съединителни и байпасни кондензатори, използвани в дискретни усилватели, на практика не могат да бъдат произведени в интегрални схеми поради малкия размер. Преодоляваме този недостатък, като произвеждаме директно свързани усилватели.

Втората голяма промяна е, че не можем лесно да произведем резистори, използвани като част от схемите за отклонение. Вместо това, ние използваме активни товари и източници на ток, съставени от MOS транзистори.

Интегрираните схеми използват както NMOS, така и PMOS вериги. CMOS е по-често срещана в цифровите схеми, докато NMOS обикновено се използва за ICs с по-висока плътност (т.е. повече функции на чип).

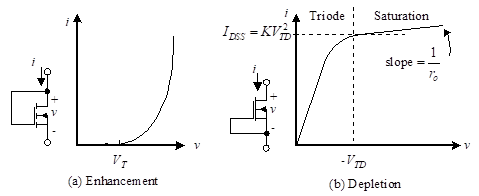

Симулирането на активни товари се възползва от наклона на MOS характеристичните криви. Фигура 23 показва два вида активни товари. На фигура 23 (a) показваме NMOS усилващ товар, докато 23 (b) показва натоварване с изчерпване на NMOS. На фигурата също са показани съответните характеристични криви.

Фигура 23 - Активни товари

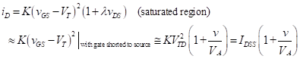

За усилващото натоварване NMOS връзката между напрежение и ток се определя от

![]()

(29)

Еквивалентното съпротивление на тази конфигурация е 1 /gm, където стойността на напрежението е тази, която се прилага в точката на отклонение.

Натоварването с изчерпване на NMOS има еквивалентно съпротивление, което се определя от наклона на характеристиката, дадена от следното уравнение

(30)

5.1 Biasing на MOSFET интегрални схеми

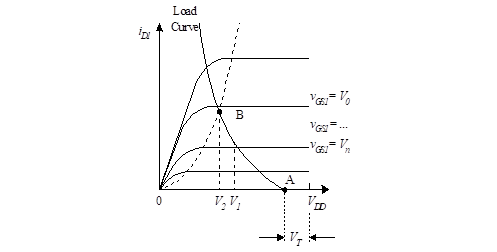

Сега, когато имаме две техники за симулиране на активни натоварвания, можем да се справим с проблема. Ние използваме активното натоварване на мястото на съпротивлението на товара в която и да е конфигурация на веригата. За да покажем техниката за анализирането им, нека разгледаме NMOS усилвателя, използвайки усилващ товар, както е показано на фигура 24.

Транзисторът е означен Q2 замества RD на нашите по-ранни схеми. За да определим неподвижната работна точка, използваме същите техники, както направихме в Раздел 4, „Конфигурации на FET усилвателя и отклонение“, само замествайки графичната характеристика на натоварването на усилването за товарната линия на резистора. Тоест, трябва да намерим едновременното решение на характеристиките на транзистора на полевия транзистор с уравнението за товарната линия. Можем да направим това графично, както е показано на фигура 25.

Параметричните криви са характеристичните криви за усилващия транзистор Q1, Напрежението спрямо токовата характеристика на активния товар, Q2 са тези от фигура 23. Изходното напрежение, vот, е разликата между VDD и напрежението в активния товар. Токът в активния товар е същият като тока на източване в усилващия транзистор. Затова конструираме линията на натоварване, като вземем изместеното огледално изображение на характеристиката на фигура 23. Работната точка е пресечната точка на тази крива с подходящата характеристична крива на транзистора. Трябва да намерим напрежението порта-към-източник, за да знаем коя транзисторна крива да изберем. Както ще видим по-нататък, напрежението на входното отклонение често се заменя с активен източник на ток.

Фигура 25 - Графично решение за Q-точката

Сега, когато знаем как да симулираме активното натоварване, обръщаме внимание на генерирането на референтен ток, който да се използва като част от веригата за входно отклонение. Тези източници на ток се използват по същия начин, по който ги използваме за отклоняване на усилвателя BJT.

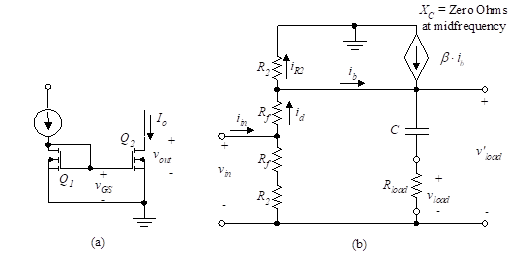

Фигура 26 - Текущо огледало

Ние анализираме MOSFET текущата огледало, Текущото огледало е показано на фигура 26. Предполага се, че двата транзистора са напълно съвпадащи. Изходният ток е изтичащият ток на Q2и референтен ток Q1. Ако транзисторите са напълно съчетани, изходният ток ще бъде точно равен на референтния ток. Това е вярно, тъй като транзисторите са свързани паралелно. Точно както беше случаят с BJT текущото огледало, референтният ток може да се генерира чрез прилагане на еталонно напрежение върху еталонно съпротивление, както е показано на Фигура 26 (b).

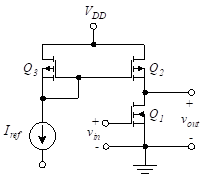

Поставянето на различните подсхеми заедно (т.е. активния товар и еталонния ток) води до CMOS усилвател на фигура 27.

Печалбата на този усилвател се дава от

![]()

(31)

Фигура 27 - CMOS усилвател

Ефект на тялото 5.2

Нашата дискусия по раздел „2. Метал-оксиден полупроводник FET (MOSFET) “се отнася до основата (или тялото) на MOSFET. Този субстрат играе важна роля при установяването на канала. При работата на дискретни MOSFET-та, тялото често е свързано към източника на захранване. В такива случаи субстратът няма пряк ефект върху работата на устройството и се прилагат кривите, разработени по-рано в тази глава.

Ситуацията се променя, когато MOSFETs са произведени като част от интегрални схеми. В такива случаи субстратът на всеки отделен транзистор не е изолиран от други субстрати. Всъщност, субстрат често се споделя между всички MOSFET на чип. В PMOS IC, споделен субстрат ще бъде свързан с най-положителен източник терминал, докато в NMOS е свързан с земята (или с отрицателна доставка, ако има такива). Това установява обратното отклонение между източника и тялото на всеки транзистор. Ефектът от това обратното отклонение е да се променят работните характеристики. Например, в n-канално устройство, ефективно повишава прага (VT). Количеството, с което прагът се променя, зависи от физическите параметри и конструкцията на устройството. За NMOS тази промяна може да бъде сближена с

![]()

(32)

В уравнение (32), γ е параметър на устройството, който варира между 0.3 и 1 (V-1/2). VSB е напрежението източник към тялото и е Ферми потенциал, Това е свойство на материала и типична стойност е 0.3 V за силиций.

ТОК - 5. MOSFET интегрални схеми

ТОК - 5. MOSFET интегрални схеми ПРЕДИШЕН - 4. Конфигурации на усилвателя и приплъзване

ПРЕДИШЕН - 4. Конфигурации на усилвателя и приплъзване