2. Metal-oksidni poluvodički FET (MOSFET)

Metal-oksidni poluvodički FET (MOSFET)

Metalni oksidni poluvodič FET (MOSFET) je četvero terminalni uređaj. Terminali su izvor (S), kapija (G) i odvod (D). The supstrat or tijelo formira četvrti terminal. MOSFET je konstruisan sa terminalom za izolaciju od kanala sa dielektrikom od silicijum dioksida. MOSFET-ovi mogu biti oba osiromašeni or mod poboljšanja. Uskoro definišemo ova dva termina.

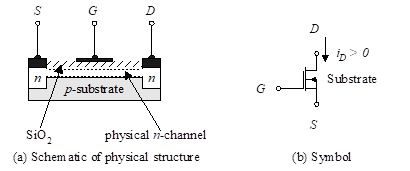

Slika 1 - N-kanal depletion MOSFET

MOSFET-ovi se ponekad nazivaju IGFET-i (izolirani tranzistori s efektom polja) zbog SiO2 sloj koji se koristi kao izolator između kapije i podloge. Svoju analizu započinjemo sa MOSFET-om u načinu iscrpljivanja. Baš kao i BJTs npn or pnp, MOSFET-ovi mogu biti n-kanal (NMOS) ili p-kanal (PMOS). Slika 1 ilustruje fizičku strukturu i simbol za n-Kanal osiromašen MOSFET. Obratite pažnju da je supstrat povezan sa izvornim terminalom. To će gotovo uvijek biti slučaj.

MOSFET iscrpljivanja je konstruisan sa a fizički kanal umetnut između odvoda i izvora. Kao rezultat, kada napon, vDS, se primjenjuje između odvoda i izvora, struja, iD, postoji između odvoda i izvora, iako terminal G ostaje nepovezan (vGS = 0 V).

Izgradnja n-Kanal osiromašen MOSFET počinje sa p-dopirani silicij. The n-dodirani izvor i bunari za drenažu formiraju veze niskog otpora između krajeva n-kanal, kao što je prikazano na slici 1. Nanesen je tanki sloj silicij-dioksida koji pokriva područje između izvora i odvoda. The SiO2 je izolator. Na izolatoru od silicij-dioksida se nanosi sloj aluminija kako bi se formirao terminal za vrata. U radu, negativan vGS izbacuje elektrone iz regiona kanala, čime se iscrpljuje kanal. Kada vGS dostiže određeni napon, VT, kanal je stegnut. Pozitivne vrijednosti vGS povećati veličinu kanala, što rezultira povećanjem struje odvoda. MOSFET može da radi sa pozitivnim ili negativnim vrednostima vGS. Pošto je kapija izolovana od kanala, struja kapije je zanemarivo mala (po redu 10-12 A).

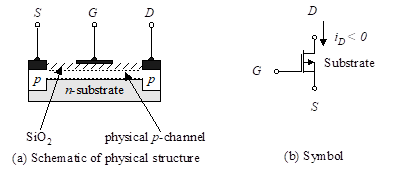

Slika 2 - pražnjenje p-kanala MOSFET

Slika 2 je usporediva sa slikom 1, osim što smo promijenili n-Kanal osiromašen MOSFET na a p-Kanal osiromašen MOSFET.

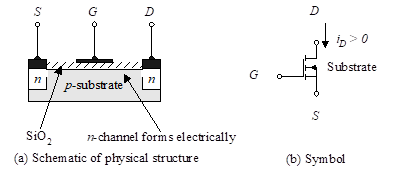

The nMOSFET je prikazan na slici 3 zajedno sa simbolom kruga. Ovo je najčešće korišteni oblik tranzistora s efektom polja.

Slika 3 - MOSFET za poboljšanje n-kanala

The nMOSFET se razlikuje od MOSFET osiromašenja tako što nema tanak n-layer. Za uspostavljanje kanala je potreban pozitivan napon između kapije i izvora. Ovaj kanal se formira djelovanjem pozitivnog napona gate-to-source, vGSkoji privlači elektrone iz područja supstrata između n-izvučeni odvod i izvor. Pozitivno vGS uzrokuje nakupljanje elektrona na površini ispod sloja oksida. Kada napon dostigne prag, VTdovoljan broj elektrona privučen je ovim područjem da bi se ponašao kao provodnik n-kanal. Nema značajne struje odvoda, iD postoji do vGS prevazilazi VT.

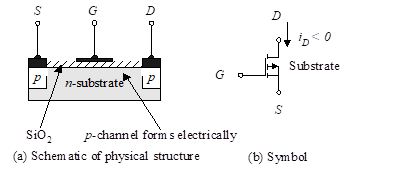

Slika 4 je usporediva sa slikom 3, osim što smo promijenili n-kanalno poboljšanje MOSFET na a pMOSFET.

Slika 4 - P-kanal poboljšanja MOSFET

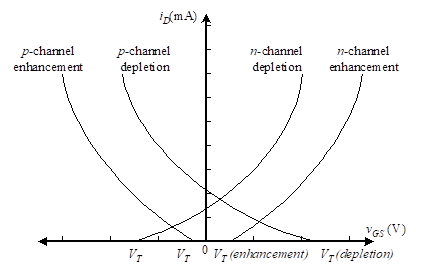

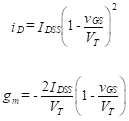

Kao rezime, porodica MOSFET pokazuje identifikaciju iD protiv vGS krive prikazane na slici 5. Svaka karakteristična krivulja je razvijena sa dovoljnim naponom odvodnog izvora vDS za održavanje uređaja u normalnom radnom području iD protiv vDS krivulje. Diskusija u kasnijim odeljcima definisaće napon praga VT i za poboljšanje MOSFET-ova i za MOSFET-ove za osiromašenje.

Slika 5 - iD protiv vGS karakteristike MOSFET porodice za dovoljan napon izvora odvoda VDS

2.1 MOSFET karakteristike poboljšanja moda

Sada kada smo predstavili osnovnu strukturu i osnovu za rad MOSFET-a, koristimo pristup kako bismo ispitali ponašanje terminala uređaja u režimu poboljšanja. Napravimo prvo neka općenita zapažanja sa slike 1. Zamislite da je normalni protok struje u MOSFET-u od odvoda do izvora (baš kao i u BJT, on je između kolektora i emitora). Kao i kod npn BJT, dva back-to-back dioda postoje između odvoda i izvora. Stoga, moramo primijeniti vanjske napone na kapiju kako bi se omogućilo da struja teče između odvoda i izvora.

Ako uzemljimo izvor i primenimo pozitivan napon na kapiju, taj napon je efektivni napon od vrata do izvora. Pozitivni napon kapije privlači elektrone i odbija rupe. Kada napon premaši prag (VT), dovoljno elektrona je privučeno da formira provodni kanal između odvoda i izvora. U ovom trenutku, tranzistor se uključuje i struja je funkcija oba vGS i vDS. Trebalo bi da bude jasno VT je pozitivan broj za n-kanalni uređaj i negativan broj za a p-kanalni uređaj.

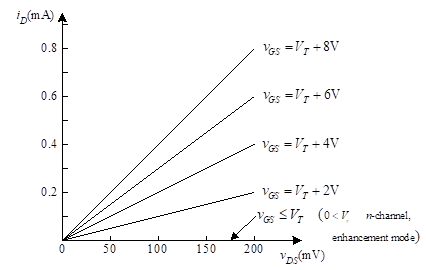

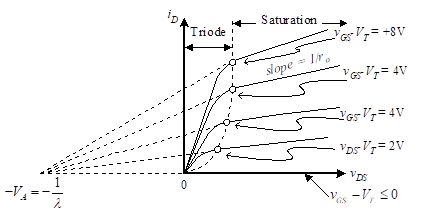

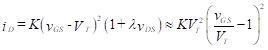

Kada je kanal kreiran (tj. vGS >VT), struja se može pojaviti u tom kanalu između odvoda i izvora. Ova struja ovisi o tome vDS, ali takođe zavisi od toga vGS. Kada vGS jedva prevazilazi prag napona, vrlo malo struje može teći. As vGS povećava se iznad praga, kanal sadrži više nosača i moguće su veće struje. Slika 6 pokazuje odnos između iD i vDS gdje vGS je parametar. Obratite pažnju na to vGS manje od praga, nema tekućih tokova. Za više vGS, odnos između iD i vDS je približno linearan ukazuje da se MOSFET ponaša kao otpornik čija otpornost ovisi vGS.

Slika 6 -iD protiv vDS za mod poboljšanja n-Kanal MOSFET kada vDS je mali

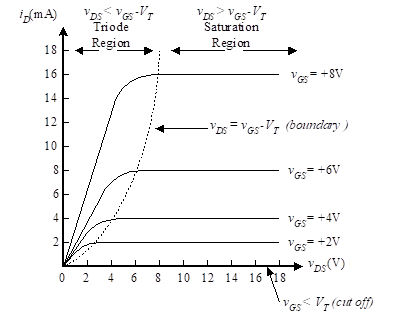

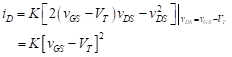

Krivulje slike 6 izgledaju kao ravne linije. Međutim, neće nastaviti kao ravne linije kada vDS postaje veći. Podsjetimo se da se za stvaranje kanala provodenja koristi pozitivan napon. To čini tako što privlači elektrone. Pozitivan napon odvoda radi istu stvar. Kako se približavamo odvodnom kraju kanala, napon stvara kanal vGS-vDS pošto se dva izvora suprotstavljaju jedni drugima. Kada je ta razlika manja od VT, kanal više ne postoji za cijeli prostor između izvora i odvoda. Kanal je ograničen na kraju odvoda, i dalje povećava u vDS ne dovode do povećanja iD. Ovo je poznato kao normalan operativni region ili zasićenje Područje prikazano na slici 7 po horizontalnom dijelu karakterističnih krivulja. Kada je razlika veća od VT, mi to zovemo triode modu, jer potencijali na sva tri terminala snažno utiču na struju.

Prethodna diskusija vodi ka operativnim krivuljama na slici 7.

Slika 7 -iD protiv vGS za MOSFET za poboljšanje

Prijelaz između triode i normalnog radnog područja (koji se naziva područje zasićenja i često identificiran kao rad u načinu rada pinch-off) operacije prikazan je kao isprekidana linija na slici 7, gdje je

![]()

(1)

Na granici triode regije, koljena krivina približno prate odnos,

![]()

(2)

U jednačini (2), K je konstanta za dati uređaj. Njegova vrednost zavisi od dimenzija uređaja i materijala koji se koriste u njegovoj konstrukciji. Konstanta je data od,

![]()

(3)

U ovoj jednadžbi, μn mobilnost elektrona; Coksid, kapacitivnost oksida, je kapacitet po jedinici površine kapije; W je širina kapije; L je dužina kapije. Jednadžba ukazuje na komplicirani i nelinearni odnos između iD i dva napona, vDS i vGS. Pošto bismo željeli da se odvodna struja varira približno linearno vGS (nezavisno od vDS), FET se obično ne koristi u triodu.

Sada želimo pronaći jednadžbu za radne krivulje u području zasićenja. Vrijednosti na tranziciji između trioda i područja zasićenja možemo utvrditi procjenom jednadžbe (2) na prijelazu (koljeno). To je,

(4)

Ova jednadžba uspostavlja veličinu struje odvoda na granici (isprekidana linija na slici 8) kao funkciju napona od izvora do izvora vGS. Ako je potrebno, možemo objasniti mali nagib karakterističnih krivulja u području zasićenja dodavanjem linearnog faktora.

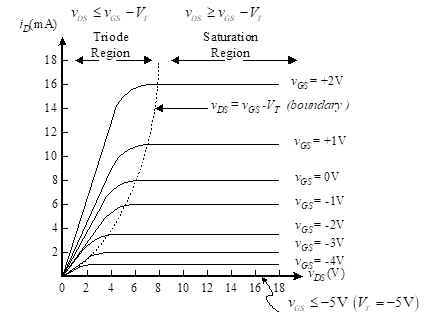

![]()

(5)

U jednačini (5), λ je mala konstanta (nagib horizontalnog dijela karakterističnih krivulja prikazanih na slici 8). Obično je manji od 0.001 (V-1). Onda

![]()

(6)

Sva naša prethodna diskusija odnosila se na NMOS tranzistor. Sada ćemo ukratko razmotriti neophodne modifikacije za PMOS. Za PMOS, vrijednosti vDS će biti negativna. Pored toga, da biste kreirali kanal u PMOS-u, ![]() .

.

Slika 8 - Karakteristike terminala MOSFET tranzistora

Jedina promena u odnosu na karakteristike NMOS tranzistora (slika 7) je da je sada horizontalna osa -vDS umesto + vDS, i parametarske krivulje predstavljaju veću odvodnu struju kako se napon kapije smanjuje (umjesto povećanja za NMOS tranzistor). Krivulje za povećanje strujnih vrijednosti odgovaraju većem negativnom naponu vrata. Kada vGS > VT, tranzistor je isključen. Za poboljšanje PMOS, VT je negativan, a za iscrpljenje PMOS, VT je pozitivan.

Jednadžba za struju tranzicije triode regije za PMOS tranzistor je identična onoj za NMOS. To je,

![]()

(7)

Zapiši to vGS i vDS oba su negativne količine. Jednadžba za područje zasićenja u PMOS tranzistoru je također identična onoj za NMOS. To je,

(8)

Zapiši to λ je negativan za PMOS tranzistore od brzine promjene krivulje (![]() ) je negativan.

) je negativan.

Uzimajući parcijalni derivat obe strane jednačine (6) u odnosu na vGS, ![]() , dobijamo

, dobijamo

![]()

(9)

Mi više volimo vrednost gm da bude konstantan, posebno za velike promene signala. Međutim, ovo stanje možemo samo približiti ako koristimo FET za male signalne aplikacije. Za velike uslove signala, izobličenje talasnog oblika može biti neprihvatljivo u nekim aplikacijama.

2.2 Depletion-Mode MOSFET

Prethodni odjeljak bavio se MOSFET-om poboljšanog načina rada. Sada to uspoređujemo sa MOSFET-om koji troši. Za n-kanalni mod poboljšanja, da bi stekao kanal morali smo primijeniti pozitivan napon na vratima. Ovaj napon je morao biti dovoljno velik da primora dovoljan broj pokretnih elektrona da proizvede struju u indukovanom kanalu.

Slika 9 - Način iscrpljivanja n-kanala MOSFET

U n-MOSFET u načinu iscrpljivanja kanala, ne treba nam ovaj pozitivni napon jer imamo fizički ugrađen kanal. To nam omogućava da imamo struju između odvodne i izvorne stezaljke čak i kada se negativni naponi primenjuju na kapiju. Naravno, postoji ograničenje količine negativnog napona koji se može primijeniti na kapiju, a da pritom struja struje ostaje između odvoda i izvora. Ova granica je opet identificirana kao prag napona, VT. Promjena u načinu poboljšanja je u tome što napon od ulaza do izvora sada može biti negativan ili pozitivan, kao što je prikazano na slici 9.

Jednadžbe koje definiraju rad MOSFET-a za iscrpljivanje su vrlo slične onima u modu poboljšanja. Vrijednost struje odvoda kada vGS je nula identifikovana kao IDSS. Ovo se često naziva i struja zasićenja izvora odvoda, Ili nultočna odvodna struja. Uspoređujući jednadžbe MOSFET moda poboljšanja s onima u modu osiromašenja, nalazimo

![]()

(10)

Onda nađemo,

(11)

Način iscrpljivanja MOSFET-ovi su dostupni u diskretnom obliku, ili se mogu proizvesti na čipovima sa integrisanim kolima, zajedno sa tipovima modova poboljšanja. Ovo uključuje i jedno i drugo p-type and n-tip. Ovo omogućava veću fleksibilnost u tehnikama dizajna krugova.

2.3 Sklop ekvivalentnog velikog signala

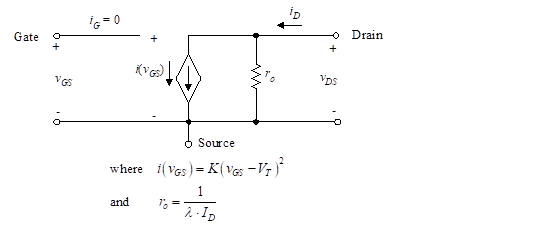

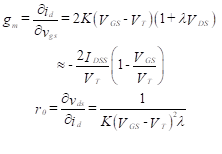

Sada želimo da razvijemo ekvivalentni sklop koji predstavlja karakteristike velikog signala slike 8 [Equation (5) ili (8)] u oblasti zasićenja. Imajte na umu da struja odvoda, iD, zavisi od vGS i vDS. Za konstantni napon od vrata do izvora radimo duž jedne od parametarskih krivulja na slici, a odnos je približno ravan. Ravni odnos između struje i napona modelira se otpornikom. Ekvivalentni krug se stoga sastoji od otpornika paralelno s izvorom struje gdje vrijednost izvora struje uspostavlja dio odvodne struje uslijed vGS. Nagib krivulje zavisi od vGS. Nagib je parcijalni derivat,

![]()

(12)

gdje r0 je inkrementalni izlazni otpor. Iz jednačine [(5) ili (8) vidimo da je ovaj otpor dat

![]()

(13)

gde koristimo gornji slučaj VGS da označi da je otpor definiran za određenu konstantnu vrijednost napona od vrata do izvora. Konačna aproksimacija u jednačini (13) je rezultat jednadžbe (5) uz pretpostavku da λ je mali. Otpor je stoga obrnuto proporcionalan struji prednapona, ID. Model ekvivalenta velikog signala se zatim daje na slici 11 gdje r0 je razvijen u jednačini (13).

Slika 11 - Sklop ekvivalentnog velikog signala

2.4 Mali signalni model MOSFET-a

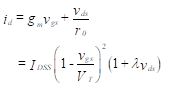

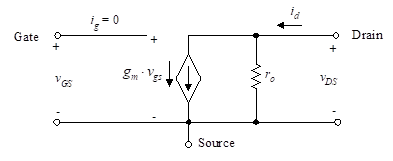

Sada želimo da pogledamo inkrementalne efekte vezane za jednačinu. Tri parametra kruga u toj jednadžbi, iD, vGS i vDS se sastoje od oba dc (pristrasnost) i ac komponente (zbog toga smo u izrazima koristili tabele velikih slova). Mi smo zainteresovani za ac komponente za model malog signala. Vidimo da struja odvoda zavisi od dva napona, od vrata do izvora i od odvoda do izvora. Za inkrementalne vrednosti možemo da napišemo ovaj odnos kao

(14)

U jednačini (14), gm is prolaznost prema naprijed i r0 je izlazni otpor. Njihove vrijednosti se dobivaju uzimanjem djelomičnih derivata u jednadžbi (5). Tako,

(15)

Aproksimacija u jednačini (15) je rezultat posmatranja λ ako je mala. Jednadžba (14) vodi do modela malog signala na slici 12.

Slika 12 - MOSFET model malog signala

STRUJA - 2. Metal-oksidni poluprovodnik FET (MOSFET)

STRUJA - 2. Metal-oksidni poluprovodnik FET (MOSFET) PREVIOUS- 1. Prednosti i nedostaci FET-ova

PREVIOUS- 1. Prednosti i nedostaci FET-ova