2. Металл-оксид Хагас дамжуулагч FET (MOSFET)

Металл-оксид Хагас дамжуулагч FET (MOSFET)

Металл-оксид хагас дамжуулагч FET (MOSFET) нь дөрвөн терминал төхөөрөмж юм. Терминалууд нь эх (S), хаалга (G) болон ус зайлуулах (D). The субстрат or байгууллага дөрөв дэх терминалыг бүрдүүлнэ. MOSFET нь цахиурын диоксид диэлектрик бүхий сувгаас тусгаарлагдсан хаалгатай терминалаар баригдсан. MOSFETs нь бас байж болно хомсдол or сайжруулах горим. Бид эдгээр хоёр нэр томъёог удахгүй тодорхойлно.

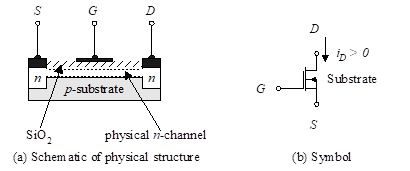

1 - н сувгийн хомсдол MOSFET зураг

MOSFETs нь заримдаа IGFETs (Insulated Gate Field-Effect Transistors) гэж нэрлэдэг2 давхарга болон хаалганы хооронд тусгаарлагч байдлаар ашиглагддаг. Бидний дүн шинжилгээ хийж дуусгавар болсон горимын MOSFET-тэй танилцаж эхэлнэ. БЖТ-ууд нэгэн адил байж болно npn or pnp, MOSFETs нь бас байж болно n-н суваг (NMOS) эсвэл pсуваг (PMOS). 1 зураг нь физик бүтэц ба тэмдэглэгээг харуулсан n- сувгийн хомсдол MOSFET. Суурь нь эх терминалтай холбогдсон гэдгийг санаарай. Энэ нь бараг л үргэлжлэх болно.

Хаягдлын MOSFET нь a бие махбодын суваг болон эх үүсвэрийн хоорондох суваг. Үүний үр дүнд, хүчдэл, vDS, ус зайлуулах ба эх үүсвэр, урсгал, iD, хаалгатай терминал G нь хоорондоо холбогдоогүй ч ус зайлуулах болон эх үүсвэрийн хооронд үүсдэг (vGS = 0 V).

Барилгын ажил n- сувгийн хомсдол MOSFET нь эхэлдэг p-Силикон цахиур. Нь n- нүхний эх үүсвэр ба ус зайлуулах цооног нь төгсгөлийн хоорондох бага эсэргүүцэл холболт үүсгэдэг n-н суваг, Зураг 1-д харуулсны дагуу. Цахиурын диоксидын нимгэн давхарга нь эх үүсвэр, ус зайлуулах суваг хоорондын талбайг хамардаг. SiO2 нь тусгаарлагч юм. Хөнгөн цагааны давхарга нь цахиурын диоксид тусгаарлагч дээр хадгалагдаж, хаалганы терминалыг үүсгэнэ. Үйл ажиллагаа нь сөрөг байна vGS сувгийн сувгуудаас цахилгааныг түлхэж, улмаар суваг шавхагдаж байна. Хэзээ vGS тодорхой хүчдэлд хүрдэг, VT, суваг нь хаагдсан. Эерэг утга vGS сувгийн хэмжээг нэмэгдүүлэх замаар ус зайлуулах урсгалыг нэмэгдүүлнэ. Хаягдлын MOSFET нь эерэг эсвэл сөрөг утгатай ажиллаж чаддаг vGS. Хаалга нь сувгаас тусгаарлагдсан тул хаалганы гүйдэл нь үл ялиг бага (10-ийн дарааллаар)-12 А).

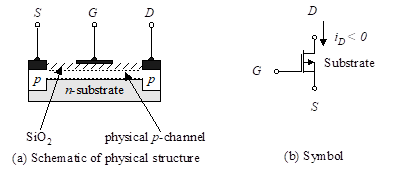

Зураг 2 - p сувгийн хомсдол MOSFET

Зураг 2 нь 1 Зурагтай харьцуулбал бид өөрчлөгдсөн байна n- сувгийн шавхалтын MOSFET рүү a p- сувгийн хомсдол MOSFET.

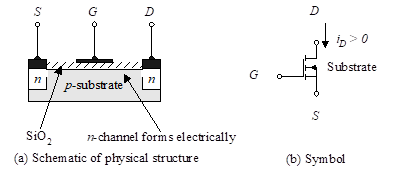

The nMOSFET-ийг 3 зураг дээр дүрс бичлэгийн хамт зургаар харуулав. Энэ нь хээрийн нөлөөтэй транзисторын хамгийн өргөн хэрэглэгддэг хэлбэр юм.

3 - н сувгийн сайжруулалт MOSFET зураг

The nMOSFET-ийн сайжруулалт MOSFET нь нимгэн MOSFET-ээс ялгаатай n-layer. Энэ нь суваг байгуулахын тулд хаалга болон эх үүсвэрийн хооронд эерэг хүчдэл шаарддаг. Энэ суваг нь хаалга-to-эх хүчдэлийн эерэг, vGS, энэ нь субстрат бүсээс электронуудыг татан авдаг n- ус зайлуулах суваг болон эх үүсвэр. Эерэг vGS исэлдлийн давхаргын дор гадаргуу дээр электронууд хуримтлагдах шалтгаан болдог. Хүчдэл нь босго түвшинд хүрэхэд, VT, хангалттай тооны электронууд энэ бүсэд татагдан орж байгаа бөгөөд үүнийг хийхтэй адил үүрэг гүйцэтгэдэг n-суваг. Ус зайлуулах хоолойд ямар ч iD хүртэл байна vGS хэтэрсэн байна VT.

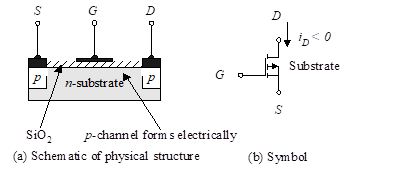

Зураг 4 нь 3 Зурагтай харьцуулбал бид өөрчлөгдсөн байна n- сувагыг сайжруулах MOSFET рүү a p- суваг сайжруулах MOSFET.

Зураг 4 - p сувгийн сайжруулалт MOSFET

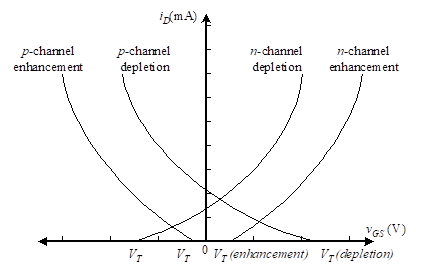

Дүгнэж хэлэхэд MOSFET-ийн гэр бүл таних тэмдэгийг харуулдаг iD эсрэг vGS Зураг 5 дээр харуулсан муруйнууд. Чанарын муруй бүрийг зайлуулах эх үүсвэрийн хүчдэлээр боловсруулдаг vDS төхөөрөмжийг хэвийн ажиллах үйлдлийн бүсэд байлгахын тулд iD эсрэг vDS муруйнууд. Дараагийн хэсгүүдийн хэлэлцүүлэг босго хүчийг тодорхойлно VT MOSFETs ба шавхалтын MOSFETs-ийг сайжруулах.

Зураг 5 - iD эсрэг vGS MOSFET бүлгийн шинж чанарууд нь хангалттай ус зайлуулах эх үүсвэрийн хүчдэл VDS

2.1 сайжруулалт-горимын MOSFET терминалын онцлогууд

MOSFET-ийн үндсэн бүтэц, үйл ажиллагааны үндэс суурийг танилцуулсан тул сайжруулалтын горимын төхөөрөмжийн төгсгөлийн зан үйлийг шалгах арга замыг ашиглаж байна. Эхлээд Зураг 1-ээс зарим ерөнхий ажиглалтыг хийцгээе. MOSFET дахь гүйдлийн хэвийн урсгалыг ус зайлуулах хоолойноос эх үүсвэр рүү чиглүүлж байна гэж бодъё (яг л BJT-тэй адил коллектор ба ялгаруулагчийн хооронд байна). Үүнтэй адил npn BJT, хоёр back-to-back diodes нь ус зайлуулах болон эх үүсвэрийн хооронд байдаг. Тиймээс урсгал болон эх үүсвэрийн хооронд урсах урсгалыг зөвшөөрөхийн тулд гадаад хүчдэлийг хаалга руу ажиллуулах ёстой.

Хэрвээ эх үүсвэрийг холбож, эерэг хүчдэлийг хаалган дээр байрлуулбал хүчдэл нь хаалга-эх үүсвэрийн хүчдэл юм. Эерэг хаалганы эерэг хүчдэл электроныг татдаг ба цоорхойг нөхдөг. Хүчдэл нь босго хэмжээнээс хэтэрсэн үедVT) хангалттай электронууд нь ус зайлуулах болон эх үүсвэрийн хооронд дамжих суваг үүсгэх сонирхолтой байдаг. Энэ үед транзистор эргэж, гүйдэл нь аль алиных нь функц юм vGS болон vDS. Энэ нь тодорхой байх ёстой VT нь эерэг тоо юм nсувагны төхөөрөмж болон сөрөг тоогоор pсуваг төхөөрөмж.

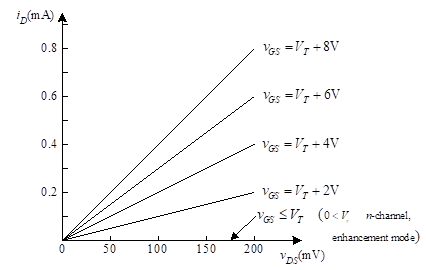

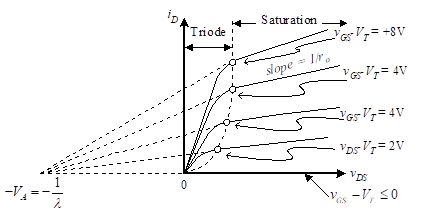

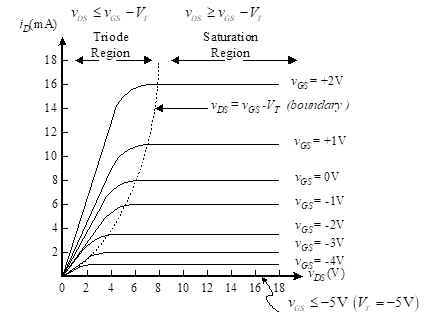

Нэг суваг бий болсон (өөрөөр хэлбэл, vGS >VT) урсгал ус зайлуулах ба эх үүсвэрийн хоорондох энэ суваг дээр урсгал урсаж болно. Энэ урсгал нь vDS, гэхдээ энэ нь бас хамааралтай байдаг vGS. Хэзээ vGS босоо хүчдэлийн хэмжээнээс арай доогуур байгаа тул маш бага урсгал гүйж чадна. Үүнд vGS босго хэмжээнээс цааш нэмэгдэж, суваг нь илүү олон тээвэрлэгч, илүү өндөр гүйдэлтэй байж болно. 6 зураг нь iD болон vDS хаана vGS параметр юм. Учир нь vGS босго хэмжээнээс бага, одоогийн урсгал байхгүй. Дээд тал нь vGS, харилцан хамаарал iD болон vDS MOSFET нь эсэргүүцэлтэй хамааралтай резистор шиг ажиллахыг харуулсан ойролцоогоор шугаман байна vGS.

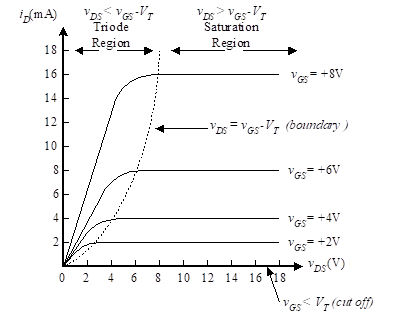

Зураг 6 -iD эсрэг vDS сайжруулах нэмэлт горимд зориулсан n- суваг MOSFET үед vDS бага байна

6-ийн муруй шулуун шугамууд шиг харагддаг. Гэсэн хэдий ч, тэдгээр нь шулуун шугамын дагуу үргэлжлэхгүй болно vDS том болж байна. Хаягдлын суваг үүсгэх эерэг хаалга хүчдэлийг ашигладаг гэдгийг санах хэрэгтэй. Энэ нь электроныг татах замаар хийдэг. Эерэг зайлуулах хүчдэл ижил зүйл хийж байна. Бид сувгийн суваг руу ойртох үед суваг үүсгэх хүчдэл бий болно vGS-vDS Учир нь хоёр эх үүсвэр бие биенээ эсэргүүцдэг. Энэ зөрүү нь бага байна VT, эх үүсвэр болон ус зайлуулах суваг хоорондох бүхэл бүтэн зайд суваг байхгүй болсон. Суваг нь хязгаарлагдмал ус зайлуулах төгсгөлд, цаашид улам нэмэгдэнэ vDS ямар ч өсөлтөд хүргэхгүй iD. Энэ нь хэвийн ажлын бүс юм уу эсвэл ханасан 7-р зурагт үзүүлсэн бүсэд шинж чанарын муруйн хэвтээ хэсэг. Ялгаа нь илүү байх үед VTгэж нэрлэдэг triode горим, учир нь гурван терминал дээр байгаа боломжууд нь одоогийн гүйдэлд хүчтэй нөлөө үзүүлдэг.

Өмнөх хэлэлцүүлэг нь 7-ийн үйлдлийн муруйд хүргэдэг.

Зураг 7 -iD эсрэг vGS өргөтгөл-горимын MOSFET-ийн хувьд

Туршилт ба хэвийн үйл ажиллагааны бүс хоорондын шилжилтийн (ханалтын бүс гэж нэрлэгддэг бөгөөд хавхлагтсан горимд ажиллах горим гэж нэрлэдэг) нь 7 зураг дээр тасалдсан шугамыг харуулсан болно.

![]()

(1)

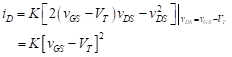

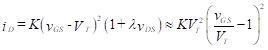

Гурвалжингийн хил орчимд муруйнуудын өвдөг холболт ойролцоогоор ойролцоогоор,

![]()

(2)

Тэгшитгэл (2), K нь өгсөн төхөөрөмжид тогтмол байна. Түүний үнэ цэнэ нь төхөөрөмжийн хэмжээ болон барилгын материалын хэмжээнээс хамаарна. Тогтмол нь,

![]()

(3)

Энэ тэгшитгэлд, μn Электроны хөдөлгөөнт байдал; Cоксид, оксид багтаамж нь хаалганы нэгж талбайд багтаамж; W хаалганы өргөн; L бол хаалганы урт юм. Тэгшитгэл нь хоорондох нарийн төвөгтэй, шугаман бус хамаарлыг илэрхийлнэ iD мөн хоёр хүчдэл, vDS болон vGS. Бид ус зайлуулах урсгалыг ойролцоогоор шугаман хамааралтайгаар өөрчлөхийг хүсч байна vGS (бие даасан vDS), FET нь triode бүсэд ерөнхийдөө ашиглагддаггүй.

Одоо бид ханасан бүсэд үйлдлийн муруйн тэгшитгэлийг олохыг хүсч байна. Шилжилтийн (өвдөг) тэгшитгэл (2) -ийг үнэлэх замаар triode болон ханасан бүсийн хооронд шилжилтийн үеийн утгыг тогтоож болно. Тэр бол,

(4)

Энэ томъёог хилийн шугам дээр (8 зураг дээр тасарсан шугам) хэмжих чадамжийг хаалга-to-source хүчдэл vGS. Шаардлагатай бол бид шугаман факторыг нэмснээр тэжээлийн бүс дэх шинж чанарын муруйн налууг багасгана.

![]()

(5)

Тэгшитгэл (5) λ нь жижиг тогтмол (8 зураг дээр үзүүлсэн шинж чанарын муруйнуудын ойролцоо хэвтээ хэсгийн налуу). Энэ нь ихэвчлэн 0.001 (V-1). Дараа нь

![]()

(6)

Бидний өмнөх хэлэлцүүлэг нь NMOS транзистортой холбоотой. Бид одоо PMOS-д шаардлагатай өөрчлөлтүүдийг товч хэлэлцэнэ. PMOS-ийн хувьд vDS сөрөг байна. Түүнчлэн, PMOS-д сувгийг бий болгох, ![]() .

.

8 зураг - MOSFET транзисторын терминалын үзүүлэлт

NMOS транзисторын шинж чанаруудаас зөвхөн өөрчлөлтүүд (Зураг 7) нь хэвтээ тэнхлэг одоо -vDS оронд нь + vDS, болон параметрийн муруйлтууд нь гүйдлийн хүчдэл буурдаг тул NMOS транзисторыг нэмэгдүүлэхийн оронд өндөр гүйдэл гүйдэг. Одоогийн утгыг нэмэгдүүлэх муруй нь илүү сөрөг хүчдэлтэй хаалгатай тэнцүү байна. Хэзээ vGS > VT, транзистор нь таслагдах болно. PMOS-ийг сайжруулахын тулд, VT сөрөг, PMOS-ийн дутагдал, VT эерэг байна.

PMOS транзисторын хувьд triode region transition нь гүйдлийн тэгшитгэл нь NMOS-ийнхтэй адил байна. Тэр бол,

![]()

(7)

гэдгийг анхаарна уу vGS болон vDS хоѐр сөрөг байна. PMOS транзистор дахь ханалтын бүс тэгшитгэл нь NMOS-ийнхтэй ижил байна. Тэр бол,

(8)

гэдгийг анхаарна уу λ муруйн өөрчлөлтийн түвшингээс хойш PMOS транзисторуудад сөрөг байна![]() ) нь сөрөг байна.

) нь сөрөг байна.

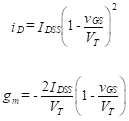

Харьцангуй тэгшитгэлийн хоёр талыг (6) фрагмын дериватив гарган авах vGS, ![]() Бид авдаг

Бид авдаг

![]()

(9)

Бидний үнэ цэнийг илүүд үздэг gm ялангуяа том дохионы хэлбэлзлийн хувьд тогтмол байх. Гэсэн хэдий ч бид FET-ийг жижиг сигналын програмууд ашиглахад л зөвхөн энэ нөхцөлийг ойролцоогоор гаргаж болно. Том дохионы нөхцөл байдлын хувьд долгионы хэлбэрийг гажуудуулж зарим аппликешнд хүлээн авах боломжгүй байдаг.

2.2 Хаягдал-Mode MOSFET

Өмнөх хэсэгт сайжруулалт-горимын MOSFET-тай холбоотой. Одоо бид үүнийг хоосон хоослох горимын MOSFET-тэй харьцуулдаг. Нь nсувгийн сайжруулсан горим, бид хаалганы эерэг хүчдэлийг ашиглах суваг олж авах. Энэ хүчдэл нь гар утасны сувагт хангалттай тооны хөдөлгөөнт электроныг хүчээр гаргах хангалттай том хэмжээтэй байх ёстой байсан.

9 зураг - Дуусах горим n-суваг MOSFET

Дахь n- MOSFET сувгийн хомсдолын горим, бид бие махбодийн хувьд суулгасан сувагтай тул энэ эерэг хүчдэл хэрэггүй болно. Энэ нь хаалган дээр сөрөг хүчдэлтэй байсан ч гэсэн ус зайлуулах хоолой ба эх үүсвэрийн терминалуудын хоорондох гүйдэлтэй байх боломжийг бидэнд олгоно. Мэдээжийн хэрэг, ус зайлуулах хоолой ба эх үүсвэрийн хоорондох урсгалтай хэвээр байх үед хаалган дээр гарч болзошгүй сөрөг хүчдэлийн хязгаарлалт байдаг. Энэ хязгаарыг босго хүчдэл гэж дахин тодорхойлов. VT. Сайжруулалтын горимоос гарсан өөрчлөлт бол хаалга-эх үүсвэрийн хүчдэл одоо Зураг 9-т үзүүлсэн шиг сөрөг эсвэл эерэг байж болно.

Хаягдлын горимын MOSFET-ийн ажиллагааг тодорхойлох тэгшитгэлүүд нь сайжруулах горимынхтай маш төстэй. Ус зайлуулах гүйдэлийн утга vGS тэг гэж тодорхойлсон IDSS. Үүнийг ихэвчлэн ус зайлуулах эх үүсвэрийн ханалтын гүйдэлэсвэл тэг хаалга зайлуулах гүйдэл. Сайжруулалтын горимын MOSFET-ийн тэгшитгэлийг хомсдолын горимтой харьцуулан олдог

![]()

(10)

Дараа нь бид,

(11)

Доройтох горим MOSFETs нь салангид хэлбэрээр байдаг, эсвэл тэдгээрийг интегрэйтийн горимын төрлүүдтэй хамт нэгдсэн схемд хуулж болно. Энэ нь хоёулаа багтдаг pтөрөл болон nтөрөл. Энэ нь хэлхээний дизайны техникийг илүү уян хатан болгодог.

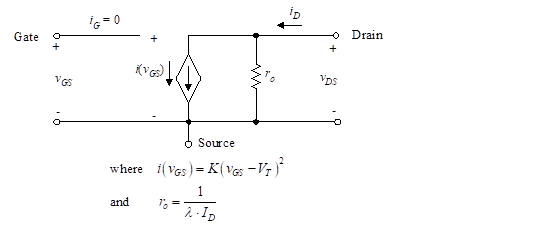

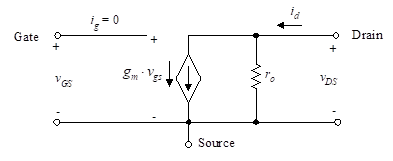

2.3 Том дохионы эквивалент хэлхээ

Бид одоо 8 [Тэгшитгэл (5) эсвэл (8) -н том дохионы шинж чанарыг хангаж буй бүс дэх эквивалент хэлхээг бий болгохыг хүсч байна. Дамжуулах гүйдэл, iD, хамаарна vGS болон vDS. Эх үүсвэрээс тогтмол хүчдэлийн хувьд бид зурагны параметрийн муруйн аль нэгний дагуу ажилладаг бөгөөд хамаарал нь ойролцоогоор шулуун шугам юм. Гүйдэл ба хүчдэлийн шулуун шугамын хамаарлыг резистороор загварчилдаг. Тиймээс эквивалент хэлхээ нь гүйдлийн эх үүсвэрийн утга нь ус зайлуулах гүйдлийн хэсгийг тогтоодог одоогийн эх үүсвэртэй зэрэгцээ эсэргүүцэлээс бүрдэнэ. vGS. Муруйн налуу нь хамаарна vGS. Налуу нь хэсэгчилсэн дериватив,

![]()

(12)

хаана r0 нь нэмэгдэл гаралтын эсэргүүцэл юм. Тэгшитгэл [(5) эсвэл (8)] - ээс бид энэ эсэргүүцлийг өгдөг

![]()

(13)

Бид хаана ч хэрэглэгддэг VGS эсэргүүцэл нь хаалга -аас-эх хүчдэлийн тодорхой тогтмол утгын хувьд тодорхойлогддог гэдгийг харуулах. Тэгшитгэл (13) -ийн эцсийн дүгнэлт λ бага байна. Тиймээс эсэргүүцэл нь хэвийсэн гүйдэлд урвуу хамааралтай, ID. Том дохионы эквивалент загварыг Зураг 11 дээр өгнө r0 тэгшитгэл (13) -д боловсруулагдсан болно.

Зураг 11 - Том дохионы эквивалент хэлхээ

2.4 MOSFET-ийн жижиг дохионы загвар

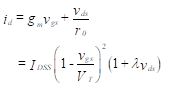

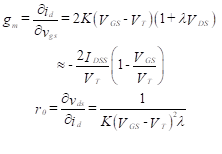

Бид одоо тэгшитгэлтэй холбоотой нэмэгдэл үр нөлөөг харахыг хүсч байна. Энэ тэгшитгэл дэх гурван хэлхээний параметрүүд, iD, vGS болон vDS нь хоёулангоос бүрддэг dc (хэвийсэн) ба ac бүрэлдэхүүн хэсгүүд (ингэснээр бид үсгэн тэмдэглэлүүдийг илэрхийлэлд хэрэглэсэн). Бид сонирхож байна ac жижиг дохионы загварт зориулсан бүрэлдэхүүн хэсэг. Дамжуулах гүйдэл нь хоёр хүчдэлээс, эх үүсвэрээс болон эх үүсвэрээс хамааралтай байгааг бид харж байна. Нэмэгдэл утгын хувьд бид энэ харилцааг бичиж болно

(14)

Тэгшитгэл (14) gm is форвард дамжуулалт болон r0 нь гаралтын эсэргүүцэл юм. Тэдний үнэ цэнэ нь тэгшитгэлд (HNUMX) хэсэгчилсэн дериватив хэрэглэснээр олддог. Тиймээс,

(15)

Тэгшитгэл (15) ойролцоолсон нь ажиглалтаас гарсан үр дүн юм λ жижиг бол Тэгшитгэл (14) Зураг 12-ийн жижиг дохионы загварт хүргэдэг.

12 зураг - Жижиг дохио MOSFET загвар

ӨНӨӨДӨР - 2. Металл оксидын хагас дамжуулагч FET (MOSFET)

ӨНӨӨДӨР - 2. Металл оксидын хагас дамжуулагч FET (MOSFET) PREVIOUS- 1. FET-ийн давуу болон сул талууд

PREVIOUS- 1. FET-ийн давуу болон сул талууд