8. FET өсгөгч - Canonical тохиргоо

FET өсгөгч - Canonical тохиргоо

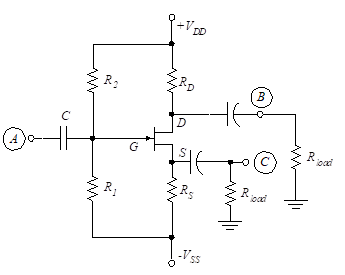

Зураг 31 - FET өсгөгч - ерөнхий тохиргоо

Зураг 31 нь FET өсгөгчний ерөнхий тохиргоог харуулж байна.

Энэ зурганд бид nJFET-ийн суваг, гэхдээ энэ нь эх сурвалжуудын тэмдэгээс хамааран бусад FET төхөөрөмжүүдэд тохирдог. Гаралт (ачаалал) нь Б цэг эсвэл В цэг дээр холбогдсон ба оролт нь А эсвэл С-д холбогддог.

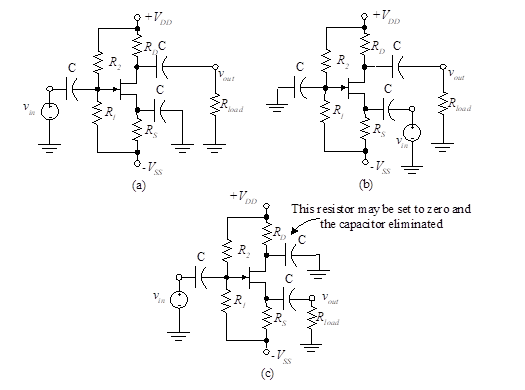

Нэг үе шаттай BJT өсгөгчийн дөрвөн үндсэн тохиргоотой байсан шиг ганц шаттай FET өсгөгчтэй дөрвөн тохиргоо байдаг. Эдгээр тохиргоонуудыг Зураг 32 дээр харуулав.

Зураг 32 (a) дээр бид ac JFET эх сурвалж терминалын замаас газрын зам. Гаралт нь ус зайлуулах ба газрын хооронд орших бөгөөд оролт нь хаалга ба газар хооронд байна. JFET эх үүсвэр терминал нь оролт, гаралтын аль алинд түгээмэл байдаг тул үүнийг a гэж нэрлэдэг нийтлэг эх сурвалж (CS) өсгөгч. Хэсэг 9.1-д энэ тохиргоо нь оролтын эсэргүүцэл ба өндөр хүчдэлийн ашиг өндөр боловч өндөр гаралтын эсэргүүцлийн зардлыг бий болгодог гэдгийг бид харах болно.

Хэрвээ JFET эх терминалын ба газрын хоорондох багтаамжийг 32 (a) зурагт хассан бол бид Эх үүсвэрийн резистор бүхий нийтлэг эх үүсвэрийн өсгөгч (эсвэл эх үүсвэрээс эсэргүүцэл өсгөгчийн). Энэ нь ялгаруулагч эсэргүүцэл бүхий CE өсгөгчтэй адил юм emitter-resistors өсгөгч).

Зураг 32 (b) дээр бид (ac) хаалганы терминалыг байрлуулж, гаралтаас газрын гадаргуу руу гарган авч, JFET эх үүсвэр терминал хүртэл газрын оролтыг оруулав.

Хаалга нь (ac) оролт болон гаралтын аль алиных нь хувьд нийтлэг байдаг нийтлэг хаалга (CG) өсгөгч. Хэсэг 9.2-д энэ тохиргоо нь өндөр хүчдэлийн ашиг, бага гаралтын эсэргүүцлийг хангаж өгдөг, гэхдээ бага оролтын эсэргүүцэлтэй холбоотой. Учир нь бага оролтын эсэргүүцэл, энэ тохиргооны ихэнхдээ эв нэгдэл (жишээ нь, дохио тусгаарлаж) ойр нь одоогийн ашиг нь одоогийн өсгөгчийн болгон ашиглаж байна.

Зураг 32 - FET нэг үе шаттай өсгөгч тохиргоо

Эцэст нь Зураг 32 (c) нь ус зайлуулах суваг дээр тохиргоог харуулсан (ac, хаалга руу хөрсний дохионы оролт, JFET эх үүсвэр терминалаас гаралт руу хөрвүүлнэ. Угаалтуур нийтлэг байдаг (ac) оролт болон гаралтын аль алины хувьд энэ нь нийтлэг зайлуулах (CD) тохиргоо. Өөрөөр хэлбэл үүнийг a гэж нэрлэдэг эх сурвалж follower (SF) үйл ажиллагаа явуулж байгаагаасаа болоод "9.3 CD (SF) өсгөгч" хэсэгт хүчдэлийн өсөлт нь гаралтын эсэргүүцэл ба оролтын эсэргүүцэл ихтэй эв нэгдэлтэй ойрхон байгааг бид харах болно. Тиймээс гаралт (JFET эх үүсвэрийн терминал) оролтыг "дагаж" явдаг бөгөөд энэ тохиргоог ихэвчлэн буфер болгон ашигладаг.

ӨНӨӨДӨР - 8. FET өсгөгч - Каноник тохиргоо

ӨНӨӨДӨР - 8. FET өсгөгч - Каноник тохиргоо PREVIOUS- 7. Компьютерийн симуляцид зориулсан FET загварууд

PREVIOUS- 7. Компьютерийн симуляцид зориулсан FET загварууд