4 ။ FET Amplifier Configuration နဲ့ဘက်လိုက်မှု

FET Amplifier Configuration နဲ့ဘက်လိုက်မှု

BJTs ၏ biasing အတှကျအသုံးပွုသောချဉ်းကပ်မှုကိုလည်း MOSFETS biasing အတှကျအသုံးပွုနိုငျသညျ။ ကျနော်တို့ဘက်ပေါင်းစုံ circuit ကိုချဲ့စက်များနှိုင်းယှဉ် discrete အစိတ်အပိုင်းအတွက်အသုံးပြုရှိသူများသို့ချဉ်းကပ်ခွဲခြားနိုင်ပါတယ်။ discrete အစိတ်အပိုင်းဒီဇိုင်းများတာ discrete အစိတ်အပိုင်း BJT ချဲ့စက်များကဲ့သို့တစ်ဦးချင်းစီအသံချဲ့စက်ဇာတ်စင်များအတွက် DC ဘက်လိုက်မှုခွဲထုတ်ဖို့ကြီးမားသောနားချင်းဆက်မှီနှင့်ရှောင်ကွင်း capacitors ကိုအသုံးပြုပါ။ ကြီးမားသော capacitors လက်တွေ့ကျတဲ့မဟုတ်ဘာဖြစ်လို့လဲဆိုတော့ IC MOSFET ချဲ့စက်များယေဘုယျအား coupled Direct နေကြသည်။ အဆိုပါ IC MOSFET ချဲ့စက်များပုံမှန်အားဖြင့် BJT IC ချဲ့စက်များအတွက်အသုံးပြုသူတို့အားအလားတူဖြစ်ကြောင်း DC ကလက်ရှိသတင်းရင်းမြစ်ကို အသုံးပြု. biased နေကြသည်။

4.1 ပြတ်-စိတျအပိုငျး MOSFET ဘက်လိုက်မှု

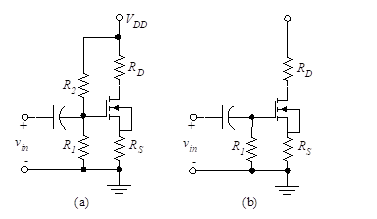

MOSFET ချဲ့စက်များများအတွက် biasing discrete-အစိတ်အပိုင်းပုံ 21 မှာပြထားတဲ့ဆားကစ်နှင့်အတူကုန်ပြီ။ မြို့တံခါးဝ-to-source ကိုဗို့ကြောင်းကို transistor configuration ကိုလိုအပ်မည်အကြောင်းအရာ circuit ကိုအမျိုးအစားကိုဆုံးဖြတ်သည်။ တစ်တိုးမြှင် mode ကို transistor များအတွက်အမြဲတမ်းတံခါးဝအပြုသဘောဆောင်ဗို့များအတွက်လိုအပ်ချက်ရှိရလိမ့်မည်။ အဆိုပါဗို့ဌာနခွဲဘက်လိုက်မှုအတွက်တစ်ဦးရှိပါလိမ့်မည် R1 နှင့် R2 အပြုသဘောဗို့အားရယူနိုင်ရန်အတွက်။ ကွယ်ပျောက်သွား MOSFETs သို့မဟုတ် JFETs အဘို့, R2 ပုံ 21 (ခ) မှာပြထားတဲ့အတိုင်းကနျ့သို့မဟုတ်အဆုံးမဲ့နိုင်ပါတယ်ဖြစ်စေ။

ပုံ ၂၁ - Amplifier ဘက်လိုက်မှုဖွဲ့စည်းမှုပုံ

ဘုံရင်းမြစ် (CS)- အ ac input ကိုမှာလျှောက်ထားတာဖြစ်ပါတယ် CG, အ ac output ကိုမှာယူဖြစ်ပါတယ် CDနှင့် CS တစ်ဦးချိတ်ဆက် dc ဗို့အားအရင်းအမြစ်သို့မဟုတ်မြေပြင်။ ဒါက BJT များအတွက်ဘုံ-ထုတ်လွှတ် configuration ကိုမှအလားတူပါပဲ။

-source resistors (SR) - အ ac input ကိုမှာလျှောက်ထားတာဖြစ်ပါတယ် CG, အ ac output ကိုမှာယူဖြစ်ပါတယ် CD နှင့် CS ချန်လှပ်ထားပါသည်။ ဒါက BJT များအတွက်ထုတ်လွှတ်-resistor configuration ကိုမှအလားတူပါပဲ။

-ဘုံဂိတ် (CG) - အ ac input ကိုမှာလျှောက်ထားတာဖြစ်ပါတယ် CS, အ ac output ကိုမှာယူဖြစ်ပါတယ် CD နှင့် CG တစ်ဦးချိတ်ဆက် dc ဗို့အားအရင်းအမြစ်သို့မဟုတ်မြေပြင်။ တစ်ခါတစ်ရံ CG configuration များအတွက်, CG ချန်လှပ်သည်မြို့တံခါးဝတစ်ဦးထံသို့တိုက်ရိုက်ချိတ်ဆက် dc ဗို့အားပေးဝေ။ ဒါကြောင့်ရံဖန်ရံခါဆားကစ်တွင်တွေ့မြင်ဖြစ်ပါတယ်ပေမယ့်အဆိုပါ CG, အ BJT များအတွက်ဘုံအခြေစိုက်စခန်း configuration ကိုမှအလားတူပါပဲ။

-source နောက်သို့လိုက်လော့ (SF) - အ ac input ကိုမှာလျှောက်ထားတာဖြစ်ပါတယ် CG, အ ac output ကိုမှာယူဖြစ်ပါတယ် CS နှင့်ယိုစီးမှုတစ်ခုချိတ်ဆက်ဖြစ်စေဖြစ်ပါသည် dc ဗို့အားပေးဝေရေးကိုတိုက်ရိုက်သို့မဟုတ်မှတဆင့် CD။ ဤသည်တစ်ခါတစ်ရံတွင်ဘုံယိုစီးမှု (CD ကို) လို့ခေါ်တဲ့နှင့် BJT များအတွက်ထုတ်လွှတ်နောက်လိုက် configuration ကိုမှအလားတူဖြစ်ပါတယ်။

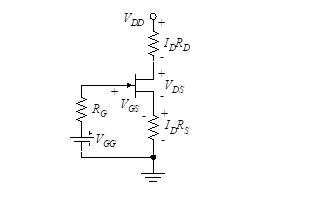

ပုံ 22 - Thevenin ညီမျှ circuit ကို

ဤဖွဲ့စည်းမှုတစ်ခုချင်းစီကိုအပိုင်း ၉၊“ FET Amplifier analysis” တွင်အသေးစိတ်လေ့လာထားသည်။

မတူညီသော configurations သာ capacitors မှတဆင့်မိမိတို့၏ဆက်သွယ်မှုအတွက်ကွဲပြားလျက်, capacitors မှပွင့်လင်းဆားကစ်တွေဟာကတည်းက dc voltages ကိုနှင့်ရေစီးကြောင်းကျနော်တို့လေ့လာလို့ရပါတယ် dc အထွေထွေအမှုအဘို့အဘက်လိုက်မှု။ အသံချဲ့စက်ဒီဇိုင်းအတွက်ကျနော်တို့ကို transistor (လည်းရွှဲတိုင်းဒေသကြီးသို့မဟုတ်ဖြစ်တော့-ချွတ် mode ကိုအဖြစ်ဖော်ထုတ်) ကိုတက်ကြွစွာလည်ပတ်မှုကဒေသတွင်းလည်ပတ်ချင်ဒါကြောင့်ကျနော်တို့က device များအတွက်ဖြစ်တော့-ချွတ် IV ဝိသေသယူဆ။ (ကျနော်တို့အမြဲတမ်းဒီဇိုင်းရဲ့အဆုံးမှာဒီယူဆချက်ကိုအတည်ပြုရန်သင့်ပါတယ်!)

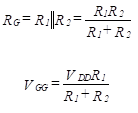

အဆိုပါဘက်လိုက်မှုခွဲခြမ်းစိတ်ဖြာရိုးရှင်းဖို့ကျနော်တို့ပုံ 22 မှာပြထားတဲ့အတိုင်းကို transistor တံခါးမှာ circuit ကိုပုံစံတစ်ခု Thevenin အရင်းအမြစ်ကိုသုံးပါ။

(24)

(biasing မဘို့ရာခန့်မှသုံးမသိသော variable တွေကိုရှိပါသည်ကတည်းကID, VGSနှင့် VDS), ကျနော်တို့သုံးယောက်လိုအပ်ပါတယ် dc ညီမျှခြင်း။ ပထမဦးစွာ dc မြို့တံခါးဝ-source ကိုကွင်းဆက်န်းကျင်ညီမျှခြင်းရေးသားခဲ့သူဖြစ်ပါတယ်။

![]()

(25)

တံခါးဝကလက်ရှိသုညဖြစ်ပါသည်ကတည်းကတစ်သုညဗို့အားကျဆင်းမှုကိုဖြတ်ပြီးရှိကွောငျးကိုသတိပွု RG။ တစ်စက္ကန့် dc ညီမျှခြင်းသည် drain-source loop ရှိ Kirchhoff ၏ law equation မှဖြစ်သည်။

![]()

(26)

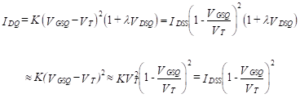

တတိယမြောက် dc အဆိုပါဘက်လိုက်မှုအမှတ်ညီမျှခြင်း (20) မှတွေ့ရှိခဲ့တာဖြစ်ပါတယ်တည်ထောင်ရန်လိုအပ်သည့် equation  အပိုင်း“ Junction field-effect transistor (JFET)" အရာကဒီမှာထပ်ခါတလဲလဲဖြစ်ပါတယ်။

အပိုင်း“ Junction field-effect transistor (JFET)" အရာကဒီမှာထပ်ခါတလဲလဲဖြစ်ပါတယ်။

(27)

| ပထမအကြမ်းဖျင်းလျှင်သက်ဆိုင်λVDS| << 1 (နီးပါးအမြဲတမ်းမှန်ကန်သော) နှင့်သိသိသာသာ coupled ညီမျှခြင်း၏ဖြေရှင်းချက်ရိုးရှင်း။

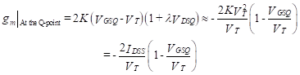

ကျနော်တို့များအတွက်ညီမျှခြင်းထည့်ထားနိုင်ပါတယ် gm [ညီမျှခြင်း (22)]

(22)

ဒီဇိုင်းအတွက်အသုံးဝင်သောသက်သေပြပါလိမ့်မယ်တဲ့အလားတူပုံစံသို့။

(28)

ညီမျှခြင်း (25) - (28) ကိုဘက်လိုက်မှုတည်ထောင်ရန်လုံလောက်သောဖြစ်ကြသည်။ discrete MOSFET ချဲ့စက်များအဘို့, ကျနော်တို့၏ဗဟိုမှာရှိတဲ့ Q-အမှတ်ထားရန်မလိုအပ်ပါဘူး ac ဝန်လိုင်းမှာကျွန်တော်မကြာခဏ BJT ဘက်လိုက်မှုအဘို့ပြုသကဲ့သို့။ discrete FET ချဲ့စက်များပုံမှန်အားဖြင့်မြင့်မား input ကိုခုခံ၏အားသာချက်ယူရန်အသံချဲ့စက်ကွင်းဆက်အတွက်ပထမအဆင့်အဖြစ်အသုံးပြုနေကြသည်ထားလို့ဖြစ်ပါတယ်။ တစ်ဦးပထမဦးဆုံးစင်မြင့်အဖြစ်အသုံးပြုသည့်အခါသို့မဟုတ် preamplifierသည်ဗို့အားအဆင့်ဆင့်ကျနော်တို့ကြီးမားတဲ့လေ့လာရေးခရီးကျော် preamplifier ၏ output ကိုမောင်းထုတ်ကြပါဘူးဒါကြောင့်သေးငယ်တဲ့ဖြစ်ကြသည်။

CURRENT - ၄

CURRENT - ၄ PREVIOUS- 3 ။ လမ်းဆုံကွင်းဆင်း-အကျိုးသက်ရောက်မှု Transistor (JFET)

PREVIOUS- 3 ။ လမ်းဆုံကွင်းဆင်း-အကျိုးသက်ရောက်မှု Transistor (JFET)