5 ။ MOSFET ပေါင်းစည်း Circuits

MOSFET ပေါင်းစည်း Circuits

MOSFET စစ္အနေနဲ့ပေါင်းစပ်ဆားကစ်၏တစ်စိတ်တစ်ပိုင်းအဖြစ်လုပ်ကြံသောအခါ, လက်တွေ့ကျတဲ့ထည့်သွင်းစဉ်းစား circuit ကို configurations နှစ်ခုအဓိကပြောင်းလဲမှုများကိုလိုအပ်သည်။ ပထမဦးစွာ discrete ချဲ့စက်များတွင်အသုံးပြုသည့်အကြီးစားနားချင်းဆက်မှီနှင့်ရှောင်ကွင်း capacitors လက်တွေ့ကျကျကြောင့်သေးငယ်တဲ့အရွယ်အစားဘက်ပေါင်းစုံဆားကစ်အတွက်လုပ်ကြံမရနိုင်ပါ။ ကျနော်တို့ကိုတိုက်ရိုက်-coupled ချဲ့စက်များ fabricating ဖွငျ့ဤချို့ယွင်းချက်န်းကျင်ရရှိမည်ဖြစ်သည်။

ဒုတိယအဓိကအပြောင်းအလဲကျနော်တို့အလွယ်တကူဘက်လိုက်မှု circuitry ၏တစ်စိတ်တစ်ပိုင်းအဖြစ်အသုံးပြုတဲ့ resistors လီဆယ်မရနိုငျသောကွောငျ့ဖွစျသညျ။ အဲဒီအစားကျနော်တို့တက်ကြွဝန်နှင့် MOS စစ္၏ဖွဲ့စည်းလက်ရှိသတင်းရင်းမြစ်ကိုအသုံးပြုပါ။

integrated circuits များ NMOS နှင့် PMOS circuitry နှစ်ဦးစလုံးကိုအသုံးပြုပါ။ NMOS ပုံမှန်အားပိုမိုမြင့်မားသိပ်သည်းဆ ICS (chip ကိုတစ်ဦးလျှင်ဆိုလိုသည်မှာပိုမိုလုပ်ဆောင်ချက်များကို) အတွက်အသုံးပြုနေစဉ် CMOS, ဒစ်ဂျစ်တယ် circuitry ပိုမိုဘုံဖြစ်ပါတယ်။

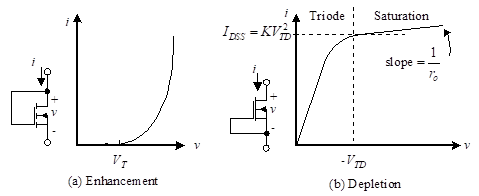

တက်ကြွဝန် Simulating ဟာ MOS ဝိသေသခါးဆစ်၏ဆင်ခြေလျှော၏အားသာချက်ကြာပါသည်။ ပုံ 23 တက်ကြွဝန်နှစ်မျိုးပြသထားတယ်။ 23 (ခ) တစ်ဦး NMOS လျော့ကျဝန်ကိုပြသနေစဉ်ပုံ 23 (က) တှငျကြှနျုပျတို့တစ်ခု NMOS တိုးမြှင့်ဝန်ကိုပြ။ ဒါ့အပြင်သက်ဆိုင်ရာဝိသေသခါးဆစ်ပုံ၌ရှိကြ၏ပြ။

ပုံ 23 - Active ကိုဝန်

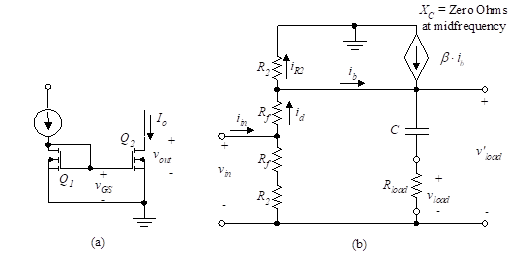

အဆိုပါ NMOS တိုးမြှင့်ဝန်များအတွက်ဗို့အားနှင့်လက်ရှိအကြားဆက်ဆံရေးအားဖြင့်ပေးထား

![]()

(29)

ဤဖွဲ့စည်းမှုပုံစံနှင့်ညီမျှခုခံ 1 ဖြစ်ပါသည် /gmအဘယ်မှာရှိ transconductance ၏တန်ဖိုးသည်ဘက်လိုက်မှုအမှတ်မှာသက်ဆိုင်သောအရာဖြစ်ပါသည်။

အဆိုပါ NMOS လျော့ကျဝန်အောက်ပါညီမျှခြင်းများကပေးသောဝိသေသ၏ဆင်ခြေလျှောကဆုံးဖြတ်ထားတဲ့အနေနဲ့ညီမျှခုခံရှိပါတယ်

(30)

MOSFET integrated circuits ၏ 5.1 ဘက်လိုက်မှု

ယခုငါတို့တက်ကြွဝန်တူအောင်ဖန်တီးနှစ်ခုနည်းစနစ်ရှိသည်, ကျနော်တို့ဘက်လိုက်မှုပြဿနာကိုဖြေရှင်းရန်နိုင်ပါတယ်။ ကျနော်တို့တိုက်နယ် configurations မဆိုအတွက်ဝန်ခုခံ၏အရပျ၌တက်ကြွစွာဝန်ကိုအသုံးပြုပါ။ ထိုအကိုခွဲခြားစိတ်ဖြာများအတွက် technique ကိုပြသနိုင်ဖို့, ပုံ 24 မှာပြထားတဲ့အတိုင်းကျွန်တော်တို့ကိုတစ်ခုတိုးမြှင့်ဝန်ကို အသုံးပြု. NMOS အသံချဲ့စက်ထည့်သွင်းစဉ်းစားကြကုန်အံ့။

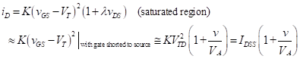

အဆိုပါကို transistor တံဆိပ်ကပ် Q2 အစားထိုး RD ကျွန်တော်တို့ရဲ့အစောပိုင်းတိုက်နယ်၏။ quiescent operating point ကိုဆုံးဖြတ်ရန်ကျွန်ုပ်တို့သည်ပုဒ်မ ၄ အရ“ FET Amplifier configurations and biasing” ပုဒ်မ ၄ တွင်ဖော်ပြထားသည့်နည်းစနစ်များကိုအသုံးပြုသည်။ ဆိုလိုသည်မှာကျွန်ုပ်တို့သည် load line အတွက်ညီမျှခြင်းနှင့်အတူ FET transistor ဝိသေသလက္ခဏာများကိုတစ်ပြိုင်နက်တည်းဖြေရှင်းရန်လိုအပ်သည်။ ပုံ ၂၅ မှာပြထားတဲ့အတိုင်းငါတို့အသေးစိတ်လုပ်နိုင်တယ်။

အဆိုပါ parametric ခါးဆစ်ဟာအသံချဲ့စက်ကို transistor, မေးများအတွက်ဝိသေသခါးဆစ်များမှာ1။ vs. တက်ကြွစွာဝန်၏လက်ရှိဝိသေသအဆိုပါဗို့အား, Q2 ပုံ 23 သူတို့ဖြစ်ကြသည်။ အဆိုပါ output ကိုဗို့အား, vထွက်, ခြားနားချက် VDD နှင့်တက်ကြွသောဝန်ဖြတ်ပြီးဗို့အား။ တက်ကြွစွာဝန်အတွက်လက်ရှိယင်းအသံချဲ့စက်ကို transistor အတွက်ယိုစီးမှုကလက်ရှိအတိုင်းအတူတူပင်ဖြစ်ပါသည်။ ထိုကြောင့်ငါတို့သည်ပုံ 23 ၏ဝိသေသများ၏ပြောင်းလဲမှန် image ကိုယူပြီးအားဖြင့်ဝန်လိုင်းတည်ဆောက်။ ၎င်း operating အမှတ်သင့်လျော်သောကို transistor ဝိသေသကွေးနှင့်အတူဤကွေး၏လမ်းဆုံဖြစ်ပါတယ်။ ကျနော်တို့ကွေးရွေးချယ်ဖို့ရာကို transistor ကိုသိရန်မြို့တံခါးဝ-to-source ကိုဗို့အားကိုရှာဖွေဖို့လိုအပ်ပါတယ်။ ကျနော်တို့လာမယ့်မြင်ရပါလိမ့်မည်သကဲ့သို့, input ကိုဘက်လိုက်မှုဗို့အားမကြာခဏတက်ကြွစွာလက်ရှိအရင်းအမြစ်ဖြင့်အစားထိုးသည်။

ပုံ 25 - ထို Q-အချက်အဘို့အ Graphical ဖြေရှင်းချက်

ယခုငါတို့အနေနဲ့တက်ကြွစွာဝန်တူအောင်ဖန်တီးဖို့ဘယ်လိုသိသော, ကျနော်တို့ input ကိုဘက်လိုက်မှု circuitry ၏တစ်စိတ်တစ်ဒေသအဖြစ်အသုံးပြုခံရဖို့တစ်ဦးကိုကိုးကားလက်ရှိ၏မျိုးဆက်မှကျွန်တော်တို့ရဲ့အာရုံကိုလှည့်။ ဤရွေ့ကားလက်ရှိသတင်းရင်းမြစ်ကျနော်တို့ BJT အသံချဲ့စက်ဘက်လိုက်မှုအဘို့ထိုသူတို့သုံးတာကအတူတူပင်လမ်းအတွက်အသုံးပြုကြသည်။

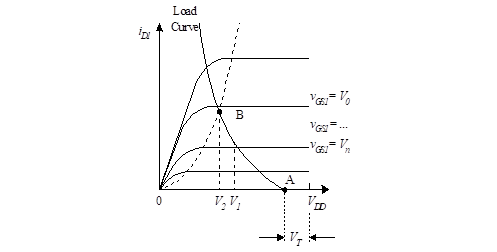

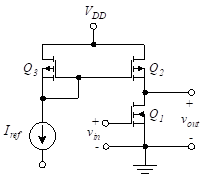

ပုံ 26 - လက်ရှိကြေးမုံ

ကျနော်တို့ MOSFET ခွဲခြမ်းစိတ်ဖြာ လက်ရှိကြေးမုံ။ တစ်ဦးကလက်ရှိကြေးမုံပုံ 26 မှာပြနေသည်။ နှစ်ခုစစ္ဿုံလိုက်ဖက်ခံရဖို့ယူဆနေကြသည်။ အဆိုပါ output ကိုလက်ရှိ၏ယိုစီးမှုကလက်ရှိဖြစ်ပါသည် Q2နှင့်ရည်ညွှန်းလက်ရှိ drives တွေကို Q1။ Transistor များသည်လုံး ၀ ကိုက်ညီပါက output current သည် reference current နှင့်တူညီလိမ့်မည်။ transistor များအပြိုင်ချိတ်ဆက်နေသောကြောင့်ဤသည်မှန်သည်။ ပုံ ၂၆ (ခ) တွင်ပြထားသကဲ့သို့ BJT current မှန်ကဲ့သို့ပင်ရည်ညွှန်းသော current ကိုရည်ညွှန်းခုခံမှုတစ်ခုအကြားရည်ညွှန်းဗို့အားအသုံးပြုခြင်းအားဖြင့်ထုတ်လုပ်နိုင်သည်။

ပုံ 27 ၏ CMOS အသံချဲ့စက်အတွက်ရလဒ်တွေကို (ဆိုလိုသည်မှာတက်ကြွစွာဝန်နှင့်ရည်ညွှန်းလက်ရှိ) အတူတကွအမျိုးမျိုးသော subcircuits ချပြီး။

ဒီအသံချဲ့စက်၏အမြတ်အားဖြင့်ပေးထား

![]()

(31)

ပုံ 27 - CMOS အသံချဲ့စက်

5.2 ခန္ဓာကိုယ် Effect

ကျွန်ုပ်တို့၏အပိုင်း“ ၂ ။ Metal-oxide semiconductor FET (MOSFET)” သည် MOSFET ၏အလွှာ (သို့မဟုတ်ကိုယ်ထည်) ကိုရည်ညွှန်းသည်။ ဤအလွှာသည်လမ်းကြောင်းကိုထူထောင်ရာတွင်အရေးပါသောအခန်းကဏ္ plays မှပါ ၀ င်သည်။ discrete MOSFETs များ၏လုပ်ဆောင်မှုတွင်ခန္ဓာကိုယ်သည် power source နှင့်မကြာခဏဆက်သွယ်လေ့ရှိသည်။ ထိုကဲ့သို့သောအခြေအနေများတွင်၊ အလွှာသည်စက်ပစ္စည်း၏လုပ်ဆောင်မှုအပေါ်တိုက်ရိုက်သက်ရောက်မှုမရှိပါ။ ဤအခန်း၏အစောပိုင်းကတီထွင်ခဲ့သောခါးဆစ်များသည်သက်ဆိုင်ပါသည်။

MOSFETs ဘက်ပေါင်းစုံဆားကစ်၏တစ်စိတ်တစ်ပိုင်းအဖြစ်လုပ်ကြံကြသောအခါအခြေအနေကပြောင်းလဲစေပါသည်။ ထိုကဲ့သို့သောကိစ္စရပ်များတွင်တစ်ဦးချင်းစီတဦးချင်းကို transistor ၏အလွှာသည်အခြားအလွှာထဲကနေခွဲထုတ်ခြင်းမရှိပါ။ အမှန်စင်စစ်တစ်အလွှာဟာမကြာခဏ chip ကိုအပေါ် MOSFETs တို့တှငျအမျှဝေသည်။ (ပစ္စုပ္ပန်လျှင်သို့မဟုတ်တစ်အနုတ်လက္ခဏာထောက်ပံ့ရေးရန်) NMOS ၌မြေပြင်ချိတ်ဆက်နေစဉ် PMOS IC မှာ shared အလွှာ, အများဆုံးအပြုသဘောအရင်းအမြစ် terminal ကိုချိတ်ဆက်ထားမည်ဖြစ်သည်။ ဒါဟာအရင်းအမြစ်နှင့်တစ်ဦးချင်းစီကို transistor ၏ခန္ဓာကိုယ်အကြားတစ်ဦးပြောင်းပြန်ဘက်လိုက်မှုတည်စေ။ ဒီပြောင်းပြန်ဘက်လိုက်မှု၏အကျိုးသက်ရောက်မှုဟာ operating ဝိသေသလက္ခဏာများကိုပြောင်းလဲရန်ဖြစ်သည်။ ဥပမာအားဖြင့်, တစ်ဦးအတွက် n-channel ကိရိယာကထိရောက်စွာ (တံခါးခုံကိုတိုးပွါးလာVT) ။ တံခါးခုံအပြောင်းအလဲများသောပမာဏကိုရုပ်ပိုင်းဆိုင်ရာ parameters တွေကိုနှင့် device ကိုဆောက်လုပ်ရေးပေါ်တွင်မူတည်သည်။ NMOS အဘို့, ဒီပြောင်းလဲမှုအားဖြင့် approximated နိုင်ပါသည်

![]()

(32)

ညီမျှခြင်း (32) ခုနှစ်, γအကြောင်းကို 0.3 နှင့် 1 (V ကိုအကြားကွဲပြားသော device ကို parameter သည်ဖြစ်ပါသည်-1 / 2). VSB အရင်းအမြစ် -to- ခန္ဓာကိုယ်ဗို့အားဖြစ်ပြီး, ဖြစ်ပါတယ် fermi အလားအလာ။ ဒါဟာပစ္စည်းအိမ်ခြံမြေဖြစ်ပြီး, ပုံမှန်တန်ဖိုးကိုဆီလီကွန်အဘို့အ 0.3 V ကိုဖြစ်ပါတယ်။

လက်ရှိ - ၅။ MOSFET ပေါင်းစည်းထားသောတိုက်နယ်များ

လက်ရှိ - ၅။ MOSFET ပေါင်းစည်းထားသောတိုက်နယ်များ PREVIOUS- 4 ။ FET Amplifier Configuration နဲ့ဘက်လိုက်မှု

PREVIOUS- 4 ။ FET Amplifier Configuration နဲ့ဘက်လိုက်မှု