Simulasi IBIS

Simulasi IBIS

Jump to TINA Main Page & General Information

Simulasi IBIS

IBIS (Spesifikasi Informasi Buffer Input / Output) adalah metode untuk memberikan informasi pemodelan tentang buffer input / output dari sirkuit terintegrasi. Hal yang baik tentang model IBIS adalah bahwa mereka sering tersedia bahkan untuk perangkat di mana model perangkat lengkap tidak tersedia dari produsen dengan alasan apa pun (misalnya, kompleksitas, perlindungan informasi hak milik, dll.).

Salah satu kegunaan model IBIS yang paling populer adalah Signal Integrity Analysis, termasuk pencocokan impedansi dan banyak lagi.

TINA saat ini mendukung versi IBIS 4.2 yang paling banyak digunakan.

Di TINA, Anda dapat mengonversi model IBIS ke TINA Spice makro dan kemudian menggunakannya di sirkuit apa pun di TINA. Anda juga dapat menyelesaikan model perangkat digital yang disederhanakan — mis., MCU dengan model IBIS — untuk lebih menggambarkan perilaku analog mereka.

Berikut ini, kami akan menunjukkan penggunaan model IBIS melalui contoh memperbaiki integritas sinyal antara Texas Instrument TMS320C6748 DSP dan ADS1259 delta-sigma ADC.

Pilih File / Impor / File IBIS (* .ibs), pilih c6748zce.ibs dari Direktori TINA >\ Contoh \ IBIS.

Dialog berikut akan ditampilkan. Dalam dialog ini, Anda dapat memilih model yang akan diimpor.

Sekarang pilih SPI1CLK_GP213 sinyal, model PBFZP18LL_X50_PI_3P3 (sel dioperasikan di 3.3V tanpa pullup atau pull-down), dan Typ nilai yang ditetapkan.

Tekan OK. Model IBIS secara otomatis dikonversi ke a Spice makro.

SPI1CLK_GP213 adalah sinyal clock serial konfigurasi master dari TMS320C6748 chip untuk mendorong input clock SPI dari konverter AD, Texas Instruments ADS1259.

Pilih File / Impor / File IBIS (* .ibs), pilih ads1259.ibs dari Direktori TINA >\ Contoh \ IBIS.

Dialog berikut akan ditampilkan. Dalam dialog ini, Anda dapat memilih model yang akan diimpor.

Sekarang pilih SCK sinyal input, model DIN_PD_3 dan max nilai (untuk rentang tegangan 3.3V DVDD).

Tekan OK. Model IBIS secara otomatis dikonversi ke a Spice makro.

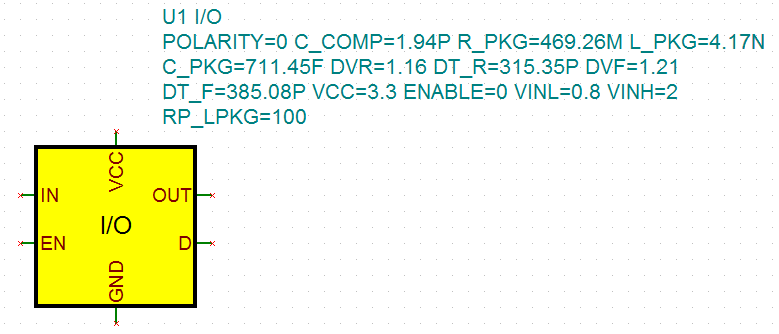

Hubungkan buffer I / O DSP ke input ADC dengan saluran transmisi lossless.

Tambahkan sumber daya dan generator tegangan untuk membuat sinyal clock sisi DSP. Tempatkan pin tegangan untuk simulasi ke node sinyal.

Kami menyesuaikan parameter saluran transmisi ke beberapa inci jejak mikrostrip yang diarahkan pada PCB empat lapis. Ini menghasilkan cc. 500ps delay dan impedansi karakteristik 90 Ohms.

File dari \ Contoh \ IBIS \ Pencocokan impedansi TMS320C6748.TSC siap digunakan.

Sekarang, klik Analisis, Sementara.

DSP mentransmisikan sinyal clock SPI di mana ketidakcocokan impedansi menciptakan refleksi. Hasilnya menunjukkan refleksi yang dibuat oleh ketidaksesuaian impedansi dalam simulasi rangkaian ini.

Pada sisi ADC (pin EoTL), tegangan berada di atas tanah dan tegangan suplai, yang melanggar nilai maksimum absolut dari input digital.

Untuk menghindari under dan overshoot pada ujung garis adalah mencocokkan impedansi output driver ke impedansi jejak dengan memasukkan resistor antara output dan jejak.

Mari kita tempatkan resistor 100 Ω secara seri sekarang dengan output.

Jalankan Analisis Sementara lagi, dan bandingkan hasilnya dengan menyalin kurva penting satu sama lain.

Sekarang, kita dapat melihat bahwa menggunakan model IBIS untuk memahami dan menemukan masalah kritis dengan simulasi membantu menyelesaikan masalah ini.