ИБИС Симулатион

ИБИС Симулатион

Jump to TINA Main Page & General Information

ИБИС Симулатион

ИБИС (Спецификација информација улазног / излазног пуфера) је метода за пружање информација о моделирању улазних / излазних бафера интегрираних кругова. Добра ствар код ИБИС модела је у томе што су они често доступни чак и за уређаје гдје комплетни модели уређаја нису доступни од произвођача из било којег разлога (нпр. Сложеност, заштита власничких информација, итд.).

Једна од најпопуларнијих употреба ИБИС модела је анализа интегритета сигнала, укључујући усклађивање импеданције и још много тога.

ТИНА тренутно подржава најраширенију верзију ИБИС КСНУМКС-а.

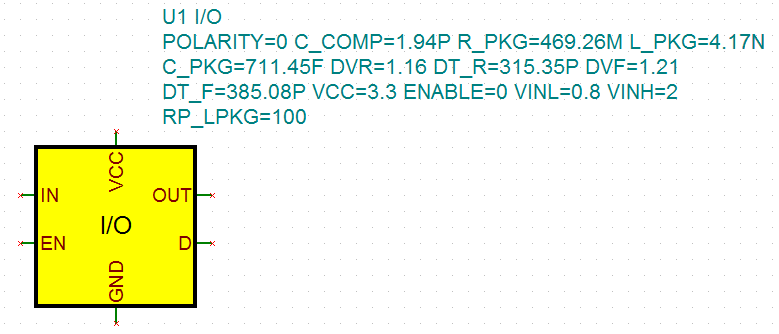

У ТИНА-и можете претворити ИБИС моделе у ТИНА Spice макрое и онда их користити у било којим круговима у ТИНА-и. Такође можете комплетирати поједностављене моделе дигиталних уређаја - нпр. МЦУ са ИБИС моделима - како би боље описали њихово аналогно понашање.

У наставку ћемо приказати употребу ИБИС модела кроз пример фиксирања интегритета сигнала између Текас Инструментс ТМСКСНУМКСЦКСНУМКС ДСП и АДСКСНУМКС делта-сигма АДЦ.

одабрати Датотека / Увоз / ИБИС датотека (* .ибс), изаберите цКСНУМКСзце.ибс од ТИНА дирецтори >Примери ИБИС.

Биће приказан следећи дијалог. У овом дијалогу можете одабрати модел за увоз.

Сада изаберите СПИКСНУМКСЦЛК_ГПКСНУМКС сигнал, ПБФЗПКСНУМКСЛЛ_КСКСНУМКС_ПИ_КСНУМКСПКСНУМКС модел (ћелија је радила на КСНУМКСВ без повлачења или падајућег) Тип валуе сет.

Притисните ОК. ИБИС модел се аутоматски конвертује у Spice макро.

СПИКСНУМКСЦЛК_ГПКСНУМКС је главни конфигурациони сигнал серијског такта ТМСКСНУМКСЦКСНУМКС чипа за погон СПИ тактног улаза АД конвертора, Текас Инструментс АДСКСНУМКС.

одабрати Датотека / Увоз / ИБИС датотека (* .ибс), изаберите адсКСНУМКС.ибс од ТИНА дирецтори >Примери ИБИС.

Биће приказан следећи дијалог. У овом дијалогу можете одабрати модел за увоз.

Сада изаберите СЦК улазни сигнал, ДИН_ПД_КСНУМКС модел и Макс валуе (за КСНУМКСВ ДВДД напонски опсег).

Притисните ОК. ИБИС модел се аутоматски конвертује у Spice макро.

Повежите ДСП И / О бафер са улазом АДЦ-а са преносном линијом без губитака.

Додајте извор напајања и генератор напона како бисте креирали сигнал сата са ДСП стране. Поставите пинове напона за симулацију на сигналне чворове.

Параметре трансмисионе линије подешавамо на неколико инча микротракастих трагова на четворослојном ПЦБ-у. Ово производи цц. КСНУМКСпс кашњење и КСНУМКС Охм карактеристична импеданса.

Филе фром \ Примери \ ИБИС \ Одговарајуће импеданце ТМСКСНУМКСЦКСНУМКС.ТСЦ је спреман за употребу.

Сада, кликните на Анализа, Трансиент.

ДСП преноси СПИ тактни сигнал гдје неусклађеност импеданције ствара рефлексије. Резултат показује рефлексије створене импеданцијским неусклађеностима у овој симулацији круга.

На АДЦ страни (пин ЕоТЛ), напон је изнад земље и напона напајања, што крши апсолутни максимални рејтинг дигиталног улаза.

Да би се избегли испод и надмашили крај линије треба да се усклади излазна импеданција драјвера са импедансом трага уметањем отпорника између излаза и трага.

Поставимо КСНУМКС Ω отпорник у серију сада са излазом.

Поново покрените Трансиент Аналисис и упоредите резултате тако што ћете копирати важне криве.

Сада можемо видјети да је кориштење ИБИС модела за разумијевање и проналажење критичних проблема са симулацијом помогло у рјешавању овог проблема.