8. Pembalik Amplifier

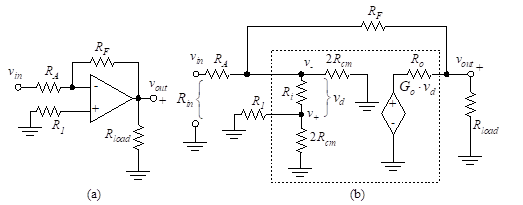

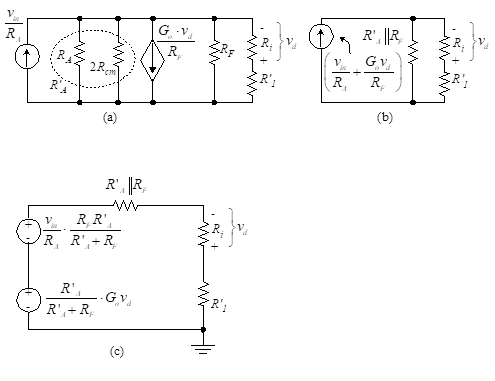

Gambar 36 (a) menggambarkan penguat pembalik. Gambar 36 (b) menunjukkan rangkaian ekivalen menggunakan model op-amp yang dikembangkan sebelumnya dalam bab ini.

Input dan Output Output 8.1

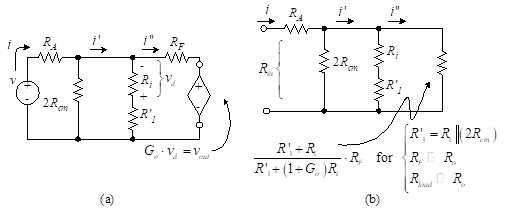

Gambar 36 (b) direduksi menjadi Gambar 37 (a) jika kita membiarkan, ![]()

Gambar 37 - Model penguat pembalik yang disederhanakan

Masuk akal untuk mengasumsikan bahwa ketidaksetaraan ini berlaku karena, jika tidak benar, output akan memuat input dan keuntungan akan berkurang.

Hubungan pembagi tegangan dapat digunakan untuk menghasilkan

(71)

dan persamaan loop menghasilkan

(72)

Resistansi input, Rin, diperoleh dari Gambar 37 (b), di mana kami telah mengganti sumber dependen dengan resistansi yang setara. Nilai dari resistor ini adalah v-/saya ” yang ditemukan dari Persamaan (72). Untuk yang besar G (yaitu, ![]() ), resistensi paling kanan pada Gambar 37 (b) adalah sekitar nol, dan

), resistensi paling kanan pada Gambar 37 (b) adalah sekitar nol, dan ![]() .

.

Resistansi keluaran dari penguat pembalik adalah sama dengan penguat non-pembalik. Demikian,

(73)

Penguatan Tegangan 8.2

Kami menggunakan sirkuit ekivalen pada Gambar 36 (b) dan Gambar 37 (a) untuk menentukan penguatan tegangan. Input input pembalik, A- = vdi luar/vin, diperoleh dari rangkaian Gambar 37 (a) dengan kembali membuat asumsi yang sama yang kami buat dalam menemukan resistansi keluaran.

Asumsi ini mengurangi rangkaian ke yang ditunjukkan pada Gambar 38 (a), di mana kami telah mengubah sumber tegangan secara seri dengan resistansi ke sumber arus secara paralel dengan resistansi. Resistor kemudian dapat digabungkan untuk menghasilkan rangkaian Gambar 38 (b). Akhirnya, sumber arus dikonversi kembali ke sumber tegangan untuk menghasilkan rangkaian yang disederhanakan dari Gambar 38 (c).

Persamaan loop untuk sirkuit ini diberikan oleh

(74)

Sejak vdi luar = Govd, keuntungan tegangan pembalik adalah

(75)

Gambar 38 (bagian a, b, c) - Membalik gain input

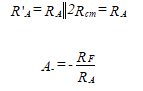

Kami dapat memverifikasi hasil ini relatif terhadap keuntungan dari op-amp ideal dengan membuat perkiraan: RA << 2Rcm dan G >> 1. Kemudian

(76)

Ini sama dengan hasil yang ditemukan sebelumnya untuk model yang disederhanakan.

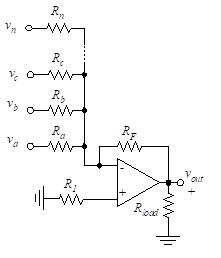

8.3 Multiple-Input Amplifier

(39)

Jika voltase va, vb,…, vm diterapkan ke persimpangan penjumlahan (membalikkan input ke op-amp) melalui resistor Ra, Rb, ..., Rm, masing-masing, seperti yang ditunjukkan pada Gambar 39, tegangan output adalah

(77)

Untuk mencapai keseimbangan bias, kami memilih

(78)

Mari kita definisikan

![]()

(79)

Resistansi keluaran kemudian

(80)

Misalkan sekarang hanya dua input yang digunakan. Tegangan output kemudian

(81)

Resistansi input pada va kira-kira sama dengan Ra, dan resistansi input pada vb adalah sekitar Rb. Kita dapat membuat sirkuit ini musim panas dua input satu-kesatuan-gain dengan tegangan output

(82)

dengan mengatur RF = Ra = Rb. Resistansi dari terminal input non-pembalik ke ground dipilih untuk mencapai keseimbangan bias. Demikian, R1 = RF/ 3, dan kami punya

(83)

Musim panas dua input sama-sama (yaitu, bukan kesatuan) diperoleh dengan menetapkan ![]() dan

dan ![]() . Dalam hal ini, tegangan output adalah

. Dalam hal ini, tegangan output adalah

(84)

Resistansi input kira-kira R. Sejak RA = R/ 2,

(85)

If m input dijumlahkan melalui resistor yang sama (katakanlah R), tegangan output

(86)

Untuk musim panas inverting multi-input dengan gain sama ini, resistansi input untuk setiap input adalah sekitar R. Sejak RA = R/m,

(87)

dan

(88)

Resistansi keluaran adalah

(89)

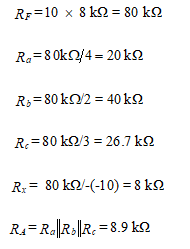

Contoh

Merancang dan menganalisis penguat pembalik input tiga menggunakan 741 op-amp mana

dan resistansi input Rmenit = 8 kΩ.

Larutan: Kami menggunakan metode desain Bab "Penguat Operasional Ideal" untuk menemukan X = 0, Y = 9, Z = -10.

Kemudian

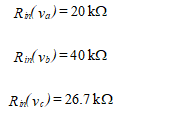

Pengganda gain penguat adalah 1 +RF/RA = 10. Kami menemukan resistansi input sebagai berikut:

Resistansi keluaran sekitar 75 (10) / 105 = 7.5 mΩ. Untuk mencapai keseimbangan bias, kami atur

SAAT INI - 8. Pembalik Amplifier

SAAT INI - 8. Pembalik Amplifier SEBELUMNYA- 7. Amplifier non-pembalik

SEBELUMNYA- 7. Amplifier non-pembalik