KHAI THÁC. Phân tích bộ khuếch đại FET

Phân tích bộ khuếch đại FET

9.1 Bộ khuếch đại CS (và điện trở nguồn)

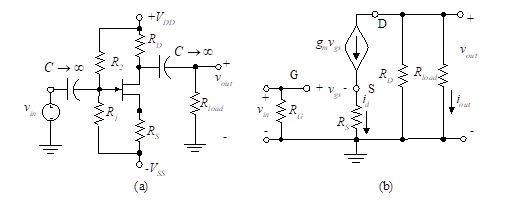

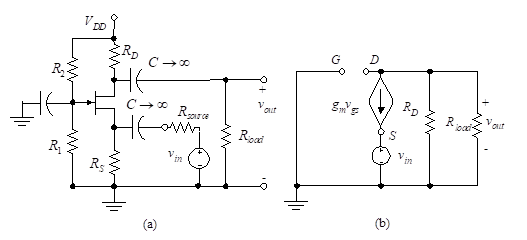

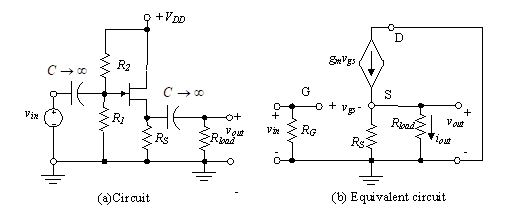

Hình 33 - Bộ khuếch đại CS với điện trở nguồn

Hình 33 (a) hiển thị bộ khuếch đại CS với điện trở nguồn. Các ac mạch tương đương nằm trong hình 33 (b). Chúng tôi giả sử ro là lớn so với, vì vậy nó có thể bị bỏ qua. Nếu một tụ điện có mặt giữa nguồn và mặt đất (tức là bộ khuếch đại CS), chúng ta chỉ cần đặt đơn giản RS bằng 0 trong các trường hợp sau ac phương trình. Chúng tôi làm điều này khi kết thúc sự phát sinh này.

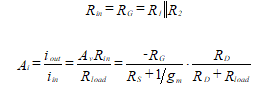

Trong phần (b) của Hình 33, RG là sự kết hợp song song của R1 và R2 và VGG là điện áp tương đương Thevenin của mạch phân cực:

(41)

(41)

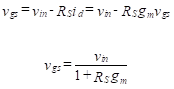

Để phân tích ac mạch tương đương, chúng ta viết một phương trình KVL xung quanh mạch cổng.

(42)

(42)

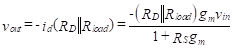

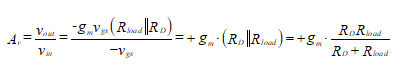

Điện áp đầu ra, vra, được đưa ra bởi

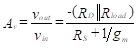

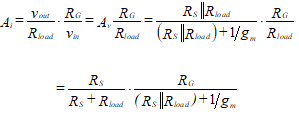

Độ tăng điện áp, Av, bây giờ được tìm thấy.

(43)

(43)

Nếu điện trở nguồn, RS, được bỏ qua bởi một tụ điện, chúng tôi cho RS = 0 và mức tăng điện áp tăng lên

![]() (44)

(44)

Đây thường là một số âm lớn.

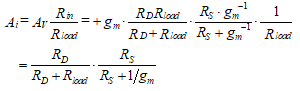

Điện trở đầu vào và mức tăng hiện tại được đưa ra bởi

(45)

(45)

9.2 Bộ khuếch đại CG

Hình 37 (a) hiển thị bộ khuếch đại cổng chung một giai đoạn và Hình 6.37 (b) hiển thị ac tương đương. Chúng tôi đã một lần nữa bỏ bê ro theo giả định rằng nó lớn so với sự kết hợp song song của RD với Rtải.

Hình 37 - Bộ khuếch đại CG

Từ vòng lặp 37 (b) ngoài cùng bên trái, điện áp cổng tới nguồn được cung cấp bởi

![]() (46)

(46)

Hiện tại thông qua RS is

(47)

(47)

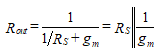

vì vậy điện trở (đầu vào) mà nguồn nhìn thấy là

![]() (48)

(48)

Điều này nên được so sánh với phương trình (45) cho bộ khuếch đại CS. Chúng ta thấy rằng nếu điện trở cổng cao, điện trở đầu vào của bộ khuếch đại nguồn chung có thể lớn hơn nhiều so với bộ khuếch đại cổng chung. Trong thực tế, số lượng ứng dụng của bộ khuếch đại CG bị hạn chế do trở kháng đầu vào thấp.

Độ tăng điện áp được cho bởi

(49)

(49)

So sánh điều này với phương trình (44), chúng ta thấy rằng mức tăng điện áp cho bộ khuếch đại CS với điện trở không vượt qua trong mạch nguồn giống như của bộ khuếch đại CG ngoại trừ bộ khuếch đại CG không làm dịch pha.

Điện trở đầu ra được đưa ra đơn giản bởi RD (đặt một dòng thử nghiệm và đo điện áp trong khi cài đặt vin về không).

Mức tăng hiện tại của bộ khuếch đại CG là

(50)

(50)

9.3 Bộ khuếch đại CD (SF)

Hình 39 (a) cho thấy bộ khuếch đại theo dõi nguồn thoát chung (SF) một giai đoạn và Hình 39 (b) hiển thị ac tương đương. Như với mỗi cấu hình chúng tôi đã phân tích, chúng tôi bỏ qua điện trở lớn, ro theo giả định, nó lớn hơn nhiều so với sự kết hợp song song của RS với Rtải.

Hình 39 - Bộ khuếch đại CD

Điện trở đầu vào đơn giản là Rin = RG. Viết một phương trình KVL vòng quanh cửa-to-nguồn, chúng tôi có

![]() (51)

(51)

từ đó chúng ta có được

![]() (52)

(52)

Điện áp đầu ra là

![]() (53)

(53)

Độ tăng điện áp là tỷ lệ đầu ra so với điện áp đầu vào.

![]() (54)

(54)

Lưu ý rằng mức tăng điện áp này nhỏ hơn thống nhất và nó tiếp cận với nhau như là sự kết hợp song song của RS với Rtải tăng.

Bây giờ chúng tôi tìm thấy mức tăng hiện tại. Dòng điện đầu ra là tỷ lệ của điện áp đầu ra với điện trở tải. Dòng điện đầu vào là điện áp đầu vào chia cho RG. Do đó, mức tăng được đưa ra bởi

(55)

(55)

Có thể tìm thấy điện trở đầu ra bằng cách thay thế điện trở tải bằng điện áp thử, vthử nghiệmvà sau đó tìm dòng điện kết quả, ithử nghiệm. Các hiện được thúc đẩy bởi nguồn thử nghiệm này được tìm thấy từ một phương trình nút tại nguồn.

![]() (56)

(56)

Điện áp cổng-nguồn chỉ đơn giản là -vthử nghiệm vì chúng ta giả sử điện áp đầu vào bằng không. Do đó, điện trở đầu ra là

(57)

(57)

HIỆN TẠI - 9. Phân tích Bộ khuếch đại FET

HIỆN TẠI - 9. Phân tích Bộ khuếch đại FET PREVIOUS- 8. Bộ khuếch đại FET - Cấu hình chuẩn

PREVIOUS- 8. Bộ khuếch đại FET - Cấu hình chuẩn