2. Метал-оксид полупроводнички FET (MOSFET)

Метал-оксид полупроводнички FET (MOSFET)

Полупроводничкиот метал-оксид полупроводник FET (MOSFET) е четири терминални уреди. Терминалите се извор (S), порта (G) одвод (D). на супстрат or тело го формира четвртиот терминал. MOSFET е конструиран со терминалот на портата изолиран од каналот со силикон диоксид диелектрик. МОСФЕТ може да биде или осиромашување or подобрување на владата. Накусо ги дефинираме овие два термина.

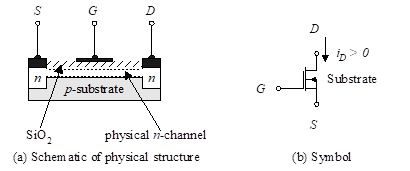

Слика 1 - n-channel осиромашен MOSFET

MOSFETs понекогаш се нарекуваат ИГФЕТ (Транзистори со полимер-ефект на изолирани порти) поради SiO2 слој кој се користи како изолатор помеѓу портата и подлогата. Ние ја започнуваме нашата анализа со MOSFET-от на осиромашување. Исто како и БЈТ npn or pnp, МОСФЕТ може да биде или nканал (NMOS) или pканал (PMOS). Слика 1 ја илустрира физичката структура и симболот за n-монење на канали MOSFET. Забележете дека подлогата е поврзана со изворниот терминал. Ова скоро секогаш ќе биде случај.

Намалувањето MOSFET е изграден со физички канал вметнат помеѓу каналот и изворот. Како резултат на тоа, кога напонот, vDS, се применува помеѓу одвод и извор, струја, iD, постои меѓу одводот и изворот, иако портата на портата G останува неповрзана (vGS = 0 V).

Изградбата на n- со MOSFET започнува со дефект на канал p-вршен силикон. На n- изворен извор и одвод на бунари формираат ниско-отпорни врски меѓу краевите на n-канал, како што е прикажано на Слика 1. Тенок слој на силициум диоксид се депонира за покривање на површината помеѓу изворот и одводот. На SiO2 е изолатор. Алуминиумски слој е нанесен на изолатор на силикон диоксид за да се формира терминалот на портата. Во работењето, негативно vGS турка електрони надвор од регионот на каналот, а со тоа го осиромашуваат каналот. Кога vGS достигнува одреден напон, VT, каналот е отсечени. Позитивни вредности на vGS зголемување на големината на каналот, што резултира со зголемување на струјата на мозоци. Намалувањето MOSFET може да работи со или позитивни или негативни вредности на vGS. Бидејќи портата е изолирана од каналот, струјата на портата е незначително мала (по редослед на 10-12 A).

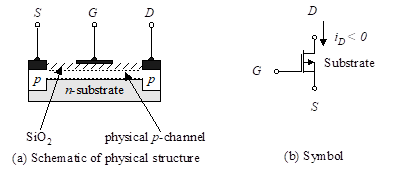

Слика 2 - MOSFET осиромашување на p-каналите

Слика 2 може да се спореди со Слика 1, освен што сме го смениле n-мастенија со MOSFET-офлајн канал p-монење на канали MOSFET.

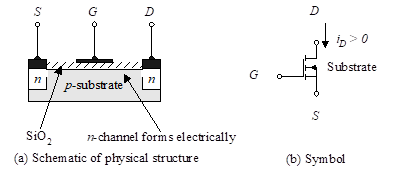

на n-канално подобрување MOSFET е илустрирано на Слика 3 заедно со симболот на колото. Ова е најчесто користената форма на транзистор со ефект на поле.

Слика 3 - n-канален MOSFET подобрување

на n-замена на канали MOSFET се разликува од MOSFET со осиромашување со тоа што нема тенки n-Слој. Потребен е позитивен напон помеѓу портата и изворот за да се воспостави канал. Овој канал е формиран со дејство на позитивен напон од порта до извор, vGS, која привлекува електрони од супстратниот регион помеѓу n- одводен мозоци и изворот. Позитивен vGS предизвикува електрони да се акумулираат на површината под оксидниот слој. Кога напонот достигнува праг, VT, во овој регион се привлекува доволен број на електрони за да се дејствува како диригент n-канал. Нема значителна струја на одвод, iD постои до vGS надминува VT.

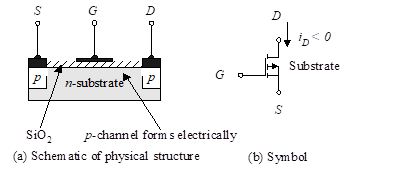

Слика 4 може да се спореди со Слика 3, освен што сме го смениле nMOSFET за подобрување на каналите на a p-канално подобрување MOSFET.

Слика 4 - п-канал за подобрување MOSFET

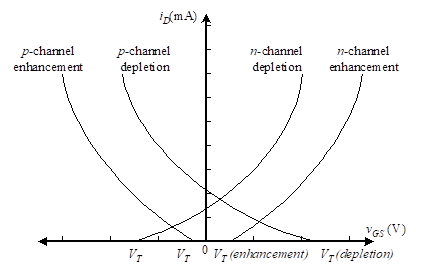

Како резиме, семејството MOSFET покажува идентификување iD наспроти vGS криви линии прикажани на слика 5. Секоја карактеристична крива се развива со доволен напон за одвод на извор vDS за одржување на уредот во нормалниот работен регион на iD наспроти vDS криви. Дискусијата во подоцнежните делови ќе го дефинира прагот на напонот VT и за MOSFETs за подобрување и за осиромашувањето на MOSFETs.

Слика 5 - iD наспроти vGS карактеристиките на семејството MOSFET за доволен извор на напон за одвод VDS

2.1 Можност за терминални карактеристики на МОСФЕТ

Сега, кога ја презентиравме основната структура и основа за работа на MOSFET, користиме пристап со цел да го испитаме терминалното однесување на уредот за режим на подобрување. Ајде прво да направиме некои општи набудувања од Слика 1. Помислете на нормалниот проток на струја во MOSFET од мозоци до изворот (исто како и во BJT, тоа е помеѓу колекторот и емитер). Како и со npn BJT, две диоди од назад кон назад постојат помеѓу одводот и изворот. Затоа, мораме да ги примениме надворешните напони на портата за да дозволиме струјата да тече помеѓу одводот и изворот.

Ако го израмниме изворот и примениме позитивен напон на портата, тој напон е всушност напон од порта до извор. Позитивниот портален напон привлекува електрони и ги отфрла дупките. Кога напонот го надминува прагот (VT), доволно електрони се привлечени да формираат спроводлив канал помеѓу одводот и изворот. Во овој момент, транзистор се вклучува и струјата е функција на двете vGS vDS. Треба да биде јасно тоа VT е позитивен број за n-канал уред, и негативен број за a p-канал уред.

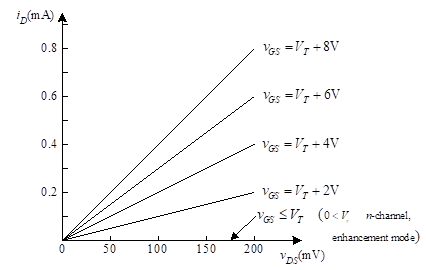

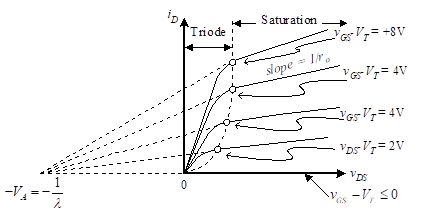

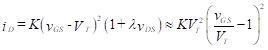

Откако ќе се креира канал (т.е., vGS >VT), тековниот проток може да се појави во тој канал помеѓу одводот и изворот. Овој тековен проток зависи од тоа vDS, но исто така зависи од тоа vGS. Кога vGS само едвај го надминува прагот на напонот, може да тече многу малку струја. Како vGS се зголемува надвор од прагот, каналот содржи повеќе носители и можни се повисоки струи. Слика 6 ја покажува врската помеѓу iD vDS каде vGS е параметар. Забележете тоа за vGS помалку од прагот, нема струја. За повисоко vGS, односот помеѓу iD vDS е приближно линеарен што укажува на тоа дека MOSFET се однесува како отпорник чиј отпор зависи од тоа vGS.

Слика 6 -iD наспроти vDS за режим на подобрување n-канален MOSFET кога vDS е мал

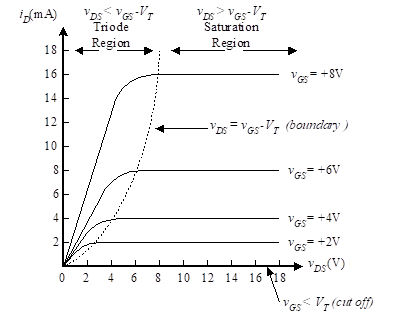

Кривите на Слика 6 изгледаат како прав линии. Сепак, тие нема да продолжат како вистински линии кога vDS станува поголем. Потсетете се дека позитивен портален напон се користи за создавање на канал за спроводливост. Тоа го прави со привлекување на електрони. Позитивниот одводен напон прави истото. Додека пристапуваме до крајниот дел на каналот, напонот што го создава каналот се приближува vGS-vDS бидејќи двата извори се спротивставуваат еден на друг. Кога оваа разлика е помала од VT, каналот повеќе не постои за целиот простор помеѓу изворот и мозокот. Каналот е ограничен на крајот на одводот, и понатаму се зголемува vDS не резултираат со никакво зголемување iD. Ова е познато како нормален оперативен регион или сатурација регионот прикажан на Слика 7 од хоризонталниот дел од карактеристичните кривини. Кога разликата е поголема од VT, ние го нарекуваме ова триода режим, бидејќи потенцијалите на сите три терминали силно влијаат на струјата.

Претходната дискусија доведува до оперативни криви на Слика 7.

Слика 7 -iD наспроти vGS за MOSFET за подобрување на владата

Транзицијата помеѓу триодата и нормалниот работен регион (наречена регион за сатурација и често идентификувана како работа во режимот на отчукување) е прикажана како испрекината линија на Слика 7, каде што

![]()

(1)

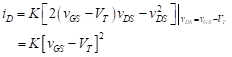

На границата со триодни региони, колената на кривите приближно ја следат врската,

![]()

(2)

Во равенката (2), K е константа за даден уред. Неговата вредност зависи од димензиите на уредот и од материјалите што се користат во неговата конструкција. Константата ја дава,

![]()

(3)

Во оваа равенка, μn е електронската мобилност; Cоксид, оксид капацитивност, е капацитетот по единица површина на портата; W е ширината на портата; L е должината на портата. Равенката укажува на комплицирана и нелинеарна врска меѓу iD и двата напони, vDS vGS. Бидејќи би сакале струја да се разликува приближно линеарно vGS (независно од vDS), ФЕТ генерално не се користи во триодниот регион.

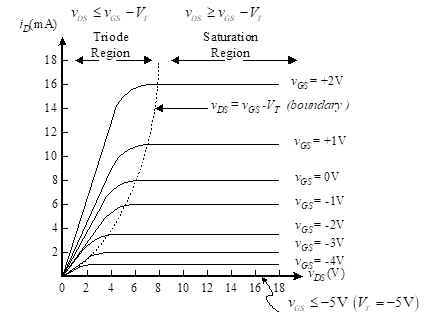

Сега сакаме да најдеме равенка за оперативните кривини во регионот на сатурација. Ние можеме да ги утврдиме вредностите на транзицијата помеѓу триодот и регионот на сатурација со евалуација на равенката (2) при транзицијата (коленото). Тоа е,

(4)

Оваа равенка ја воспоставува големината на струјата за одвод на границата (испрекината линија на Слика 8) како функција на напонот од портата до извор vGS. Доколку е неопходно, можеме да сметаме за мал наклон на карактеристичните кривини во регионот на заситеност со додавање на линеарен фактор.

![]()

(5)

Во равенката (5), λ е мала константа (наклонот на блискиот хоризонтален дел од карактеристичните кривини прикажани на Слика 8). Тоа е обично помалку од 0.001 (V-1). Потоа

![]()

(6)

Сите наши претходни дискусии се однесуваа на NMOS транзистор. Сега накратко разговараме за потребните модификации за PMOS. За PMOS, вредностите на vDS ќе биде негативен. Дополнително, за да се создаде канал во PMOS, ![]() .

.

Слика 8 - Терминални карактеристики на MOSFET транзистор

Единствените промени од карактеристиките на NMOS транзисторите (Слика 7) е дека хоризонталната оска е сега -vDS наместо на + vДС, и параметарските кривини претставуваат повисока струја на струја, бидејќи напонот на портата се намалува (наместо да се зголемува за NMOS транзистор). Кривите за зголемување на сегашните вредности одговараат на повеќе негативни портални напони. Кога vGS > VT, транзистор е пресечен. За подобрување на PMOS, VT е негативно, а за трошење ПМООС, VT е позитивно.

Равенката за струјата при транзицијата на триодниот регион за транзисторот PMOS е идентична со онаа на NMOS. Тоа е,

![]()

(7)

Имајте на ум дека vGS vDS се и негативни количини. Равенката за регионот на сатурација во PMOS транзистор е идентична со онаа на NMOS. Тоа е,

(8)

Имајте на ум дека λ е негативен за PMOS транзисторите од стапката на промена на кривата (![]() ) е негативен.

) е негативен.

Преземање на делумен дериват на двете страни на равенката (6) во однос на vGS, ![]() , добиваме

, добиваме

![]()

(9)

Ние претпочитаме вредноста на gm да биде константна, особено за големи сигнални промени. Сепак, ние можеме да ја приближиме оваа состојба само ако ги користиме ФЕТ за мали сигнални апликации. За големи сигнални услови, нарушувањето на форма на бранови може да биде неприфатливо во некои апликации.

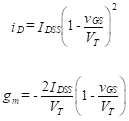

МОСФЕТ на режим на деплеција на 2.2

Претходниот дел се занимаваше со MOSFET за подобрување на владата. Ние сега го отсликуваме ова на MOSFET-от на деплеција. За n-канал подобрување на владата, да се здобијат со канал ние мораше да се применува позитивен напон на портата. Овој напон мораше да биде доволно голем за да предизвика доволен број мобилни електрони да создадат струја во индуцираниот канал.

Слика 9 - n-канален MOSFET режим на деплеција

Во n- режим на намалување на канал MOSFET, не ни треба овој позитивен напон бидејќи имаме физички вграден канал. Ова ни овозможува да имаме струја помеѓу терминалите за одвод и извор дури и со применети негативни напони на портата. Се разбира, постои ограничување на количината на негативен напон што може да се примени на портата додека сеуште има проток на струја помеѓу мозоци и извор. Оваа граница е повторно идентификувана како праг на напон, VT. Промената од режимот за подобрување е дека напонот од вратата до изворот сега може да биде или негативен или позитивен, како што е прикажано на слика 9.

Еднаквите кои ја дефинираат работата на MOSFET-овиот режим на модот се многу слични на оние на режимот за подобрување. Вредноста на мозоци кога vGS е нула е идентификувана како IДСС. Ова често се нарекува струја на сатурација на изворот, Или нула - струја на одвод на портата. Споредувајќи ги равенките на МОСФЕТ со подобрување на режимот со оние на режимот на исцрпување, наоѓаме

![]()

(10)

Потоа,

(11)

Режимот на деплеција MOSFET се достапни во дискретна форма, или тие можат да бидат фабрикувани на интегрираните кола чипови во право, заедно со начини на подобрување на режимот. Ова ги вклучува и двете pтип и nтип. Ова овозможува поголема флексибилност во техниките на дизајнирање на кола.

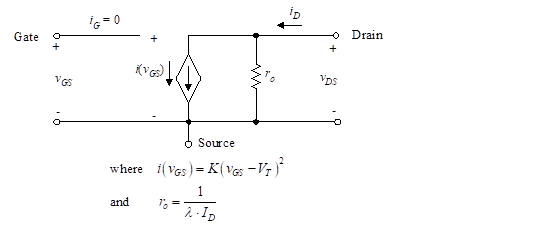

2.3 Еквивалентно коло со голем сигнал

Сега сакаме да развиеме еквивалентно коло кое ги претставува големи сигнални карактеристики на Слика 8 [равенка (5) или (8)] во регионот на заситеност. Имајте на ум дека тековната струја, iD, зависи од vGS vDS. За постојан напон од вратата до изворот, работиме по една од параметарските кривини на сликата, а врската е приближно права. Правата линија помеѓу струјата и напонот се моделира со отпорник. Еквивалентното коло се состои од отпорник паралелно со изворот на струја каде што вредноста на изворот на струја го воспоставува делот од струјата на одводот заради vGS. Наклонот на кривата зависи од тоа vGS. Наклонот е делумен дериват,

![]()

(12)

каде r0 е поединечниот излез отпор. Гледаме од равенката [(5) или (8)] дека овој отпор е даден од

![]()

(13)

каде што се користи горниот случај VGS за да се покаже дека отпорот е дефиниран за одредена константна вредност на напонот од порта до извор. Конечната апроксимација во равенката (13) произлегува од равенката (5) со претпоставка дека λ е мал. Отпорот е, според тоа, обратно пропорционален на струјата на пристрасност, ID. Големиот сигнален еквивалентен модел потоа е даден со Слика 11 каде r0 е развиен во равенката (13).

Слика 11 - еквивалентно коло со голем сигнал

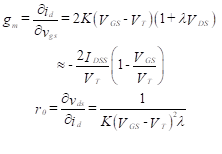

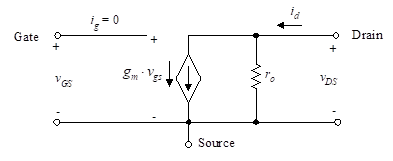

2.4 Мали-сигнален модел на MOSFET

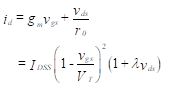

Сега сакаме да ги разгледаме постепените ефекти поврзани со равенката. Трите коло параметри во таа равенка, iD, vGS vDS се составени од двете dc (пристрасност) и ac компоненти (затоа сме користеле индекс на големи букви во изразите). Ние сме заинтересирани за ac компоненти за моделот со мал сигнал. Гледаме дека струјата на одводот зависи од две напони, портата до извор и одводот до извор. За поединечни вредности, оваа врска можеме да ја напишеме како

(14)

Во равенката (14), gm is напредна транспроводност r0 е излезен отпор. Нивните вредности се наоѓаат со земање на делумни деривати во равенката (5). Така,

(15)

Апроксимацијата во равенката (15) произлегува од набљудувањето дека λ ако е мал. Равенката (14) води до малиот сигнален модел на Слика 12.

Слика 12 - модел на мал сигнал MOSFET

АКТУЕЛНО - 2. Полупроводник на метал-оксид FET (MOSFET)

АКТУЕЛНО - 2. Полупроводник на метал-оксид FET (MOSFET) ПРЕТХОДНО-1. Предности и недостатоци на FETs

ПРЕТХОДНО-1. Предности и недостатоци на FETs