1. Диференцијални засилувачи

Диференцијални засилувачи

Повеќето оперативни засилувачи се состојат од серија на транзистори, отпорници и кондензатори кои формираат комплетен систем на еден чип. Засилувачите што се достапни денес се сигурни, мали, и трошат многу малку енергија.

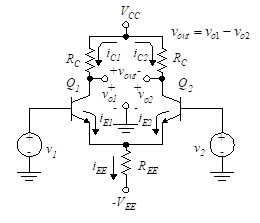

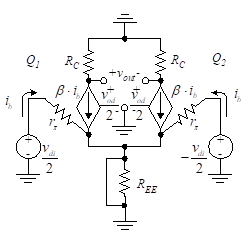

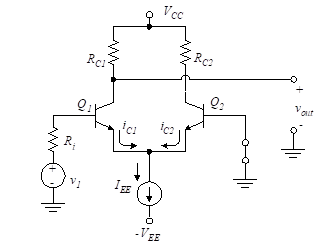

Влезната фаза на повеќето оп-засилувачи е Dзасилен засилувач како што е прикажано во неговата наједноставна форма на Слика 1.

Слика 1 - Диференцијален засилувач

Диференцијалниот засилувач е составен од два емитер-споени заеднички емитер dc засилувачи. Има два влеза, v1 v2, и три излези, vo1, vo2 vнадвор. Третиот излез, vнадвор, е разликата помеѓу vo1 vo2.

1.1 dc трансферни карактеристики

Диференцијалниот засилувач не работи линеарно со големи влезни сигнали. Со цел да се поедностави анализата претпоставуваме дека РЕ е голем, дека основниот отпор на секој транзистор е занемарлив и дека излезниот отпор на секој транзистор е голем. Имајте на ум дека ние користиме REE наместо RE во диференцијалниот засилувач бидејќи отпорот што се користи тука е голем и може да биде еквивалентен отпор на тековниот извор. Големата вредност на REE го задржува падот на напонот на емитерските отпорници речиси постојано.

Сега го решаваме ова коло за излезниот напон. Започнуваме со пишување на равенка на КВЛ околу базната јамка за кругот на Слика 1.

(1)

(2)

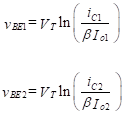

Треба да најдеме изрази за колекторските струи, iC1 iC2. Напоните на базниот емитер се дадени со равенката,

Во равенката (2) Io1 Io2 се обратните струи на сатурација за Q1 Q2 соодветно. Се претпоставува дека транзисторите се идентични. Комбинирање на равенки (1) и (2) приноси

(3)

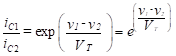

Решавачка равенка (3) за тековниот сооднос, наоѓаме,

(4)

Можеме да претпоставиме iC1 е приближно еднаква на iE1 iC2 е приближно еднаква на iE2. Затоа

(5)

Комбинирање на равенки (4) и (5), имаме

(6)

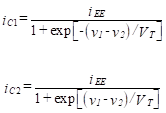

Имајте на ум дека

(7)

Важно набљудување може да се направи со гледање равенка (6). Ако v1 - v2 станува поголема од неколку стотици миливоли, колекторската струја во транзистор 2 станува мала и транзистор во основа е отсечен. Колорната струја во транзистор 1 е приближно еднаква на iEE, и овој транзистор е заситен. На колектор струи, а со тоа и на излезниот напон vнадвор, стануваат независни од разликата помеѓу двата влезните напони.

Линеарна засилување се јавува само за разлика од влезните напони помалку од приближно 100 mV. Со цел да се зголеми линеарен опсег на влезниот напон, може да се додадат мали емитерски отпорници.

1.2 Придобивки од општ режим и од диференцијален режим

Диференцијалниот засилувач има за цел да одговори само на разликата помеѓу двата влезните напони, v1 v2. Сепак, во практичен оп-засилувач излезот зависи од степен на збирот на овие влезови. На пример, ако двата влеза се еднакви, излезниот напон идеално би требало да биде нула, но во практичен засилувач тоа не е. Ние го означуваме случајот кога колото одговара на разликата како диференцијален режим. Ако два влеза се направени еднакви, ние велиме дека коло е во нејзината заеднички режим. Идеално би очекувале колото да произведе излез само во диференцијалниот режим.

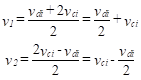

Секое две влезни напони, v1 v2, може да се реши во заеднички и диференцијален дел. Ние дефинираме две нови влезни напони на следниов начин:

(8)

На напонот, vdi, е диференцијален режим на влезниот напон и тоа е едноставно разликата помеѓу двата влезните напони. На напонот, vci, е вообичаен влезен напон, и тоа е просекот од двата влезните напони. Оригиналните влезни напони може да се изразат во смисла на овие нови количини како што следува:

(9)

Ако ги поставиме двата влезните напони еднакви, имаме

(10)

Бидејќи двата влеза се еднакви, напоните на емитер-базата се еднакви (ако транзисторите се идентични). Така, колекторските струи, исто така, мора да бидат идентични.

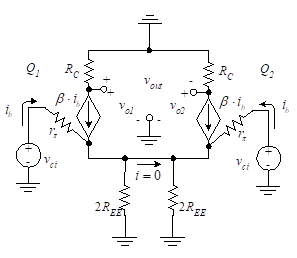

Слика 2 (а) Еквивалентно коло за засилувач со диференцијален режим

Сега гледаме еквивалентно коло за влезниот напон на диференцијалниот режим како што е прикажано на Слика 2 (а). Имајте на ум дека како струја во Q1 коло се зголемува, сегашната во Q2 коло намалува со иста стапка и амплитуда. Ова е точно од влезот на Q2 е еднаква на онаа на Q1 но 180o надвор од фаза. Така, напонот се менува REE е нула. Од ac сигнал на напон низ REE е нула, може да се замени со краток спој во ac еквивалентно коло. Имајте на ум дека поставување на напон на секоја транзистор база, кои се еднакви во амплитуда, но 180o надвор од фаза е еквивалентно на поставување на напон помеѓу двата транзисторски бази на двапати амплитудата. Напоните на vo1 vo2 се со еднаква амплитуда, но спротивната фаза и добивањето на диференцијалниот режим е

(11)

Оваа разлика во диференцијалниот режим е дефинирана во а единечен излез бидејќи се зема помеѓу еден колектор и земја. Ако излезот е направен помеѓу vo1 vo2, добивањето на диференцијалниот режим се нарекува a двоен завршен излез и е дадена од

(12)

Слична анализа може да се примени и на еквивалентното коло на обичен режим на слика 2 (б).

Слика 2 (b) Еквивалентно коло за засилувач во Common mode

Ако го делиме резисторот REE во два паралелни отпорници, секој од нив има двојно повеќе од оригиналниот отпор, можеме да го најдеме излезот со анализа на само половина од колото. Бидејќи транзисторите се идентични и вообичаените влезни напони се еднакви и во фаза, напоните низ 2REE отпорници се исти. Така, струјата помеѓу двата паралелни резистори прикажани е нула и ние треба само да погледнеме на едната страна од колото. Тогаш се добива напон за заеднички режим

(13)

Претпоставува равенка (13) REE е голем и re<<REE.

Ние го наоѓаме излезниот напон со двоен завршеток во однос на добивањето на заеднички режим и диференцијален режим на следниов начин:

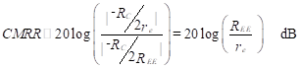

(14)

Пожелно е добивањето на диференцијалниот режим да биде многу поголемо од добивката на општ режим, така што засилувачот првенствено реагира на разликата помеѓу влезните напони. На заеднички режим на одбивање сооднос, CMRR, се дефинира како сооднос на степенот на добивање на диференцијален режим на добивка за заеднички режим. Тоа обично се изразува во дБ.

(15)

Ние сега се утврди влезот отпор на засилувачот и во диференцијален режим и во општ режим. За диференцијалниот режим, гледаме во засилувачот во основата на двата транзистори. Ова резултира со комплетно коло преку емитер на два транзистори, а влезниот отпор е

(16)

Сега за вообичаен влез, гледаме во засилувачот на Слика 2 (б). Така, влезниот отпор е

(17)

Овие резултати покажуваат дека влезниот отпор на заедничкиот режим е многу повисок од оној на диференцијалниот режим.

Нашата анализа на диференцијални засилувачи е базирана на BJT како транзисторски градежни блокови. FETs исто така може да се користат во диференцијални засилувачи со добиени предности на намалената влезна пристрасност и речиси бесконечна влезна импеданса. Анализата на диференцијалниот засилувач со користење на FETs се постигнува на ист начин како и анализата на BJT.

За диференцијалните засилувачи им требаат соодветни транзистори за да осигураат дека колото функционира правилно. Ако диференцијалниот засилувач е на интегрирано коло, овој дополнителен услов е помалку проблем бидејќи два транзистори се фабрикувани истовремено со користење на истиот материјал.

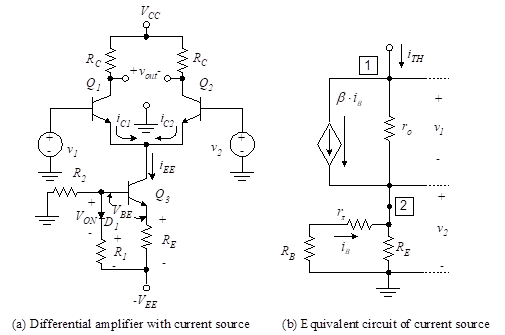

1.3 диференцијален засилувач со постојан извор на струја

Пожелно е да се направи REE колку што е можно поголем, за да се намали излезот на општ режим. Равенката покажува дека за да се направи големината на CMRR мора да се направи REE големи. Бидејќи големите отпори се тешки за производство на IC-чипови, бараме алтернативен пристап. Ова се постигнува со замена REE со dc тековен извор. Идеален извор на струја има бесконечна импеданса, па ја испитуваме можноста за замена REE со таков тековен извор. Слика 9.3 илустрира диференцијален засилувач каде што резисторот, REE, се заменува со извор на постојана струја.

(18)

Колку е поблиску изворот до идеалниот извор на постојана струја, толку е поголем односот за отфрлање вообичаен режим. Ние илустрираме диоден-компентиран фиксен пристрасен тековен извор. Надоместокот ја прави работата на колото помалку зависни од варијации на температурата. Диода D1 и транзистор Q3 се избрани така што имаат речиси идентични карактеристики во текот на опсегот на работните температури.

Со цел да се анализира колото на Слика 3 (а) и да се најде CMRR, ние треба да се одреди еквивалентен отпор, RTH (Thevenin еквивалент на константен струен извор). Еквивалентен отпор е даден од [види слика 3 (b)]

Пишувајќи KCL равенка во јазол 1, имаме

(19)

каде ro е внатрешниот отпор на транзисторот во наведената оперативна точка. Тоа е дадено од

(20)

Слика 3 - диференцијален засилувач со извор на постојана струја

ККЦ равенка на јазол 2 приноси

(21)

каде

(22)

Заменување v1 v2 во равенката на јазол 2, имаме

(23)

Конечно, отпорот на Тевенин е даден со замена на равенките (22) и (23) во равенка (18).

(24)

Сега ќе направиме низа претпоставки за значително поедноставување на овој израз. За да ја одржиме стабилноста на предрасудите, го користиме упатството за тоа

(25)

Заменувајќи ја оваа вредност од RB во равенка (24) и делење од β, ние имаме

(26)

Можеме да го поедноставиме овој израз со забележување

(27)

Ние тогаш имаме

(28)

Бидејќи вториот поим во оваа равенка е многу поголем од првиот, па можеме да го игнорираме RE да се добие

(29)

Оваа равенка може понатаму да се поедностави доколку постои следната состојба:

(30)

Во тој случај, имаме едноставен резултат

(31)

Оттука, ако сите приближувања се валидни, RTH е независна од β и неговата вредност е прилично голема.

1.4 диференцијален засилувач со еднократен влез и излез

Слика 4 покажува диференцијален засилувач каде вториот влез, v2, е поставена еднаква на нула и излезот се зема како vo1.

Ние користиме постојан тековен извор наместо REE, како што беше дискутирано во претходниот дел. Ова е познато како еднонасочен влезен и излезен засилувач со фазно пренасочување. Засилувачот се анализира со поставување v2 = 0 во претходните равенки. Диференцијалниот влез е едноставно

(32)

па излез е

(33)

Слика 4 - Еднократен влез со фазно пренасочување

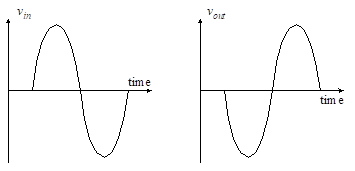

Знакот минус покажува дека овој засилувач покажува 180o фазно поместување помеѓу излезот и влезот. Типичен синусоидален влез и излез се илустрирани на Слика 5.

Слика 5 - Синусоидален влез и излез

Ако излезниот сигнал треба да се референцира на теренот, но фазата не се сака, излезот може да се земе од транзистор Q2.

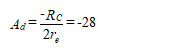

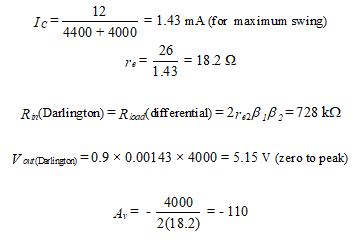

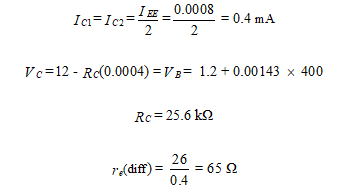

Пример 1 - диференцијален засилувач (анализа)

Пронајдете ја диференцијалната оптовареност на напонот, зголемувањето на напонот за заеднички режим и CMRR за колото прикажано на Слика 1. Да претпоставиме дека Ri = 0, RC = 5 kΩ, VEE = 15 V, VBE = 0.7 V, VT = 26 mV, и REE = 25 kΩ. Нека v2 = 0 и земете го излезот од vo2.

решение: Тековната преку REE се наоѓа во состојба на мирување. Од основата на Q2 е заземјен, напонот на емитер е VBE = 0.7 V, и

Натриската струја во секој транзистор е една половина од оваа сума.

Од

диференцијалното зголемување на напонот во секој транзистор е

Појавата на напон вообичаен режим е

Соодносот на отфрлање вообичаен режим потоа се дава од

ПРИМЕНА

Исто така, можете да ги извршите овие пресметки со симулатори на TINA или TINACloud коло, користејќи ја нивната преведувачка алатка со кликнување на линкот подолу.

1- Симулација на колор за диференцијални засилувачи

Пример 2

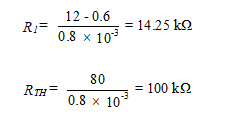

За диференцијалниот засилувач опишан во Пример 1, дизајнирајте го тековниот извор на фиксна-пристрасност со температурна компензација (Слика 3) за замена REE и да го одреди новиот CMRR за диференцијалниот засилувач, со ro = 105 kΩ, VBE = 0.7 V, и β = 100. Да претпоставиме R1 = R2.

решение: Ние ја поставуваме оперативната точка на транзисторот во средината на dc товарна линија.

Потоа, осврнувајќи се на тековниот извор на Слика 3 (а),

За стабилност на предрасудите,

Потоа

Од 0.1RE>>re (т.е. 1.25 kΩ >> 26 / 0.57 Ω), тогаш од равенката (31) имаме

CMRR е даден од

ПРИМЕНА

Исто така, можете да ги извршите овие пресметки со симулатори на TINA или TINACloud коло, користејќи ја нивната преведувачка алатка со кликнување на линкот подолу.

2- Симулација на колор за диференцијални засилувачи

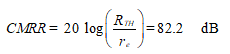

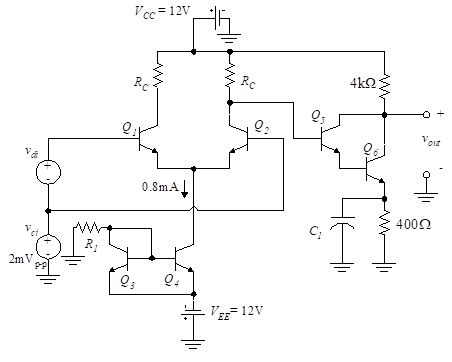

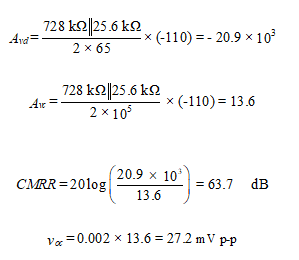

Пример 3

Дизајн на коло за постигнување на условите како што е наведено во Слика 6 за максимален излезен напон замав. Петте транзистори, Q1 до Q5, секој има β = 100 додека Q6 има β на 200. VBE е 0.6 V за сите транзистори, VT = 26 mV, и VA = 80 V. Претпостави дека сите транзистори се идентични.

Утврди,

(А) RC, R1, и CMRR.

(б) Излезен напон за заеднички режим.

(в) Излезен напон во диференцијален режим.

(г) Диференцијален режим влез напон vdi за максимално излез.

решение: Ќе го третираме коло во три дела:

- 1. Дарлингтонски засилувач.

- 2. Диференцијален засилувач

- 3. Едноставен тековен извор

Сега за вкупниот систем имаме

Диференцијалниот влез vdi неопходни за производство на максимално неискористен излез на напон

Исто така, можете да ги извршите овие пресметки со симулатори на TINA или TINACloud коло, користејќи ја нивната преведувачка алатка со кликнување на линкот подолу.

3- Симулација на колор за диференцијални засилувачи

АКТУЕЛНО - 1. Диференцијални засилувачи

АКТУЕЛНО - 1. Диференцијални засилувачи ПРЕТХОДНИ - практични оперативни засилувачи - вовед

ПРЕТХОДНИ - практични оперативни засилувачи - вовед